RT-Thread STM32F746-st-disco开发板BSP说明

RT-Thread STM32F746-st-disco开发板BSP说明

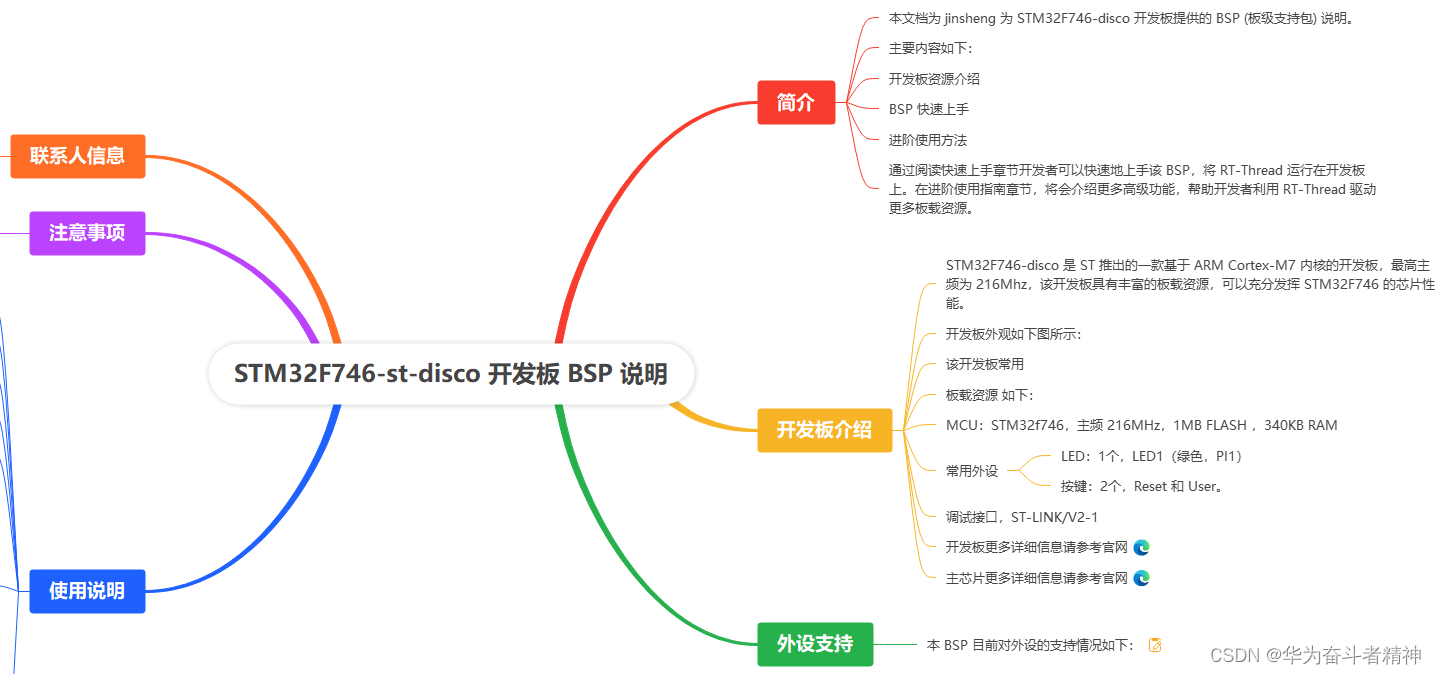

简介

本文档为 jinsheng 为 STM32F746-disco 开发板提供的 BSP (板级支持包) 说明。

主要内容如下:

- 开发板资源介绍

- BSP 快速上手

- 进阶使用方法

通过阅读快速上手章节开发者可以快速地上手该 BSP,将 RT-Thread 运行在开发板上。在进阶使用指南章节,将会介绍更多高级功能,帮助开发者利用 RT-Thread 驱动更多板载资源。

开发板介绍

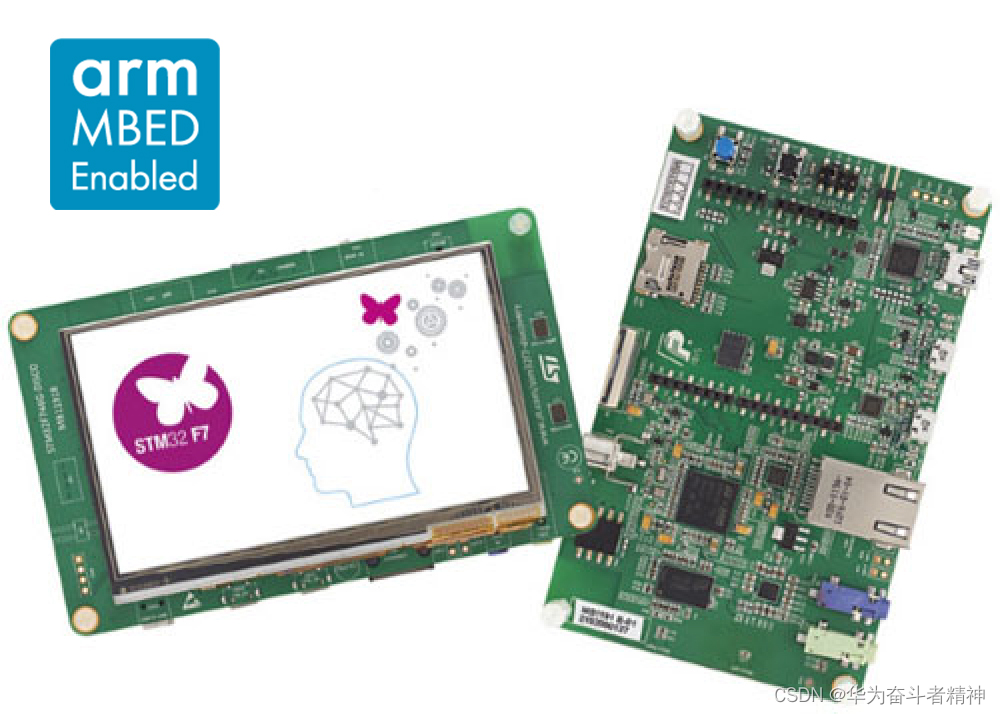

STM32F746-disco 是 ST 推出的一款基于 ARM Cortex-M7 内核的开发板,最高主频为 216Mhz,该开发板具有丰富的板载资源,可以充分发挥 STM32F746 的芯片性能。

开发板外观如下图所示:

该开发板常用 板载资源 如下:

- MCU:STM32f746,主频 216MHz,1MB FLASH ,340KB RAM

- 常用外设

- LED:1个,LED1(绿色,PI1)

- 按键:2个,Reset 和 User。

- 调试接口,ST-LINK/V2-1

开发板更多详细信息请参考官网 stm32f746-disco 开发板介绍。

主芯片更多详细信息请参考官网 stm32f746 芯片资料。

外设支持

本 BSP 目前对外设的支持情况如下:

| 板载外设 | 支持情况 | 备注 |

|---|---|---|

| USB 转串口 | 支持 | UART1 |

| QSPI Flash | 支持 | QSPI1 |

| 以太网 | 支持 | RMII |

| SDRAM | 支持 | SDRAM1 |

| SD卡 | 支持 | SD 4bits |

| 4.3寸电容屏 | 支持 | LTDC |

| MEMS麦克风 | 暂不支持 |

| 片上外设 | 支持情况 | 备注 |

|---|---|---|

| GPIO | 支持 | PA0, PA1… PK7 —> PIN: 0, 1…168 |

| UART | 支持 | UART1 |

| TIMER | 支持 | Timer11 |

| SPI | 暂不支持 | 即将支持 |

| QSPI | 支持 | QSPI1 |

| I2C | 暂不支持 | 即将支持 |

| FLASH | 支持 | |

| WDT | 支持 | |

| SDIO | 支持 | |

| USB Device | 暂不支持 | 即将支持 |

| USB Host | 暂不支持 | 即将支持 |

| SAI | 暂不支持 | 即将支持 |

使用说明

使用说明分为如下两个章节:

-

快速上手

本章节是为刚接触 RT-Thread 的新手准备的使用说明,遵循简单的步骤即可将 RT-Thread 操作系统运行在该开发板上,看到实验效果 。

-

进阶使用

本章节是为需要在 RT-Thread 操作系统上使用更多开发板资源的开发者准备的。通过使用 ENV 工具对 BSP 进行配置,可以开启更多板载资源,实现更多高级功能。

快速上手

本 BSP 为开发者提供 MDK4、MDK5 和 IAR 工程,并且支持 GCC 开发环境。下面以 MDK5 开发环境为例,介绍如何将系统运行起来。

硬件连接

使用数据线连接开发板到 PC,打开电源开关。

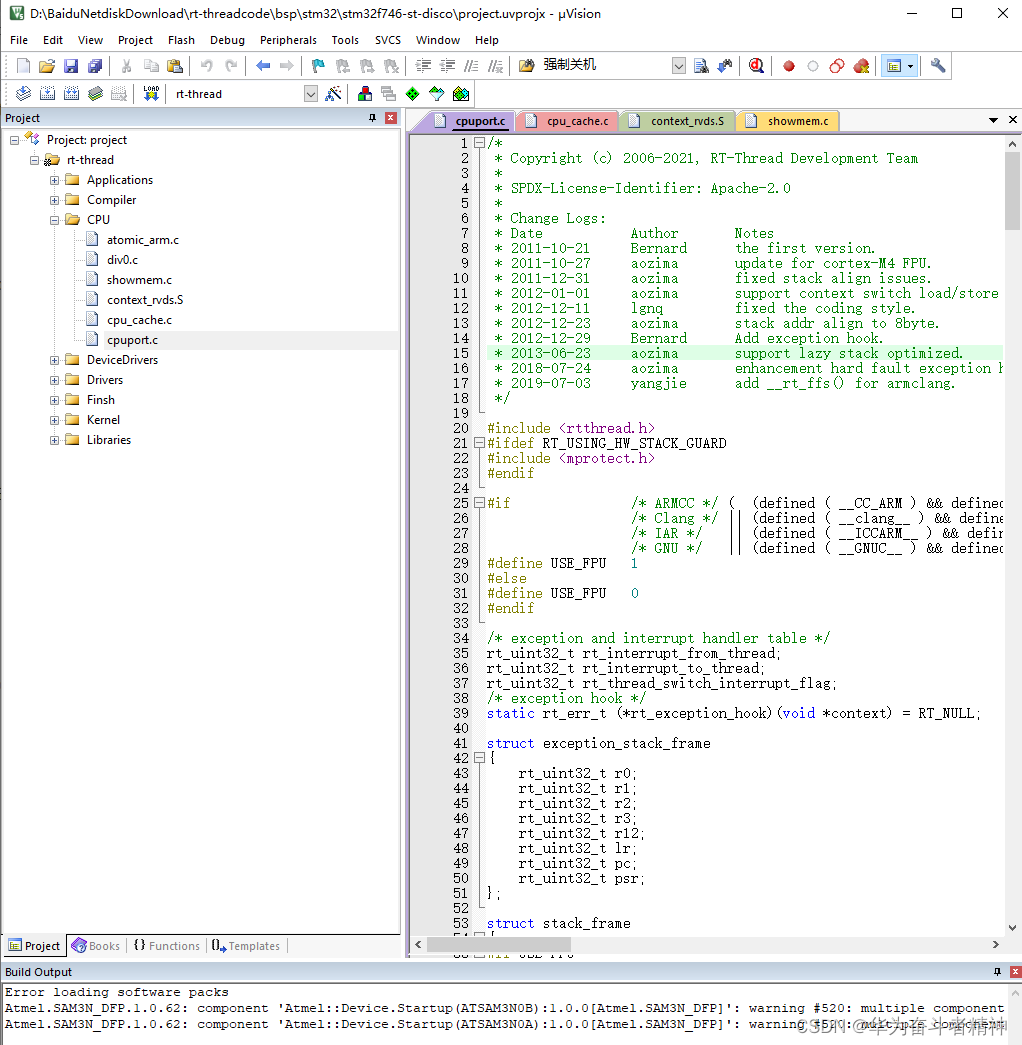

编译下载

双击 project.uvprojx 文件,打开 MDK5 工程,编译并下载程序到开发板。

工程默认配置使用 st-link 仿真器下载程序,在通过 st-link 连接开发板的基础上,点击下载按钮即可下载程序到开发板

运行结果

下载程序成功之后,LED 闪烁。

连接开发板对应串口到 PC ,在终端工具里打开相应的串口(115200-8-1-N),复位设备后,可以看到 RT-Thread 的输出信息:

\ | /

- RT - Thread Operating System

/ | \ 4.0.0 build Jan 30 2019

2006 - 2018 Copyright by rt-thread team

msh >

进阶使用

此 BSP 默认只开启了 GPIO 和 串口1 的功能,更多高级功能,需要利用 ENV 工具对 BSP 进行配置,步骤如下:

-

在 bsp 下打开 env 工具。

-

输入

menuconfig命令配置工程,配置好之后保存退出。 -

输入

pkgs --update命令更新软件包。 -

输入

scons --target=mdk4/mdk5/iar命令重新生成工程。

本章节更多详细的介绍请参考 STM32 系列 BSP 外设驱动使用教程。

注意事项

暂无

示例代码

…\libcpu\arm\cortex-m7\cpuport.c

#include <rtthread.h>

#ifdef RT_USING_HW_STACK_GUARD

#include <mprotect.h>

#endif

#if /* ARMCC */ ( (defined ( __CC_ARM ) && defined ( __TARGET_FPU_VFP )) \

/* Clang */ || (defined ( __clang__ ) && defined ( __VFP_FP__ ) && !defined(__SOFTFP__)) \

/* IAR */ || (defined ( __ICCARM__ ) && defined ( __ARMVFP__ )) \

/* GNU */ || (defined ( __GNUC__ ) && defined ( __VFP_FP__ ) && !defined(__SOFTFP__)) )

#define USE_FPU 1

#else

#define USE_FPU 0

#endif

/* exception and interrupt handler table */

rt_uint32_t rt_interrupt_from_thread;

rt_uint32_t rt_interrupt_to_thread;

rt_uint32_t rt_thread_switch_interrupt_flag;

/* exception hook */

static rt_err_t (*rt_exception_hook)(void *context) = RT_NULL;

struct exception_stack_frame

{

rt_uint32_t r0;

rt_uint32_t r1;

rt_uint32_t r2;

rt_uint32_t r3;

rt_uint32_t r12;

rt_uint32_t lr;

rt_uint32_t pc;

rt_uint32_t psr;

};

struct stack_frame

{

#if USE_FPU

rt_uint32_t flag;

#endif /* USE_FPU */

/* r4 ~ r11 register */

rt_uint32_t r4;

rt_uint32_t r5;

rt_uint32_t r6;

rt_uint32_t r7;

rt_uint32_t r8;

rt_uint32_t r9;

rt_uint32_t r10;

rt_uint32_t r11;

struct exception_stack_frame exception_stack_frame;

};

struct exception_stack_frame_fpu

{

rt_uint32_t r0;

rt_uint32_t r1;

rt_uint32_t r2;

rt_uint32_t r3;

rt_uint32_t r12;

rt_uint32_t lr;

rt_uint32_t pc;

rt_uint32_t psr;

#if USE_FPU

/* FPU register */

rt_uint32_t S0;

rt_uint32_t S1;

rt_uint32_t S2;

rt_uint32_t S3;

rt_uint32_t S4;

rt_uint32_t S5;

rt_uint32_t S6;

rt_uint32_t S7;

rt_uint32_t S8;

rt_uint32_t S9;

rt_uint32_t S10;

rt_uint32_t S11;

rt_uint32_t S12;

rt_uint32_t S13;

rt_uint32_t S14;

rt_uint32_t S15;

rt_uint32_t FPSCR;

rt_uint32_t NO_NAME;

#endif

};

struct stack_frame_fpu

{

rt_uint32_t flag;

/* r4 ~ r11 register */

rt_uint32_t r4;

rt_uint32_t r5;

rt_uint32_t r6;

rt_uint32_t r7;

rt_uint32_t r8;

rt_uint32_t r9;

rt_uint32_t r10;

rt_uint32_t r11;

#if USE_FPU

/* FPU register s16 ~ s31 */

rt_uint32_t s16;

rt_uint32_t s17;

rt_uint32_t s18;

rt_uint32_t s19;

rt_uint32_t s20;

rt_uint32_t s21;

rt_uint32_t s22;

rt_uint32_t s23;

rt_uint32_t s24;

rt_uint32_t s25;

rt_uint32_t s26;

rt_uint32_t s27;

rt_uint32_t s28;

rt_uint32_t s29;

rt_uint32_t s30;

rt_uint32_t s31;

#endif

struct exception_stack_frame_fpu exception_stack_frame;

};

rt_uint8_t *rt_hw_stack_init(void *tentry,

void *parameter,

rt_uint8_t *stack_addr,

void *texit)

{

struct stack_frame *stack_frame;

rt_uint8_t *stk;

unsigned long i;

stk = stack_addr + sizeof(rt_uint32_t);

stk = (rt_uint8_t *)RT_ALIGN_DOWN((rt_uint32_t)stk, 8);

stk -= sizeof(struct stack_frame);

stack_frame = (struct stack_frame *)stk;

/* init all register */

for (i = 0; i < sizeof(struct stack_frame) / sizeof(rt_uint32_t); i ++)

{

((rt_uint32_t *)stack_frame)[i] = 0xdeadbeef;

}

stack_frame->exception_stack_frame.r0 = (unsigned long)parameter; /* r0 : argument */

stack_frame->exception_stack_frame.r1 = 0; /* r1 */

stack_frame->exception_stack_frame.r2 = 0; /* r2 */

stack_frame->exception_stack_frame.r3 = 0; /* r3 */

stack_frame->exception_stack_frame.r12 = 0; /* r12 */

stack_frame->exception_stack_frame.lr = (unsigned long)texit; /* lr */

stack_frame->exception_stack_frame.pc = (unsigned long)tentry; /* entry point, pc */

stack_frame->exception_stack_frame.psr = 0x01000000L; /* PSR */

#if USE_FPU

stack_frame->flag = 0;

#endif /* USE_FPU */

/* return task's current stack address */

return stk;

}

#ifdef RT_USING_HW_STACK_GUARD

void rt_hw_stack_guard_init(rt_thread_t thread)

{

rt_mem_region_t stack_top_region, stack_bottom_region;

rt_ubase_t stack_bottom = (rt_ubase_t)thread->stack_addr;

rt_ubase_t stack_top = (rt_ubase_t)((rt_uint8_t *)thread->stack_addr + thread->stack_size);

rt_ubase_t stack_bottom_region_start = RT_ALIGN(stack_bottom, MPU_MIN_REGION_SIZE);

rt_ubase_t stack_top_region_start = RT_ALIGN_DOWN(stack_top - MPU_MIN_REGION_SIZE, MPU_MIN_REGION_SIZE);

stack_top_region.start = (void *)stack_top_region_start;

stack_top_region.size = MPU_MIN_REGION_SIZE;

stack_top_region.attr = RT_MEM_REGION_P_NA_U_NA;

stack_bottom_region.start = (void *)stack_bottom_region_start;

stack_bottom_region.size = MPU_MIN_REGION_SIZE;

stack_bottom_region.attr = RT_MEM_REGION_P_NA_U_NA;

rt_mprotect_add_region(thread, &stack_top_region);

rt_mprotect_add_region(thread, &stack_bottom_region);

thread->stack_buf = thread->stack_addr;

thread->stack_addr = (void *)(stack_bottom_region_start + MPU_MIN_REGION_SIZE);

thread->stack_size = (rt_uint32_t)(stack_top_region_start - stack_bottom_region_start - MPU_MIN_REGION_SIZE);

}

#endif

/**

* This function set the hook, which is invoked on fault exception handling.

*

* @param exception_handle the exception handling hook function.

*/

void rt_hw_exception_install(rt_err_t (*exception_handle)(void *context))

{

rt_exception_hook = exception_handle;

}

#define SCB_CFSR (*(volatile const unsigned *)0xE000ED28) /* Configurable Fault Status Register */

#define SCB_HFSR (*(volatile const unsigned *)0xE000ED2C) /* HardFault Status Register */

#define SCB_MMAR (*(volatile const unsigned *)0xE000ED34) /* MemManage Fault Address register */

#define SCB_BFAR (*(volatile const unsigned *)0xE000ED38) /* Bus Fault Address Register */

#define SCB_AIRCR (*(volatile unsigned long *)0xE000ED0C) /* Reset control Address Register */

#define SCB_RESET_VALUE 0x05FA0004 /* Reset value, write to SCB_AIRCR can reset cpu */

#define SCB_CFSR_MFSR (*(volatile const unsigned char*)0xE000ED28) /* Memory-management Fault Status Register */

#define SCB_CFSR_BFSR (*(volatile const unsigned char*)0xE000ED29) /* Bus Fault Status Register */

#define SCB_CFSR_UFSR (*(volatile const unsigned short*)0xE000ED2A) /* Usage Fault Status Register */

#ifdef RT_USING_FINSH

源码下载

…\bsp\stm32\stm32f746-st-disco\project.uvproj

RT-Thread STM32F746-st-disco开发板BSP说明 源码下载

903

903

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?