FPGA学习误区:

1.花太长时间学习verilog语法

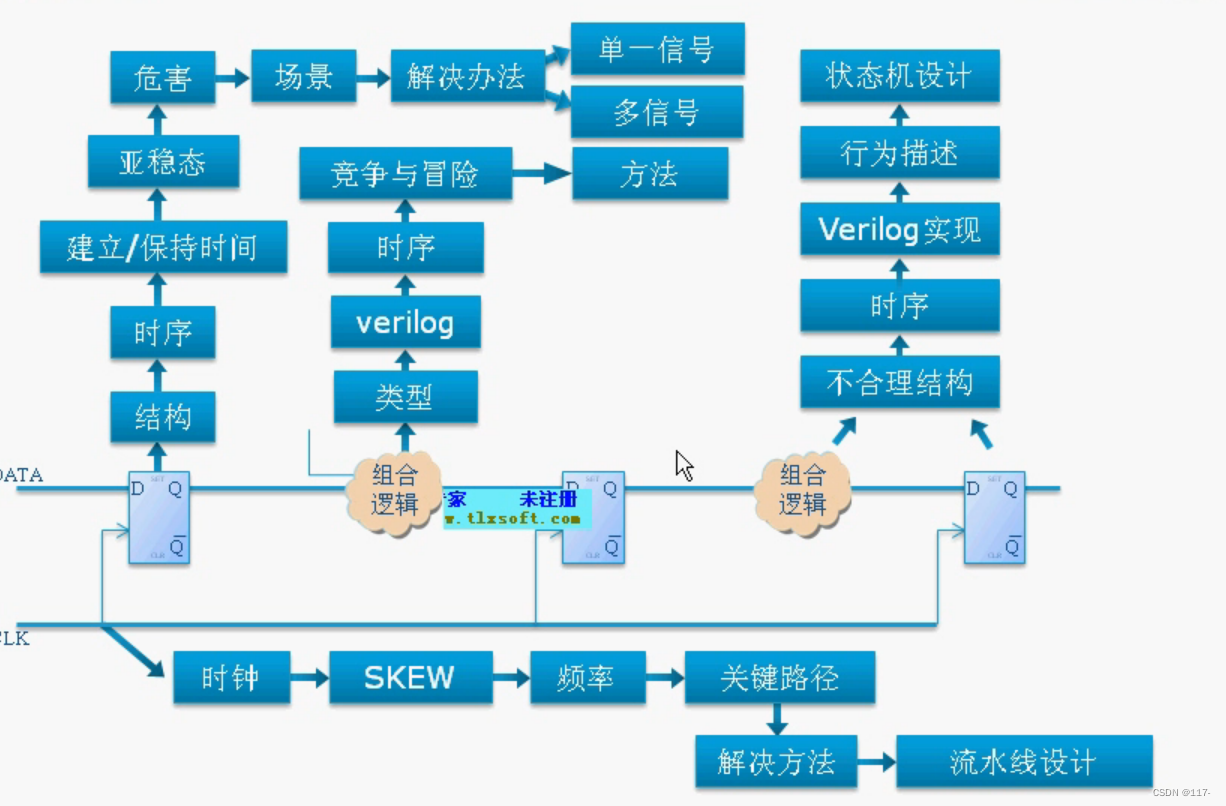

2.软件思维:FPGA是借用verilog将已有的电路结构描述出来,而非用verilog设计出电路

3.设计的好坏并非看代码量,而是看综合出来的电路

TIPS:1.begin里的代码并非串行执行的

2.关于<=和=,时序电路用<=,组合电路用=,别太纠结

组合逻辑:

1.一个组合逻辑电路+一个D触发器就构成了一个功能电路

2.组合逻辑包含:1)门级逻辑:与、或、非等

2)选择器、比较器(本质上还是由门逻辑组成的功能电路

3)运算逻辑:加减乘除等(本质上也是由门逻辑组成的功能电路

TIPS:有些verilog代码是不可综合的,verilog中存在一些用于仿真验证的语句,只在仿真的时候使用,不可综合成电路,因为没有相应的硬件与其对应

竞争与冒险:

解决办法:1.D触发器对竞争冒险不敏感(D触发器的使用会给系统带来一定的延时

2.组合逻辑输出不要连到时钟、复位

3.模块输出要寄存器输出(寄存器输出在时钟信号的边沿才会更新数据,并在整个时钟周期内保持稳定。这样可以避免数据在传输过程中出现不确定的变化,例如:LED灯的状态取决于输入信号。如果直接将组合逻辑产生的输出连接到LED灯,由于信号传播延迟的影响,LED灯的状态可能会闪烁或产生不稳定的效果。而使用寄存器输出,LED灯的状态只在时钟信号的边沿改变,保持稳定的亮或灭状态,避免了闪烁或不稳定的情况。

D触发器:

D触发器的输出Q只在时钟边沿或复位有效的时候发生变化。

D触发器在上升沿时Q=D,若此时输入D也同时发生变化,此时输出Q无法确定是0还是1,因此设定一个建立/保持时间的概念。

建立时间:上升沿到来的前一段时间内,输入端D不变。

保持时间:上升沿到来后的一段时间内,输入端D不变。

D触发器亚稳态:不满足建立/保持时间时,当上升沿到来,D触发器无法确定输出端Q是0还是1,而是在进行“思考”,这段时间没有处于稳定状态,就叫亚稳态。(亚稳态可能导致芯片挂死,如果不复位就无法继续正常工作)

亚稳态的出现场景:当存在不受本地时钟控制的信号,均有可能出现亚稳态(输入信号的边沿到来时间非常接近时钟边沿,例如:有一个异步信号(即不受本地时钟控制)直接作为触发器的输入,而该信号的边沿与时钟边沿非常接近,触发器可能无法在时钟边沿之间确定地切换状态)

亚稳态解决办法:

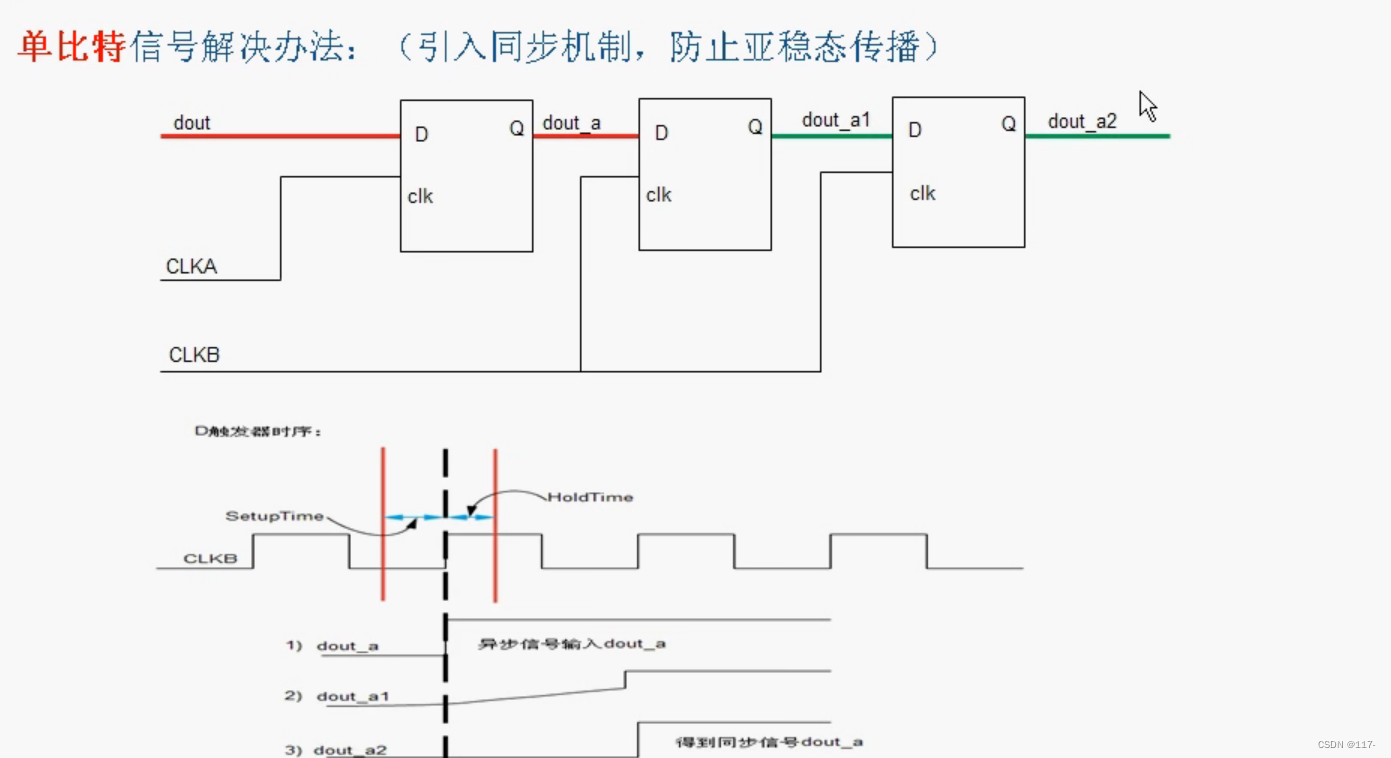

1.单比特信号解决办法:引入同步机制,防止亚稳态传播

如图:a是相当于一个异步信号,a1可能出现亚稳态,但是实际情况出现亚稳态的概率很低,连续两次出现亚稳态的概率更低。(打两拍再将信号传出去)

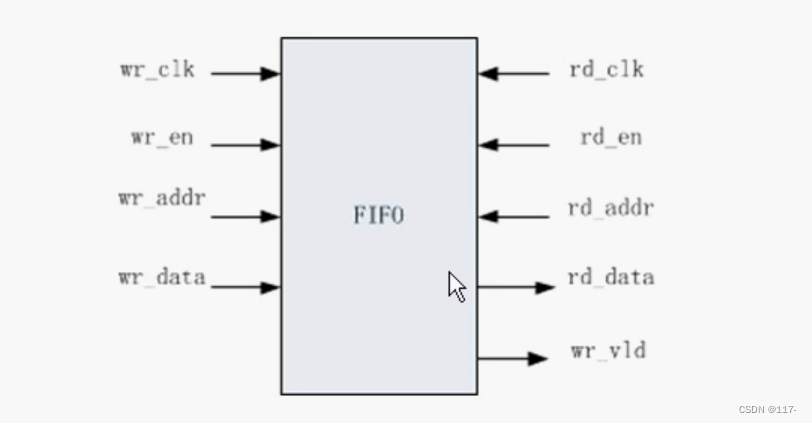

2.多比特信号解决方法:①使用FIFO

一侧有写时钟(异步信号输入),一侧有读时钟,两个时钟不一样,FIFO内部已经做好了异步处理

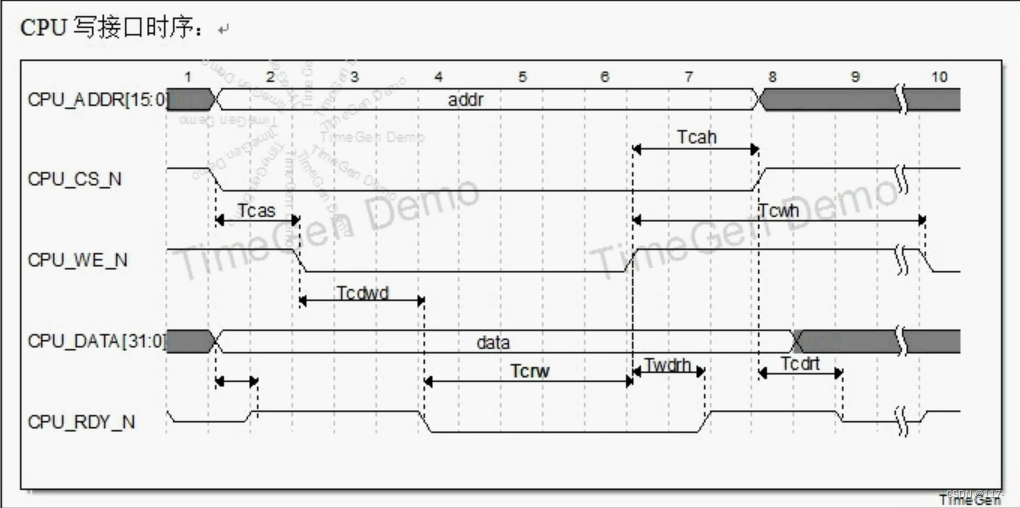

多比特信号解决办法2:用一个使能信号(当数据流小的时候可以使用,因为当数据流小的时候使用FIFO显得有些浪费,数据流小指的是很久才有一次信号,例如几毫秒)

eg:上游CPU接口传输数据到下游FPGA接口,我们希望FPGA接口时钟沿到来时,传输的数据是稳定的,这就需要一个信号告知FPGA接口:此时信号是稳定的,这个信号即使能信号,但使能信号属于单比特信号,因此需要引入同步机制,使能信号有效期间,传输的数据不能发生变化。

TIPS:异步时钟要进行亚稳态处理,即使同为一百兆,但不是同一个时钟,也要进行亚稳态处理。

时序逻辑:

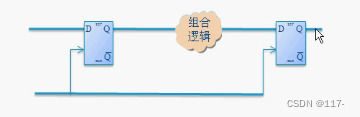

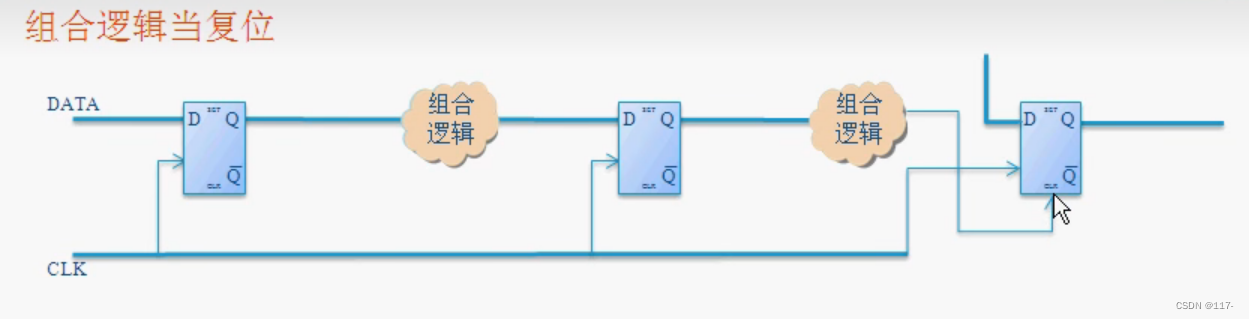

时序逻辑是由组合逻辑+D触发器构成的(如下图)

上图是时序逻辑正确的结构

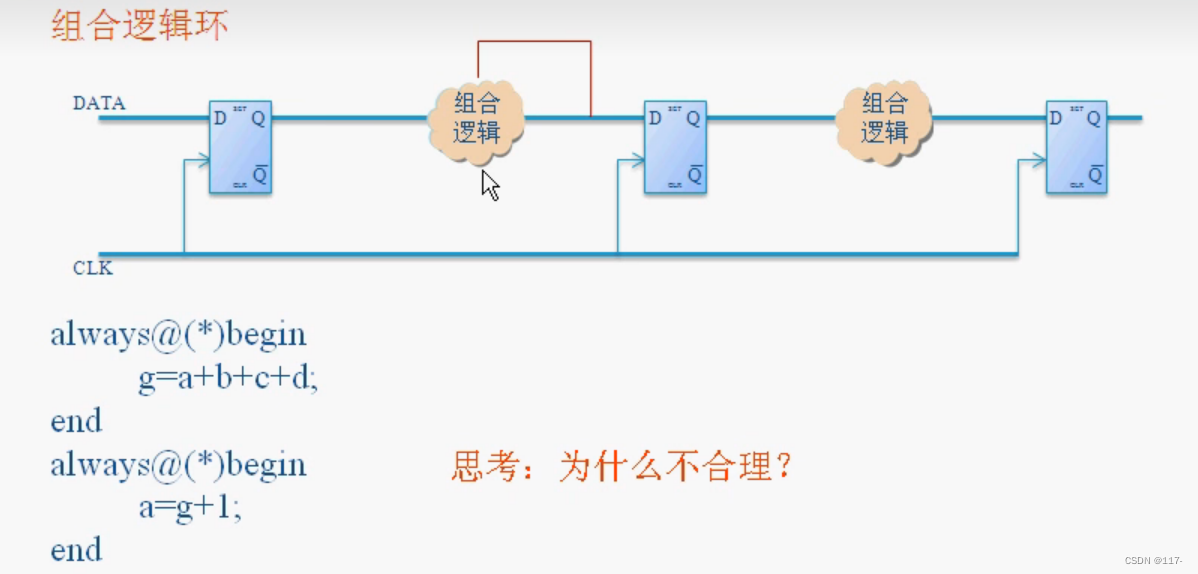

上图是不正确的时序逻辑,存在组合逻辑到自身的组合逻辑环,是不合理的结构

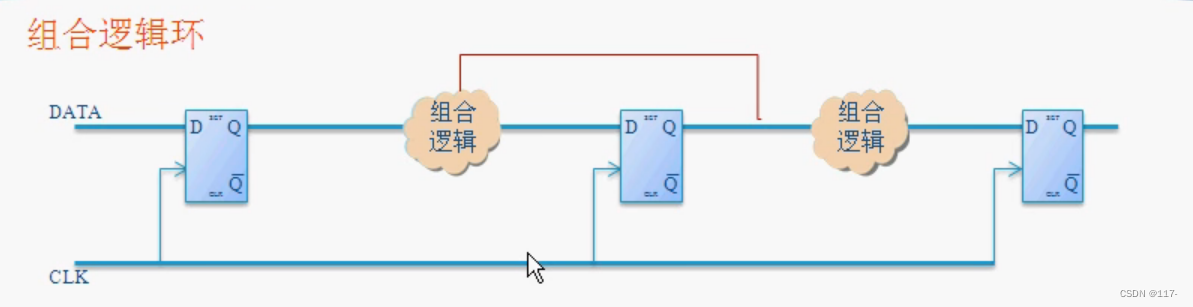

而这样的组合逻辑环是可以的

而这样的组合逻辑环是可以的

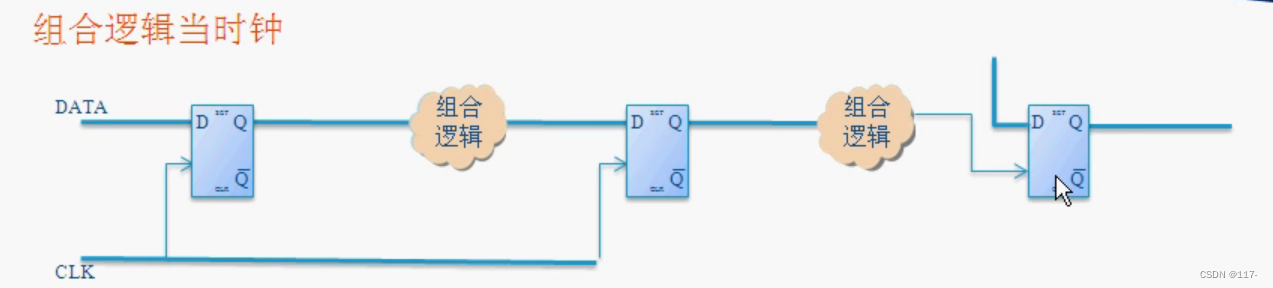

组合逻辑的输出存在毛刺,不可以做为时钟输入端,时钟在FPGA中非常重要,时钟输入端不要连其他时钟发生电路以外的其他信号电路

组合逻辑的输出存在毛刺,不可以做为时钟输入端,时钟在FPGA中非常重要,时钟输入端不要连其他时钟发生电路以外的其他信号电路

同理,复位端也不要连组合逻辑电路

同理,复位端也不要连组合逻辑电路

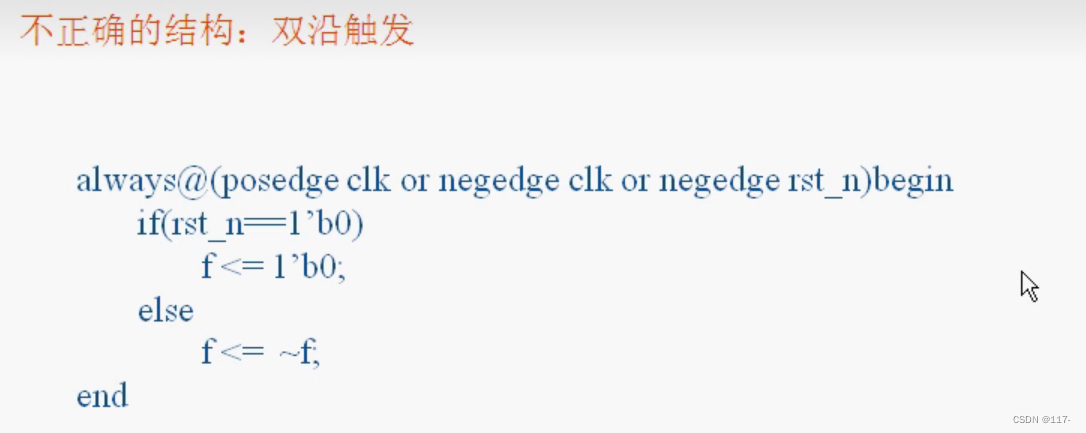

FPGA只能对时钟的一个沿进行优化,不可以在时钟的两个沿都进行触发

FPGA只能对时钟的一个沿进行优化,不可以在时钟的两个沿都进行触发

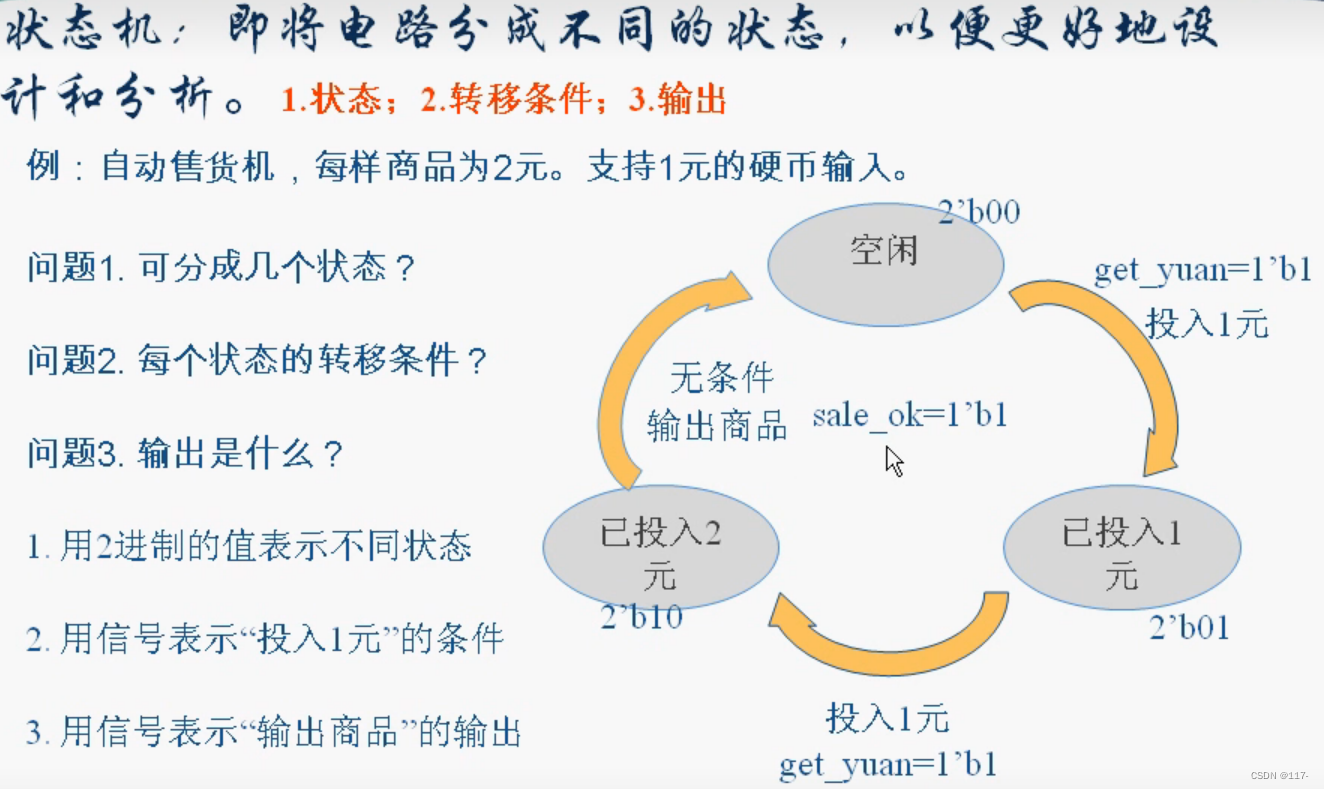

状态机的三个要素:1.状态2.状态转移条件3.输出

状态机的三个要素:1.状态2.状态转移条件3.输出

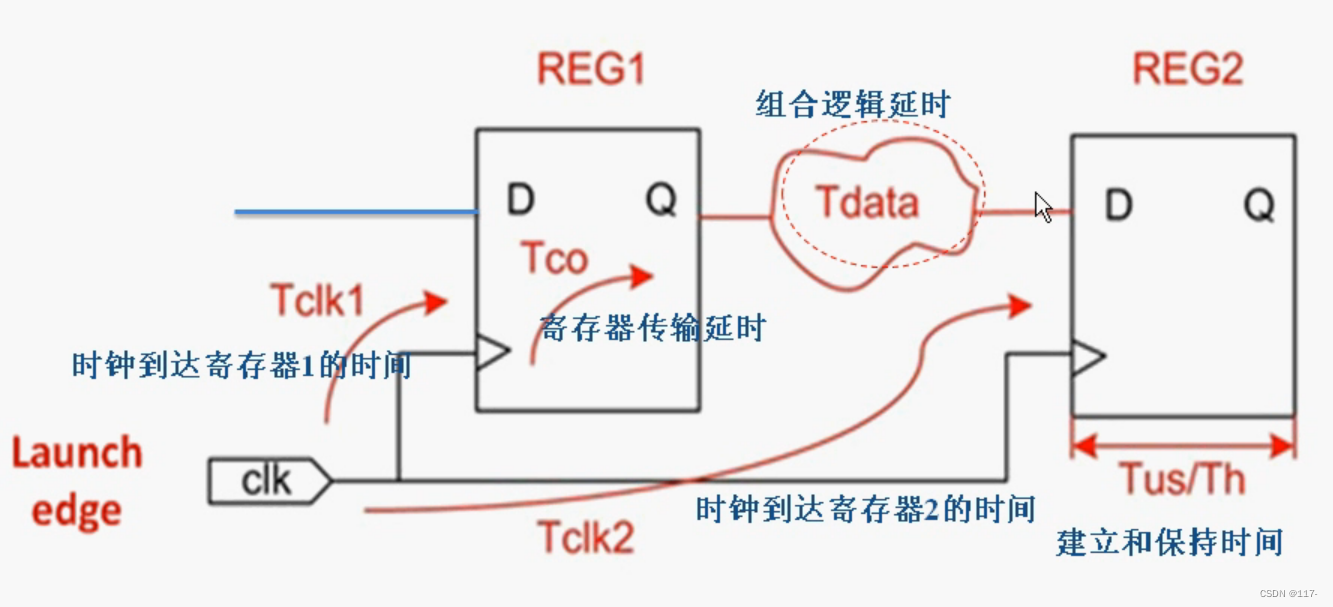

FPGA时序(重要):

几个基本概念:

几个基本概念:

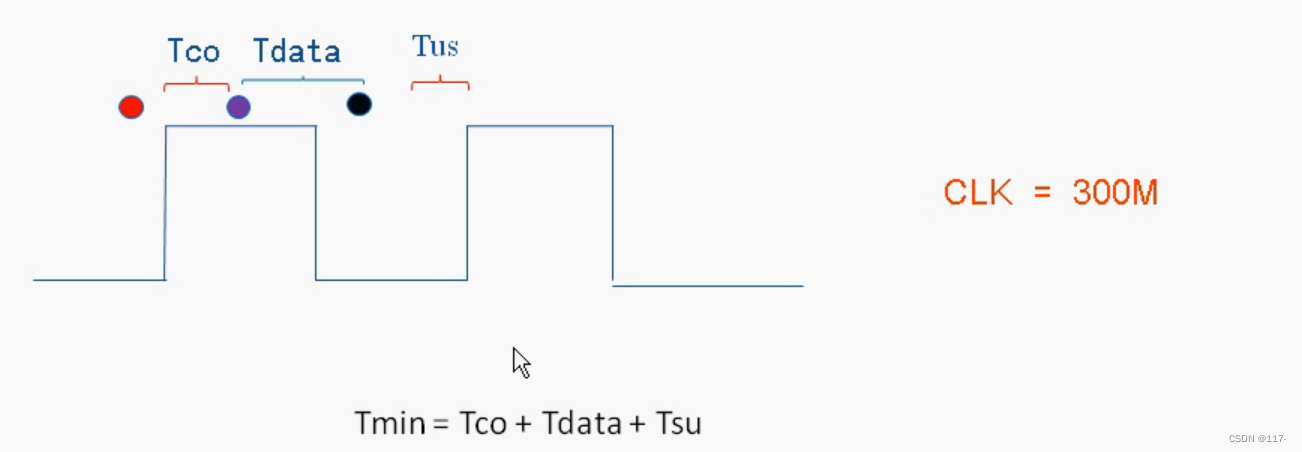

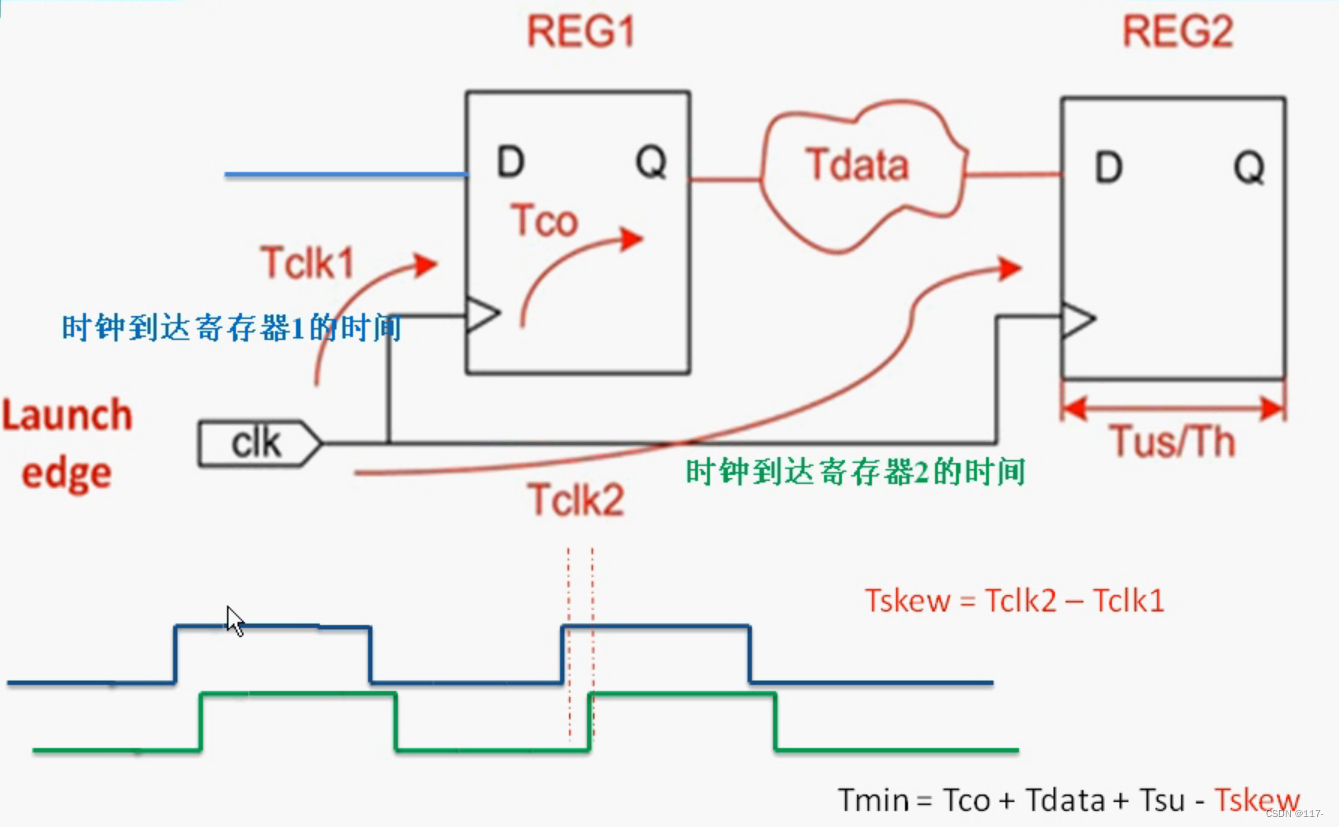

1.时钟到达寄存器的时间:Tclk(路径不同,同一时钟到达不同寄存器的时间不同)

2.寄存器传输时延:Tco(数据从寄存器输入端到寄存器输出端所需时间)

3.组合逻辑时延:Tdata(类似Tco)

4.建立/保持时间:Tus/Th

5.偏抖:Tskew=Tclk2-Tclk1(可能是正数也可能是负数,Tclk2是目的地,Tclk1是源)

最小时钟周期公式,此时的频率为电路可以取到的最大时钟频率,若要提高时钟频率,需想办法缩小Tdata

最小时钟周期公式,此时的频率为电路可以取到的最大时钟频率,若要提高时钟频率,需想办法缩小Tdata

由于偏抖的存在,使时钟周期得以改善(当偏抖Tskew是正数则起改善作用,是负数的时候则起恶化的作用)

由于偏抖的存在,使时钟周期得以改善(当偏抖Tskew是正数则起改善作用,是负数的时候则起恶化的作用)

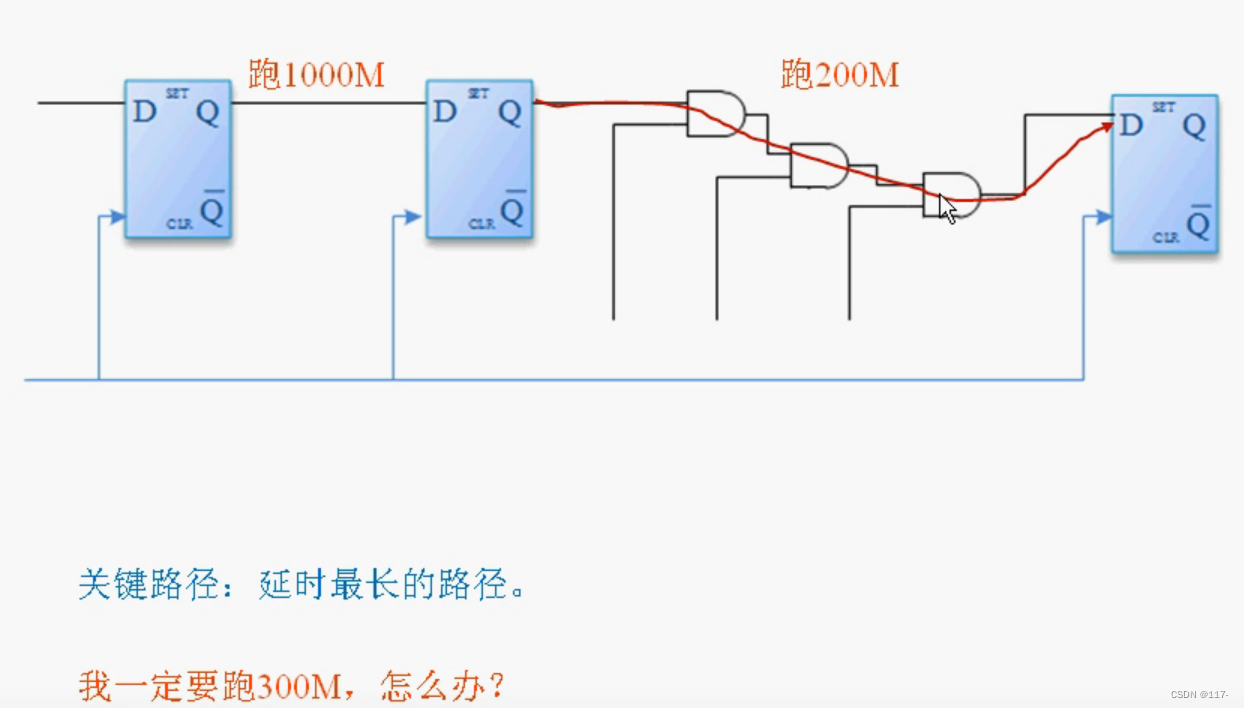

关键路径的概念,最小时钟周期取决于延时最长的路径,即关键路径

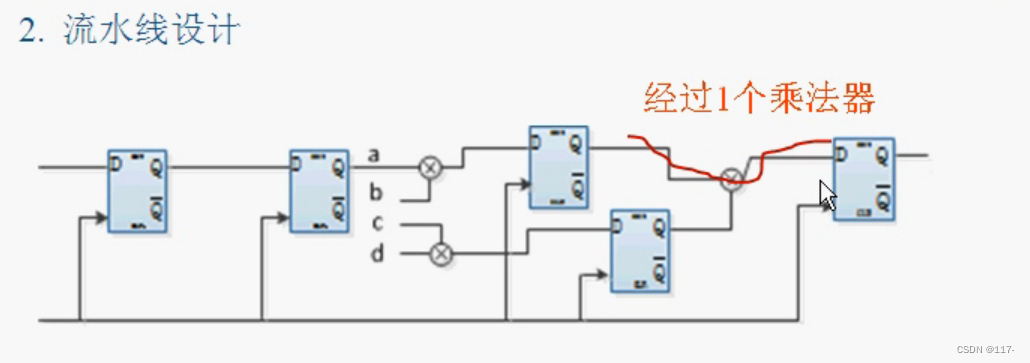

流水线设计

流水线设计

要提高时钟频率,可以通过流水线设计,将功能进行拆分,使得两个寄存器之间的延时达到最小,最小时钟周期越短,最大时钟频率就越大

总结:

1417

1417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?