- 博客(14)

- 资源 (1)

- 收藏

- 关注

原创 FPGA多周期路径约束

多周期路径约束主要用在四种情况下。①带有使能的数据(例如:使能周期为2倍的时钟周期)set_multicycle_path -from [get_cells {cmd_parse_i0/send_resp_data_reg[]}] -to [get_cells {resp_gen_i0/to_bcd_i0/bcd_out_reg[]}] 2set_multicycle_path -hold -from [get_cells {cmd_parse_i0/send_resp_data_reg[]}] -t

2021-03-24 10:51:07

502

502

原创 FPGA时序约束-设置伪路径和设置异步时钟

**什么是设置伪路径?**伪路径是指该路径存在,但该路径的电路功能不会发生或者无须时序约束。创建伪路径的好处:可以减少工具运行优化时间,增强实现结果,避免在不需要进行时序约束的地方花费较多时间。设置伪路径一般用在:①跨时钟域,②一但上电就被写入数据的寄存器,③异步复位或测试逻辑,④异步双端口RAM。总结:伪路径主要就是用在异步时钟的处理上。**注意的是:**伪路径的设置是单向的,如果两时钟之间存在相互的数据传输,则需要再反向设置一次伪路径。举例如何设置伪路径:在异步时钟的位置右击选择设置伪路径即

2021-03-24 10:08:39

2761

2761

原创 约束衍生时钟

该问题主要是解决时钟约束语句中时钟具体位置怎么找到的。例如:create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins clk_gen_i0/BUFHCE_clk_samp_i0/O]时钟路径就是时钟对应一个个模块往下找到的位置,clk_tx的位置在clk_gen_i0模块下的clk_core_i0模块里。...

2021-03-23 21:35:53

313

313

原创 vivado原语BUFHCE

今天再看vivado自带官方例程wave_gen中看到了BUFHCE原语的使用。格式如下:BUFHCE #(.INIT_OUT(0) // Initial output value)BUFHCE_clk_samp_i0(.O (clk_samp), // 1-bit The output of the BUFH.CE (en_clk_samp),// 1-bit Enables propagation of signal from I to O.I

2021-03-23 21:06:42

2235

2235

原创 vivado时序出错的解决方法

这几天一直改程序,请教师兄帮我解决了一些时序上的问题。由于现在项目里用的是200M时钟,所以会出现很多时序问题,下面一一举例。问题1:逻辑级数太高导致Net Delay过高,该问题显示在时许报告的Levels列下,如图1所示。(这里我已经解决了问题,图片只是指出Levels)图1导致该问题出现的有两种情况,第一种是由于程序中自己写的逻辑级数过高,比如:assign a = cb + de ,这种情况在高速时钟下是会导致时序问题。讲一下我自己遇到的问题吧,reg_q <= -fifo_out;

2020-07-31 16:54:58

10271

10271

原创 vivado保存ila的波形

1.保存ila数据的TCL命令write_hw_ila_data E:/yourpath/name_ila.ila [upload_hw_ila_data hw_ila_4]注意:目录中不能有space,中文name_ila为保存的文件名,需要带路径,注意是右斜“/”.hw_ila_4为你的ILA的名字,[ ]中为对应的ILA核。2.可以读取保存的ila数据,并在vivado上显示read_hw_ila_data E:/yourpath/name_ila.iladisplay_hw_ila_d

2020-07-31 14:57:20

4885

4885

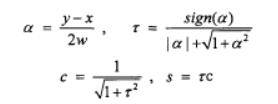

原创 关于矩阵白化的问题

之前我在FPGA上实现了脉动阵列的SVD分解,接下来我要对矩阵白化遇到了问题。白化公式:对相关矩阵Rx做特征分解或SVD分解。白化矩阵T公式如上,有一个问题是如果求得的奇异值太小,比如我现在处理数据遇到的问题,三路信号虽然都是不相关的,但是算出的其中一个奇异值太小(小数点后六位),然后再做开跟求倒数会导致数据大小猛增到百万,到后面可能导致数据过大,FPGA无法表示的问题。来看奇异值定义:奇异值:设A为mn阶矩阵,AHA的n个特征值的非负平方根叫作A的奇异值。记为σi(A)特征值:一矩阵A作用

2020-06-02 08:47:54

883

883

原创 BLV脉动阵列实现矩阵SVD分解

在信号处理中经常碰到观测值的自相关矩阵,从物理意义上说,如果该观测值是由几个(如 K 个)相互统计独立的源信号线性混合而成,则该相关矩阵的秩或称维数就为 K,由这 K 个统计独立信号构成 K 维的线性空间,可由自相关矩阵最大 K 个特征值所对应的特征向量或观测值矩阵最大 K 个奇异值所对应的左奇异向量展成的子空间表示,通常称信号子空间,它的补空间称噪声子空间,两类子空间相互正交。理论上,由于噪声的...

2020-04-29 11:58:43

1099

1099

10

10

原创 SVD分解基于FPGA实现2

关于jacobi的基本原理网上资料很多,它求解正余弦值的方法是通过求解方程得来的。这样做可以方便求出正余弦值,但是不利于FPGA硬件实现,FPGA中可以用cordic算法求出反正切以及正余弦值,所以FPGA实现时应当使用arctan求出theta值,再直接算出正余弦结果,...

2020-04-22 09:02:20

1654

1654

原创 SVD分解基于FPGA实现1

现在正在看一篇SVD算法基于FPGA实现的论文,有一些收获。首先要知道,1.verilog中直接写“ + ”实现两数据相加,综合后的结果是逻辑门组成,在运算量大的时候还是应当选择加法器ip实现,这样便于控制latency2.使用乘法器ip可以选择使用dsp资源来实现,可以灵活设置流水级数,不占用过多逻辑资源。在这篇文章里,采用的是单边jacobi算法实现svd分解,模块是这样的。他的设...

2020-04-21 09:34:40

1806

1806

2

2

原创 关于特征值分解后续

已经尝试将double型数据写成的特征值分解模块用在盲源分离的工程中,由于精度的问题,在频率较低的情况下可以分解成功,但是一旦频率过高,分解出的三路信号频率在一个位置,不满足要求。接下来准备看一下关于SVD分解运用在fpga中的文章,希望在迭代过程中数据尽量小。...

2020-04-20 16:26:39

264

264

原创 记录自己遇到的问题1

2020.4.17 开始记录自己遇到的问题基于fpga实现fast ICA算法的框架大致完成,但是白化的模块还有不少问题。使用的是jacobi迭代算法实现三阶对称矩阵的特征值分解(我看到别人的论文中用的是SVD分解),由于之前使用32位定点数表示数据,能够表示的最大范围不够,结果楞是用单精度浮点数去做jacobi,当然就精度不够了,附上float与double的范围和精度。接下来是用do...

2020-04-17 11:00:26

232

232

空空如也

TA创建的收藏夹 TA关注的收藏夹

TA关注的人

RSS订阅

RSS订阅