第一次接触亚稳态的概念,是在野火FPGA教学视频里,在串口通信的章节里,使用打两拍的方法降低亚稳态的隐患,当时对这个概念似懂非懂,也就是照着了例程加了两级寄存器,最近在学习中又接触到了这个概念,对其理解也更加深入,因此撰写本篇文章进行相关内容的总结。

一、什么是亚稳态?

亚稳态是指在设计的正常运行过程中,信号在一定时间内不能达到稳定的0或者1的现象。亚稳态问题常常在信号的跨时钟域处理中遇到,上文中提到的FPGA与PC之间进行串口通信就是一个很典型的例子。

我们知道时序电路中的基本单元是D触发器,由于器件的物体特性(该部分内容可参考(149条消息) 亚稳态处理之两级同步和握手_我去给你买橘子吃的博客-CSDN博客),D触发器进行采样时对被采样的信号有一定的要求:

(1)在上升沿到来之前的一定时间内,信号要保持稳定,也就是图中的Tsu,su是setup的简写,也即建立时间。

(2)在上升沿到来之后的一定时间内,信号要保持稳定,也就是图中的Th,h是hold的简写,也即保持时间。

还是以FPGA和PC之间进行串口通信为例,在FPGA接受PC发送的数据的时候,需要检测RX的一个下降沿,但是由于FPGA和PC的时钟是异步的,这个下降沿到来的时间是随机的,有可能在FPGA的clk的上升沿的时候,RX也同时拉低了,FPGA的D触发器就刚刚好好采到了这个下降沿上(与图中的情况类似),没法满足上面的两个条件,这个时候D触发器的就可能出现亚稳态,需要等一段时间(Tmet)触发器的输出才能稳定到某个值上。

二、亚稳态的危害

由于亚稳态的输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。 逻辑误判有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用),而亚稳态的传播则扩大了故障面,难以处理。电平信号的逻辑误判一般只会对电路造成几个时钟的延时,后面还会稳定在需要的电平,不会造成逻辑错误。

三、如何降低亚稳态的影响

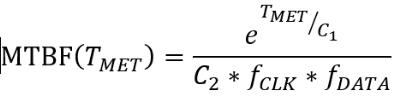

亚稳态不能从根本上消除,这是由器件的物理特性决定的,但是我们可以采取一些措施降低亚稳态的影响,由于亚稳态是由不同步造成的,最直接的办法就是想办法将两个时钟域的信号进行同步化。Altern在他们写的文章之中引入了MTBF(mean time between failures)这个参量来衡量亚稳态发生的可能性,越大的MTBF的值意味着发生两次问题之间的时间越长。其公式如下:

式中C1和C2为常数,器件的厂商会在手册中给出,fCLK 是接收异步信号的时钟域的时钟频率,fDATA 是异步数据的翻转频率(toggling frequency)。TMET是指寄存器从时钟上升沿触发后的时序裕量(slack),即下一级满足建立时间要求之后的裕量(注意与上文图中的Tmet进行区分,为了防止混淆,下文中写为 )。下图是一个典型的数字系统的电路模型。

)。下图是一个典型的数字系统的电路模型。

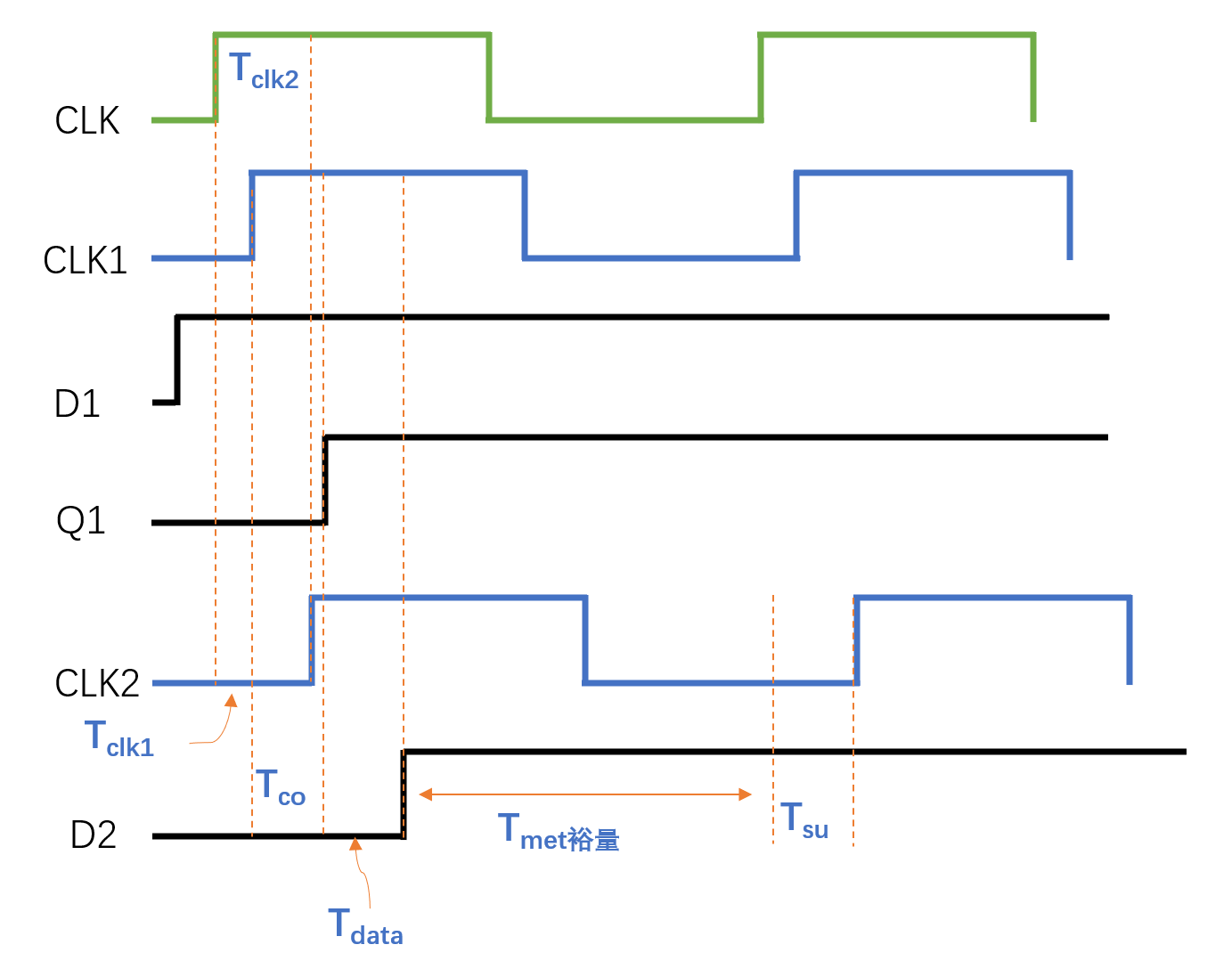

代表数据在两个触发器之间传输时的延时,

代表数据在两个触发器之间传输时的延时, 代表时钟到达第一个触发器时的延时时间,

代表时钟到达第一个触发器时的延时时间, 代表时钟到达第二个触发器时的延时时间,

代表时钟到达第二个触发器时的延时时间, 代表正常情况下触发器在上升沿采集到数据到Q端输出数据的延迟时间。下图是该模型的数据传输波形图。

代表正常情况下触发器在上升沿采集到数据到Q端输出数据的延迟时间。下图是该模型的数据传输波形图。

根据上图中的时序关系可以计算得到:

式中T为采样时钟周期, ,

, 都是由器件决定的,

都是由器件决定的, ,

, 为时钟信号的传输延时。为了尽可能增大

为时钟信号的传输延时。为了尽可能增大 ,最直接的办法就是减小组合逻辑部分的延时

,最直接的办法就是减小组合逻辑部分的延时 ,直接用一根导线连接两个寄存器。根据现有的器件工艺水平进行计算,采用两级寄存器进行同步就可以把亚稳态MTBF提高到几百年的水平,足以安全的使用。

,直接用一根导线连接两个寄存器。根据现有的器件工艺水平进行计算,采用两级寄存器进行同步就可以把亚稳态MTBF提高到几百年的水平,足以安全的使用。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?