一、IIC

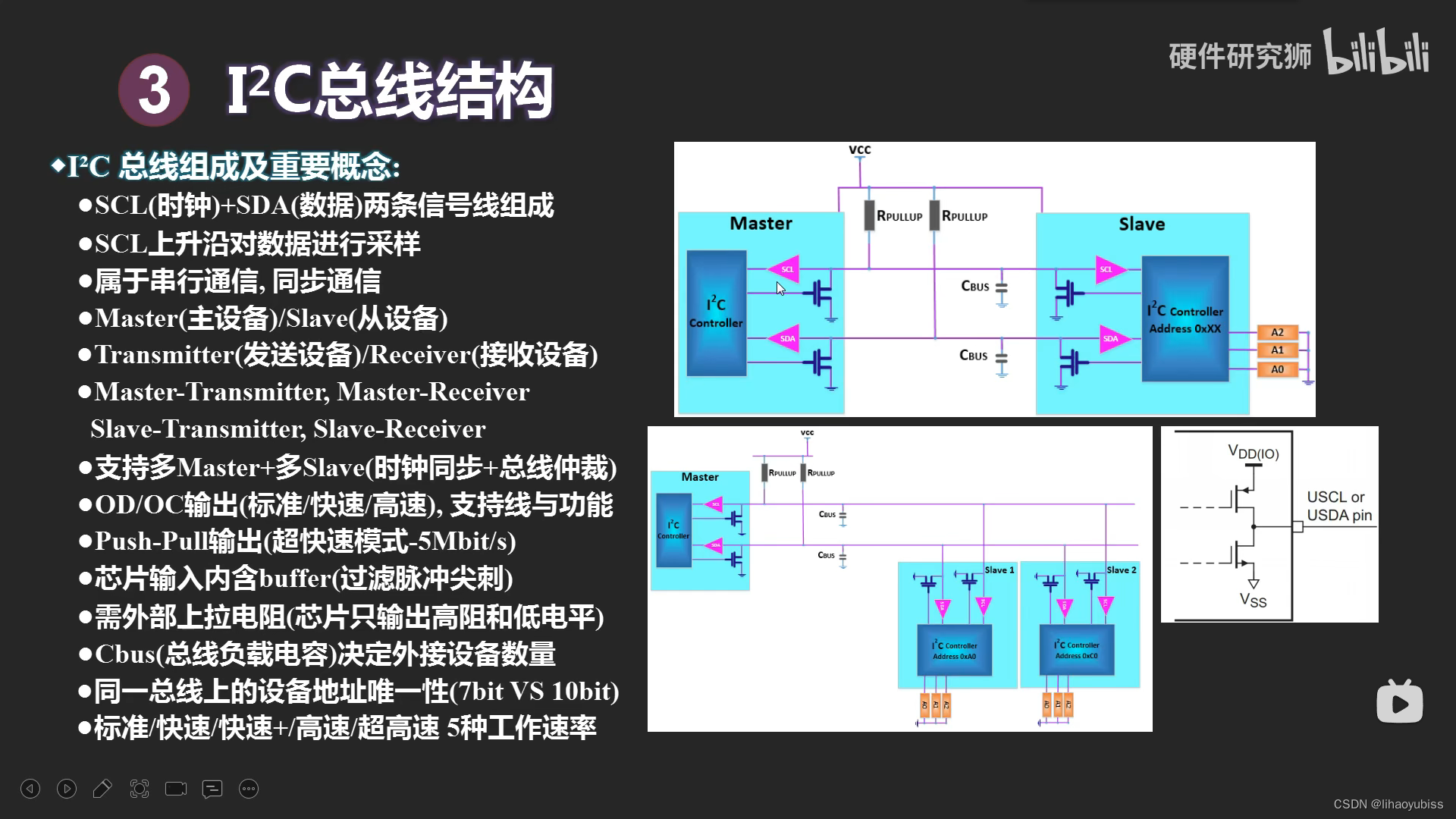

1.总线结构

2.工作模式

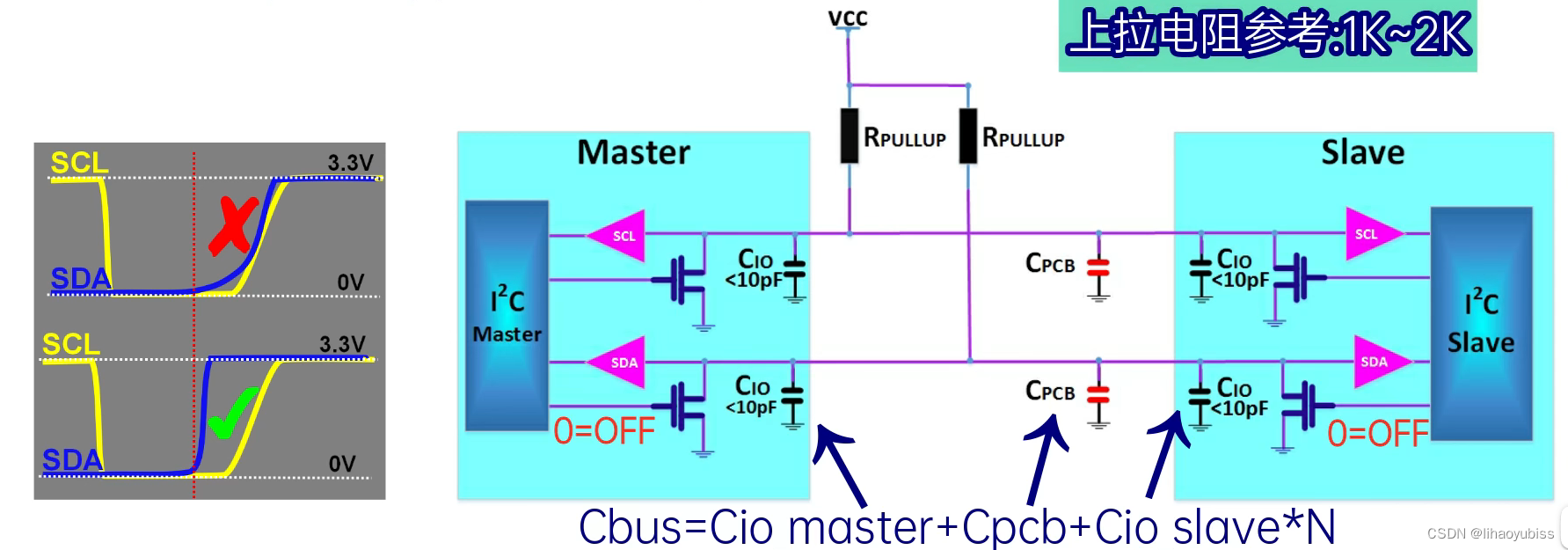

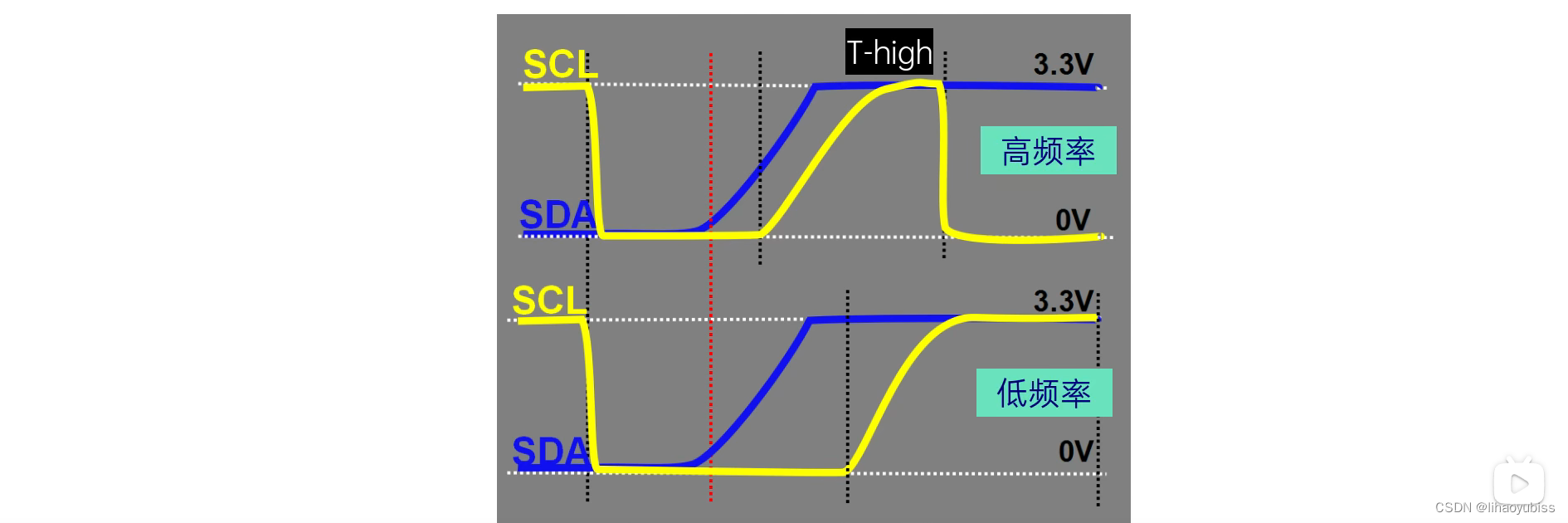

规范定义芯片管脚容性负载必须小于10pf,理论上能接40个设备。但是因为走线上存在寄生电容,设备数量远远减少。因为总线结构决定高电平的充电时间∝上拉电阻R*Cbus,若Cbus过大,SCL上升沿到来时Cbus电压低,即建立时间过短,被识别成低电平,采样错误。所以要保证Cbus足够小,有充足的建立时间。

Q:为什么快速模式是400pf,然后更快的快速+模式为什么是550pf,正常应该比400pf小才对

A:正常来说速率越快肯定外部的cbus需要越小越好,但是这里面有个变量就是 快速+模式的驱动电流是20mA比标准模式和快速模式的3mA大多了,所以规范定义的cbus也会比他们大

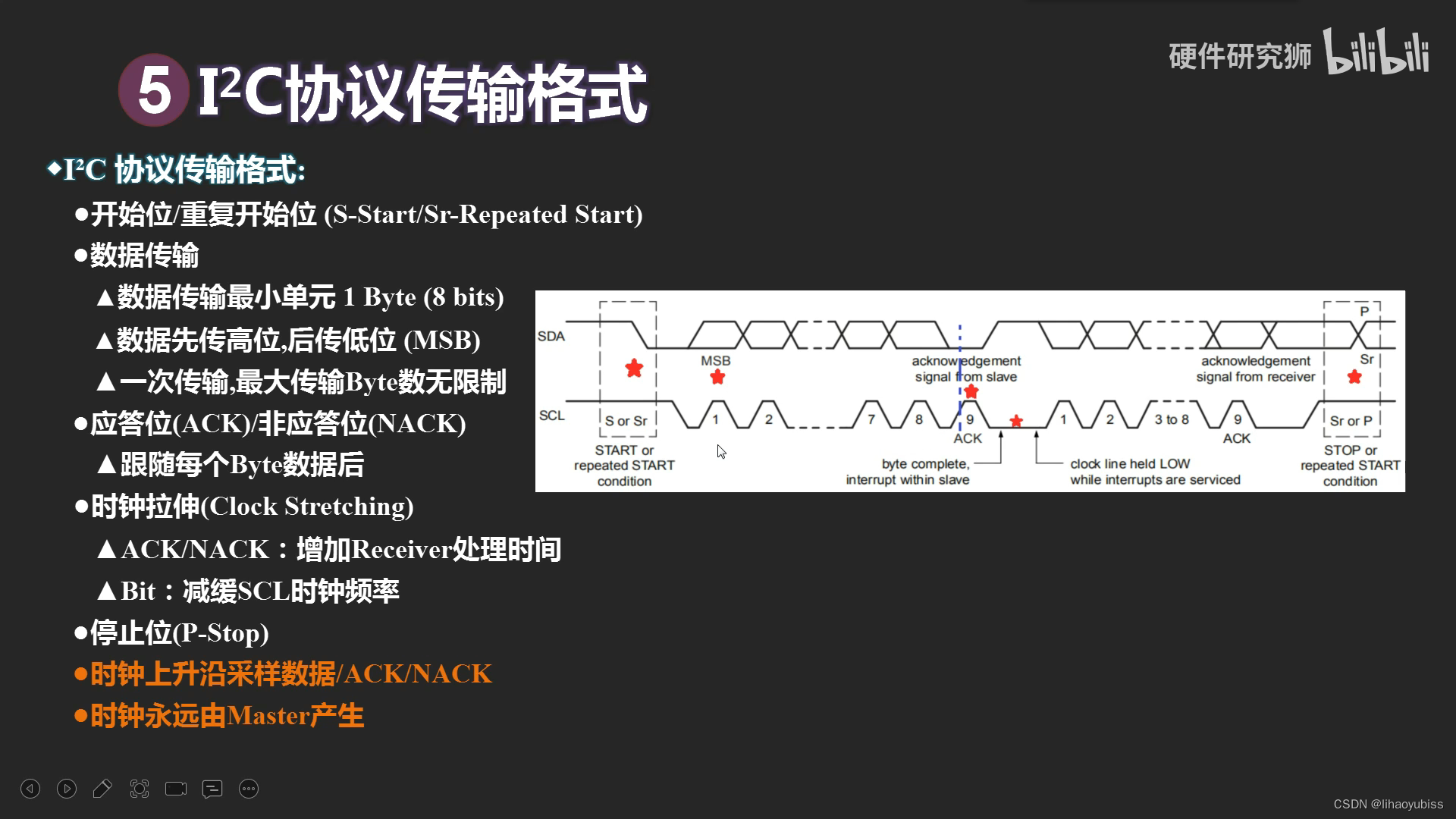

3.协议格式

- 数据是在时钟SCL上升沿时刻进行采样。

- 数据先传高位MSB,后传低位。

- 每个Byte后Receiver发送一个ACK/NACK。

- 少数芯片支持时钟拉伸功能,有2种使用情况

①在ACK/NACK后把SCL低电平时间拉长。当接收机接收到数据还没有处理完成,接收机接收到了一个中断等需要紧急处理的事情还没有处理完,留出一定的时间处理

②每个SCL的低电平拉长。应对两个芯片对于数据的处理速度是有差异的,通过这种方式弥补这种差异。 - SCL永远由主机发送,SDA可由主机从机分时发送。

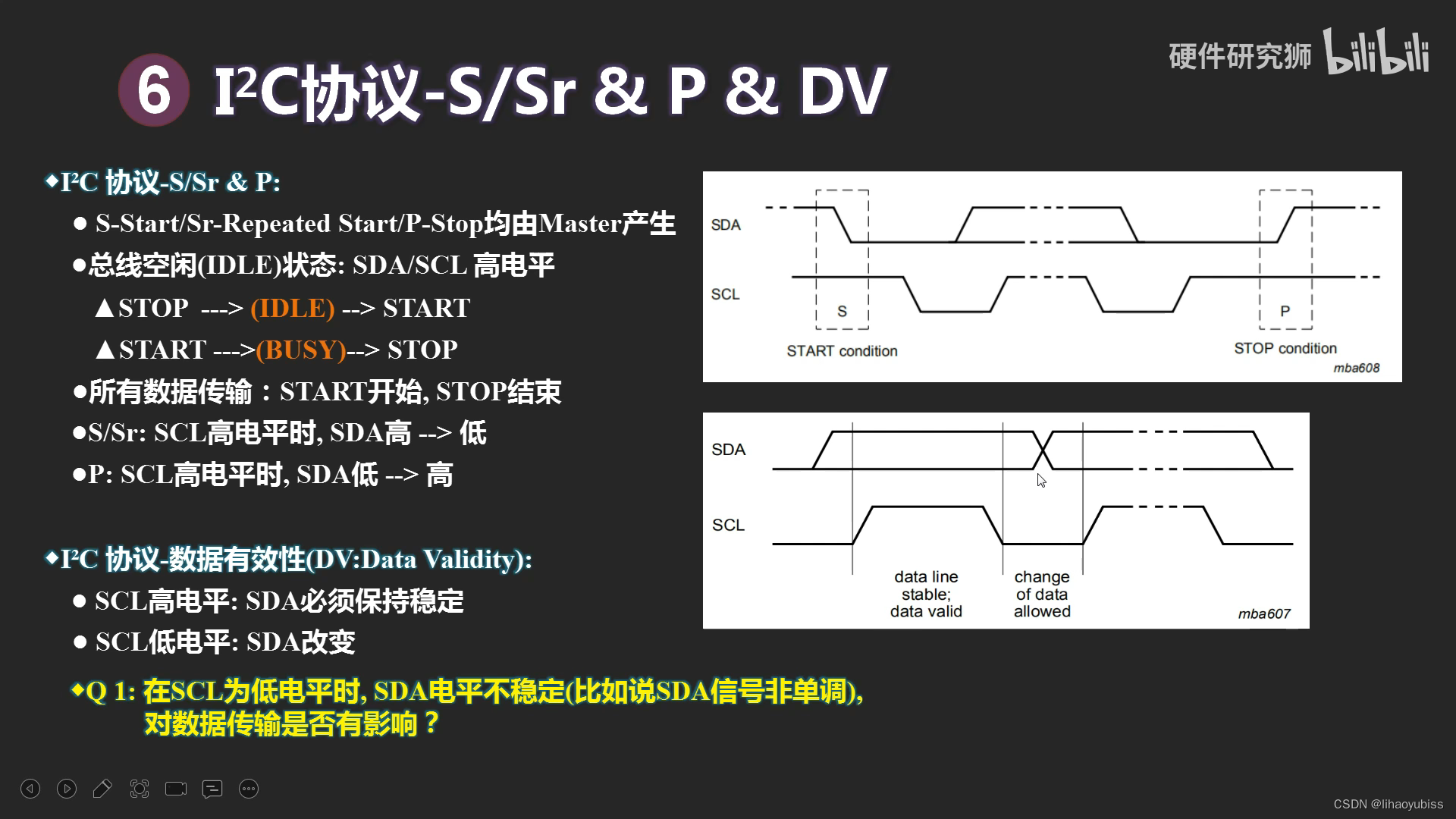

4.S/P/数据有效性

- 数据传输由S开始,P结束,中间传输多少Byte没有限制。

- SCL高电平时,SDA必须保持稳定;SCL上升沿前,SDA必须满足芯片的建立时间;SCL上升沿后,SDA必须满足芯片的保持时间

A1:没有影响,因为SDA只有在SCL 或者高电平的时候才有意义,SCL低电平的时候没有任何意义,所以无所谓SDA状态

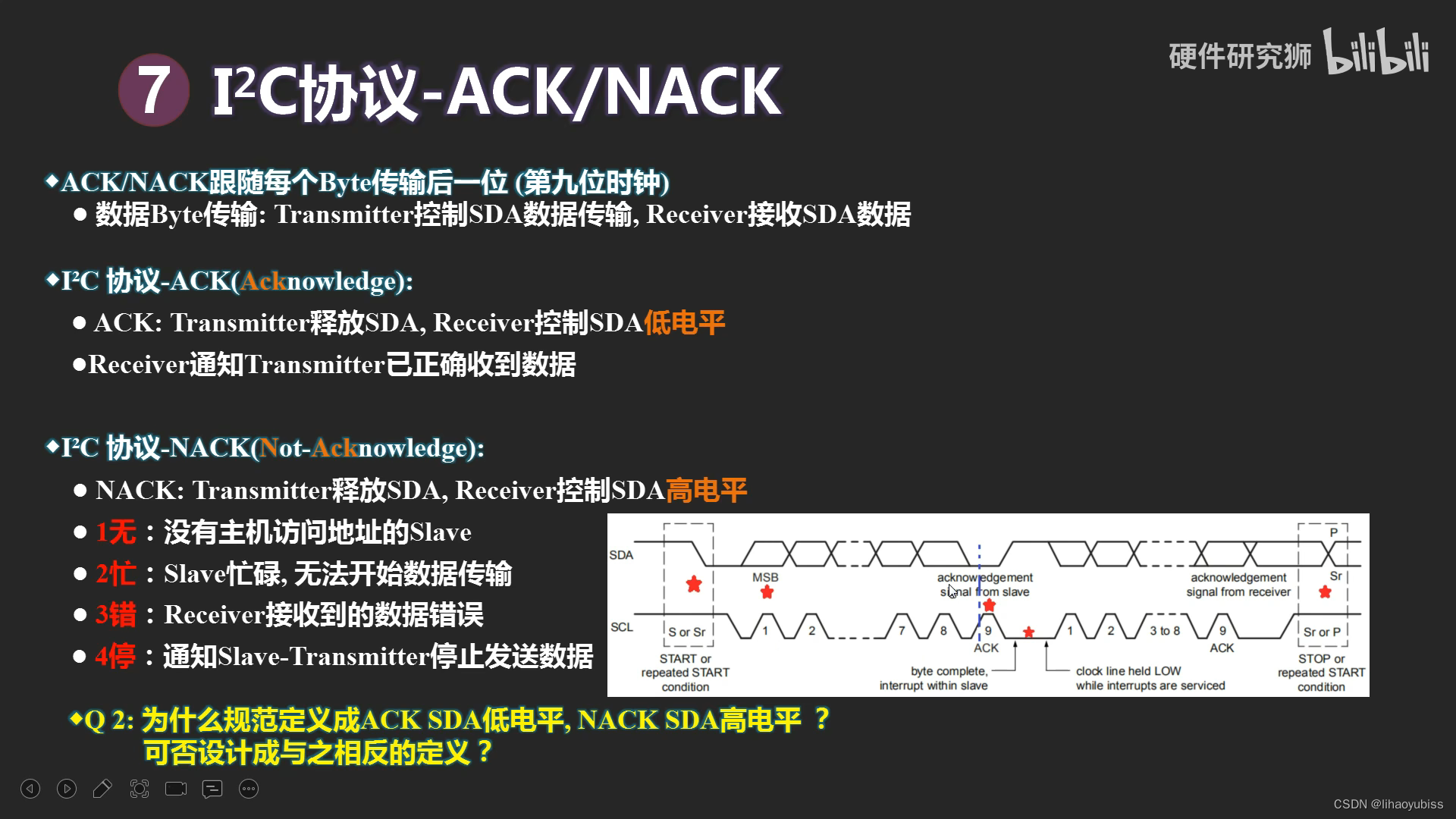

5.ACK/NACK

Transmitter发送8位Byte,Receiver发送应答信号

过程应该是Transmitter发送8位Byte后,数据位由输出变为输入,等待Receiver发送应答信号。

- Receiver发送ACK表示已正确收到数据

- Receiver发送NACK表示出现异常,有以上4种情况。4中从机没有发多少数据的定义,它会一直发一直发,直到主机发送NACK后停止发送。

A2:不能设计成相反,因为默认idle状态就是高电平,应答的时候必须和idle 或者 外部设备不在等情况下有差异才能确认数据传输正常。即正常继续传输需要拉低电压,异常则放弃控制由上拉电阻拉高电平。

6.时钟同步 (SCL)

同一总线上有多个Master同时访问Slave,即有多组CLK信号,进行竞争,即利用SCL时钟线的OC/OD线与结构进行仲裁。

- 当所有CLK信号都为高时,SCL置高(线与)

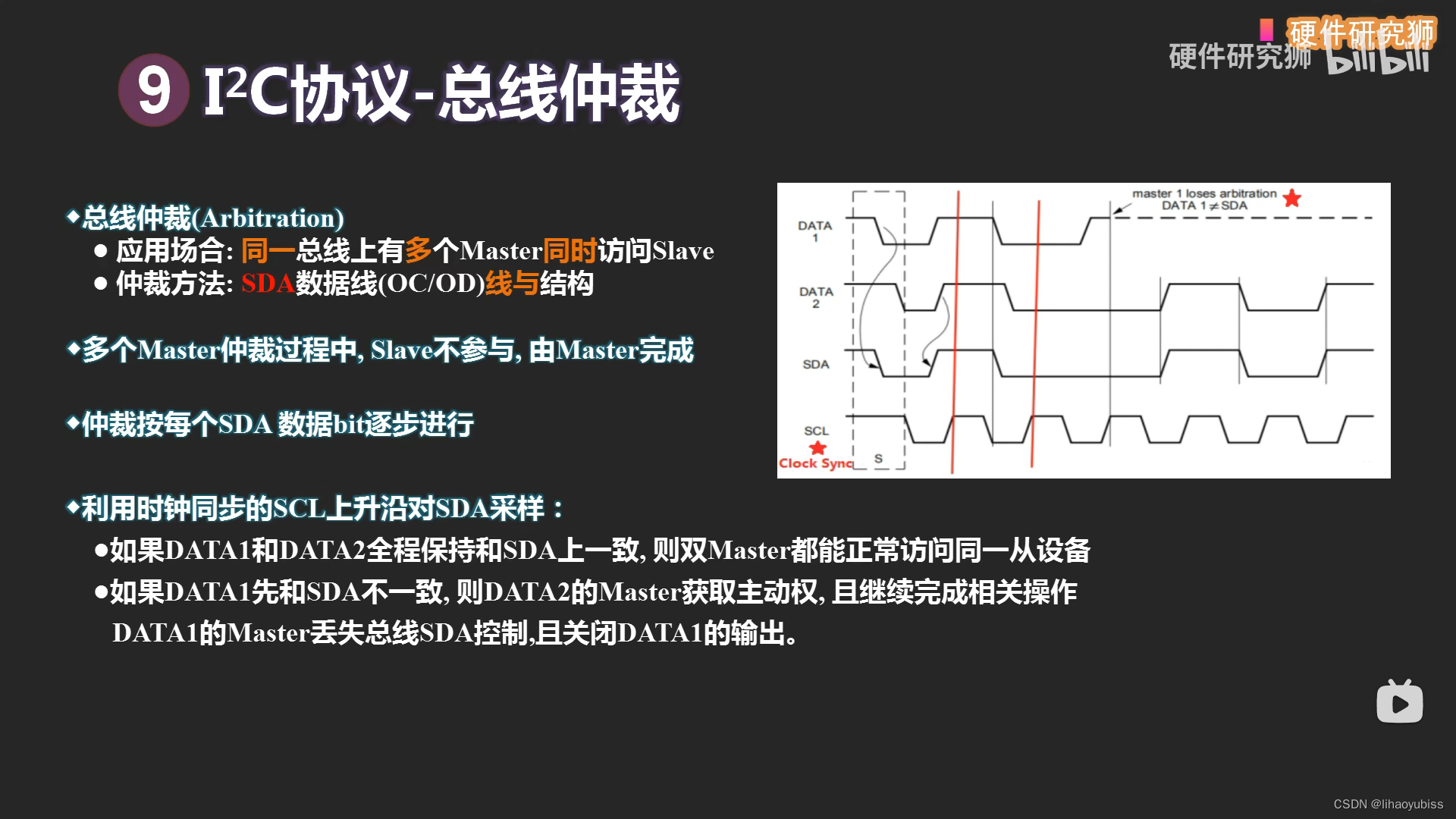

7.总线仲裁(SDA)

- 多对一时发生,由Master完成,Slave不参与。利用SDA时钟线的OC/OD线与结构进行仲裁。

- 仲裁按每个SDA数据bit逐步进行。规则为:谁先与SDA上电平不一致,谁放弃总线控制权。(谁先高谁放弃)

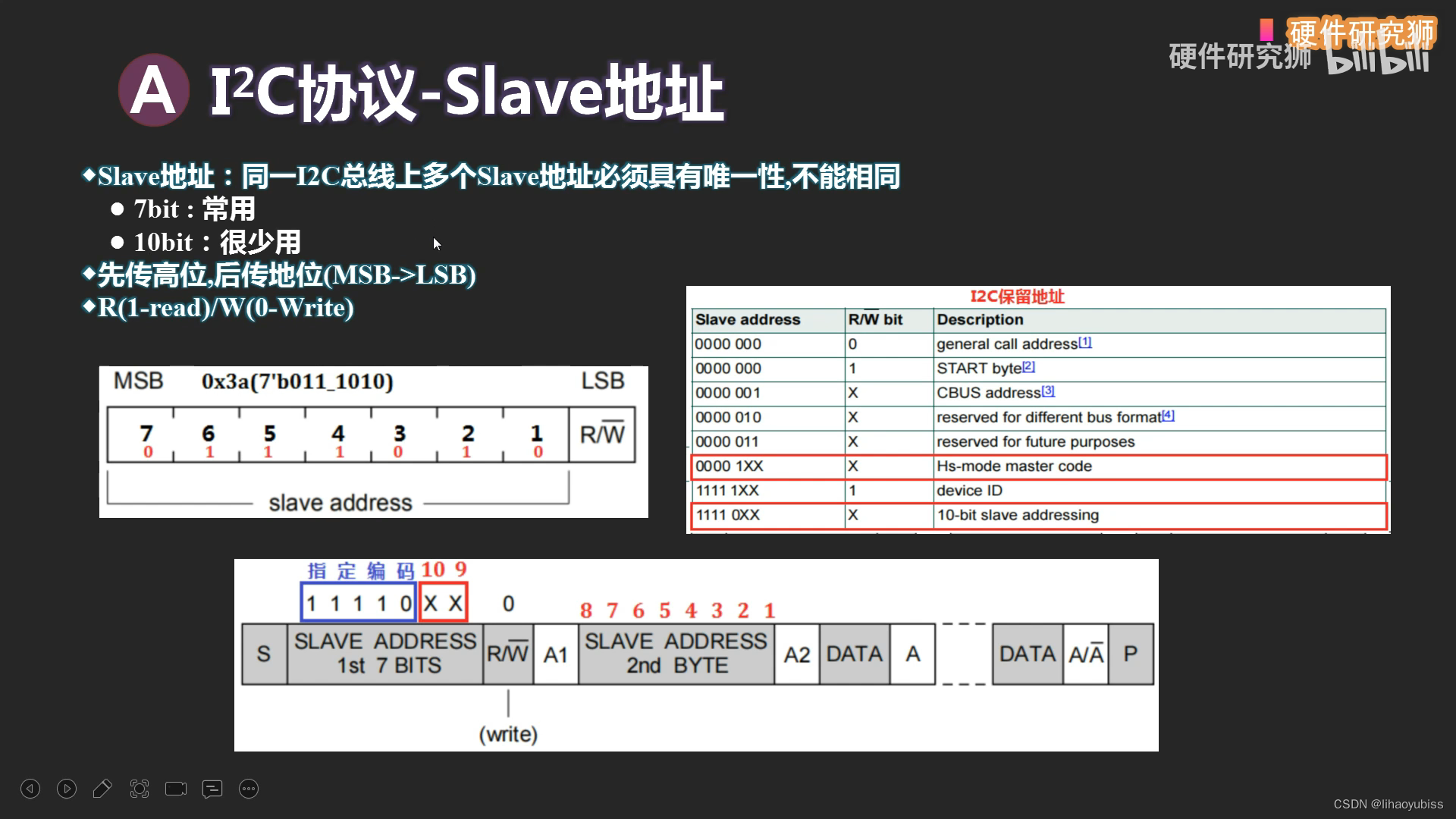

8.Slave地址

- 每个Slave地址唯一

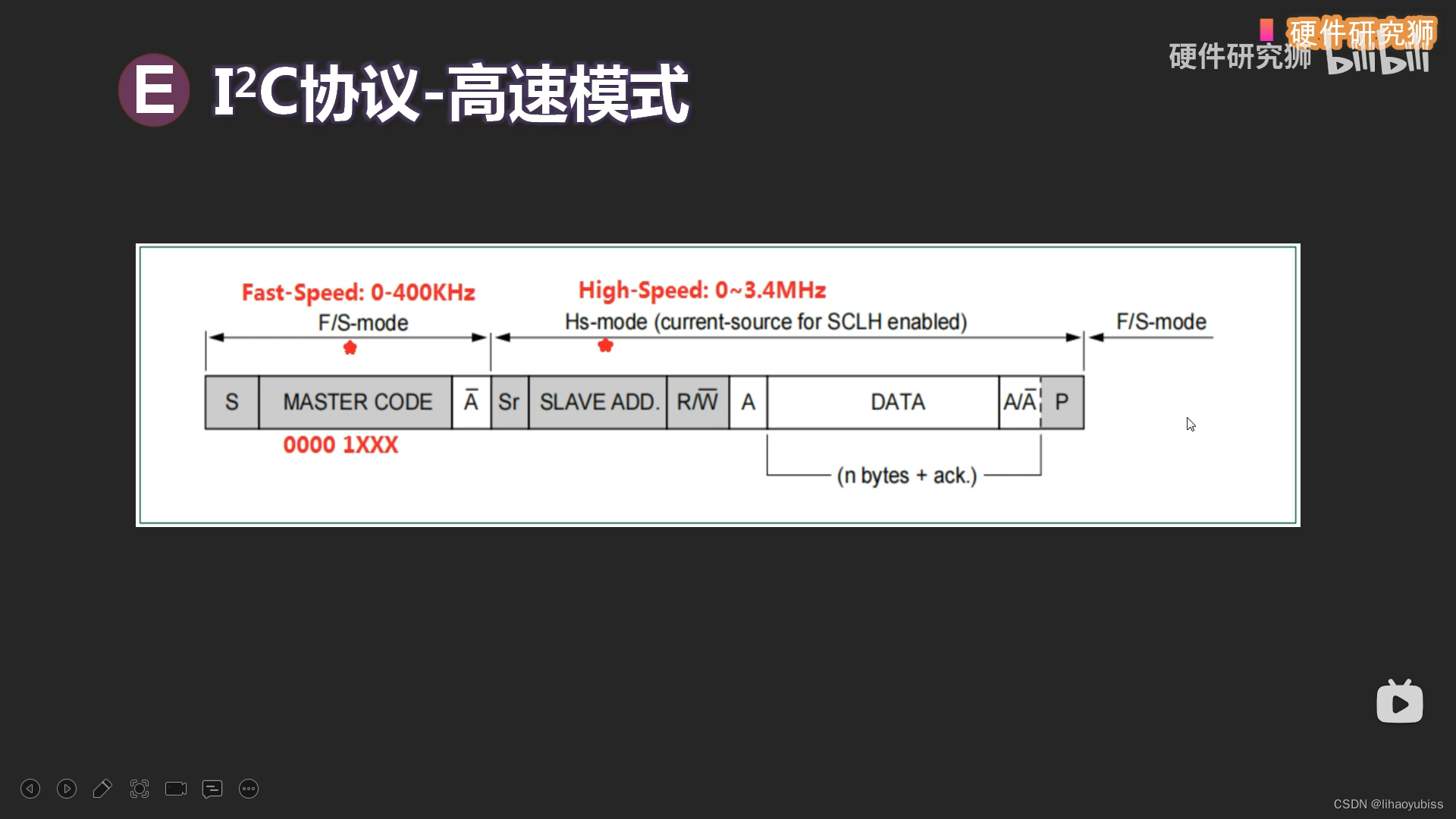

- 0000-1xxx:高速模式

- 1111-0xxx:10bitSlave地址

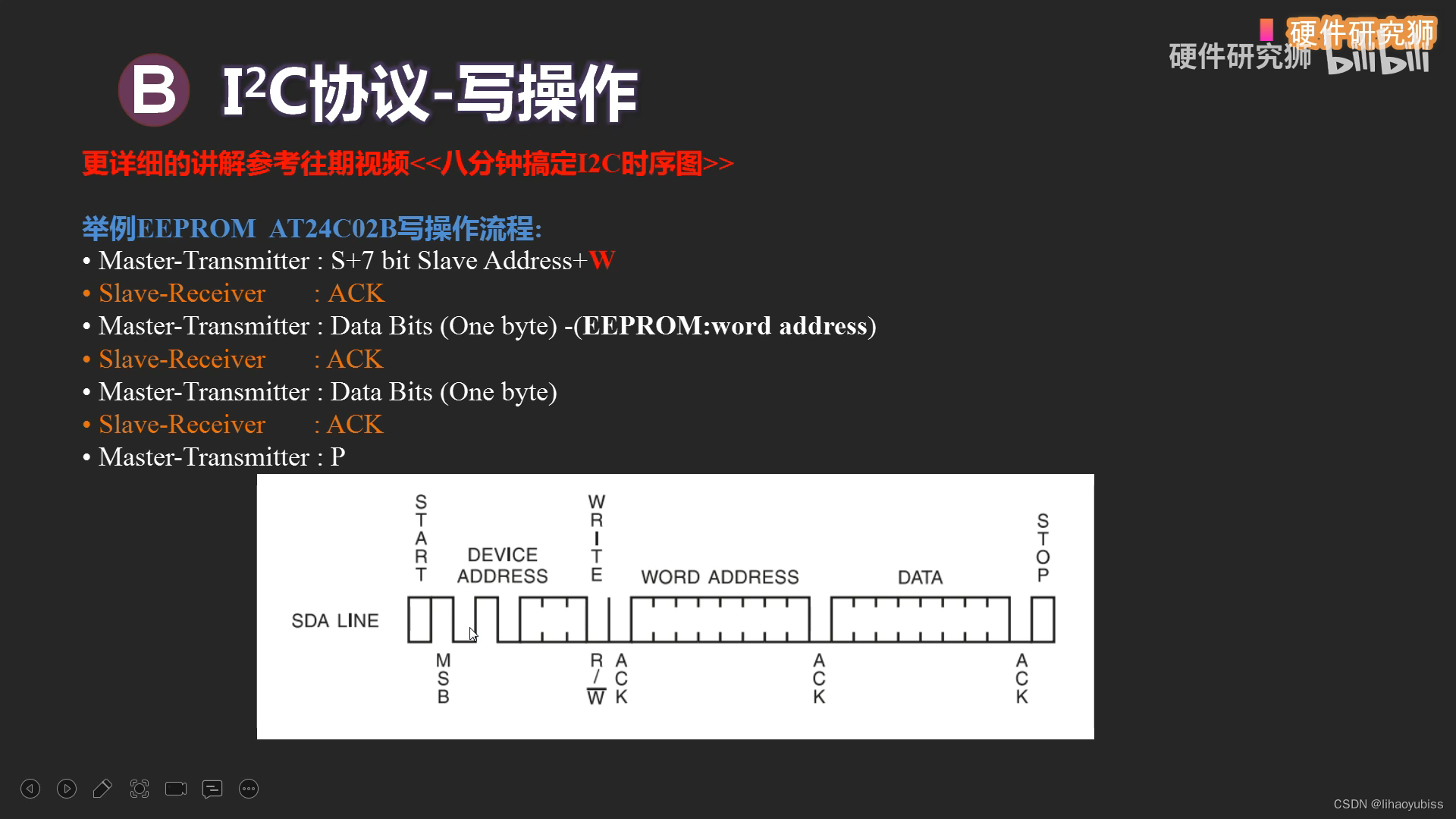

9.写操作

1.M:S+7bitSlave地址+W

2.S:ACK

3.M:8bit寄存器地址

4.S:ACK

5.M:8bit储存内容

6.S:ACK

7.M:P

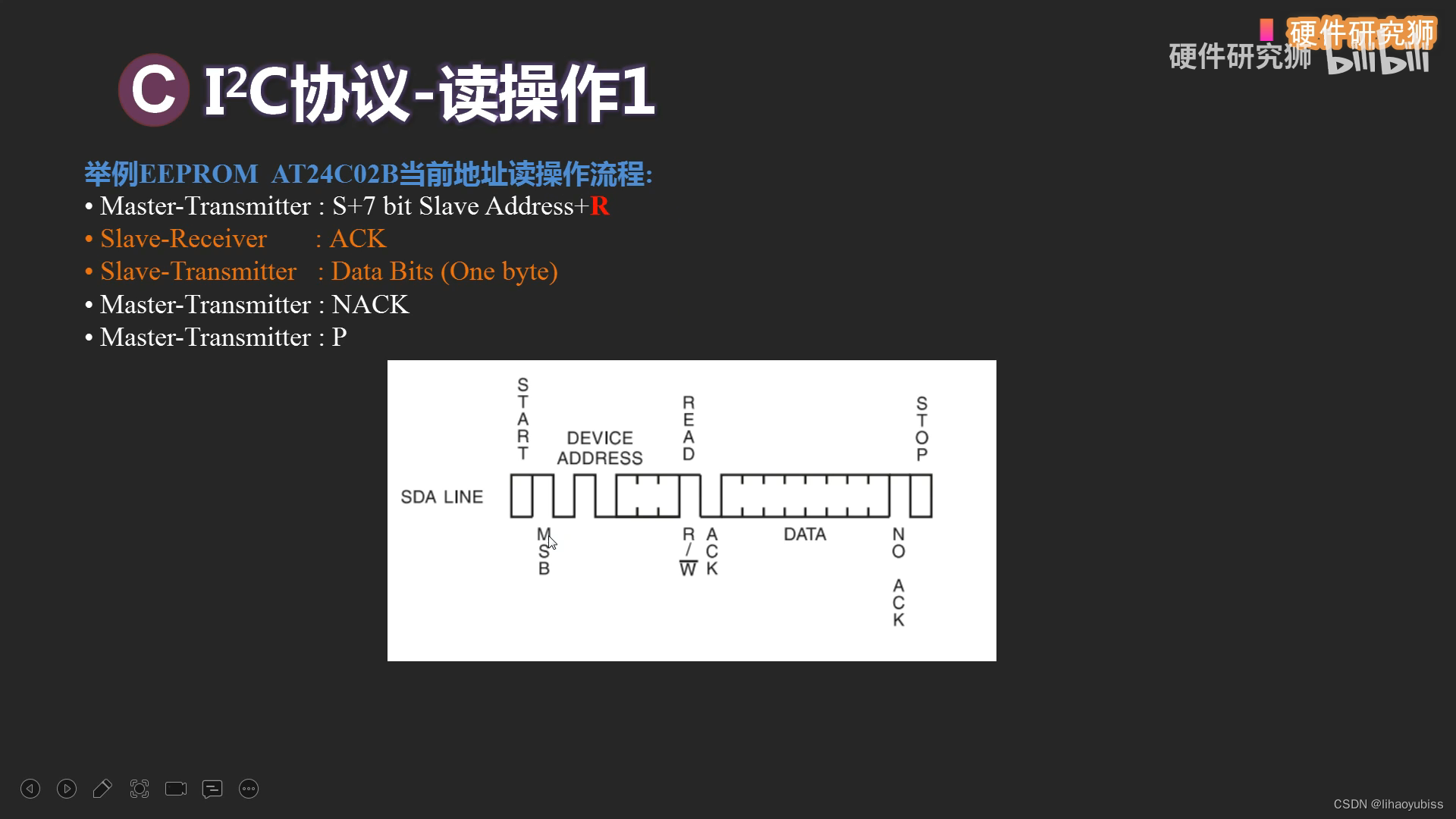

10.1读操作(当前地址)

1.M:S+7bitSlave地址+R

2.S:ACK

3.S:8bit储存内容

4.M:NACK(只需读取1Byte,让Slave停止发送)

5.M:P

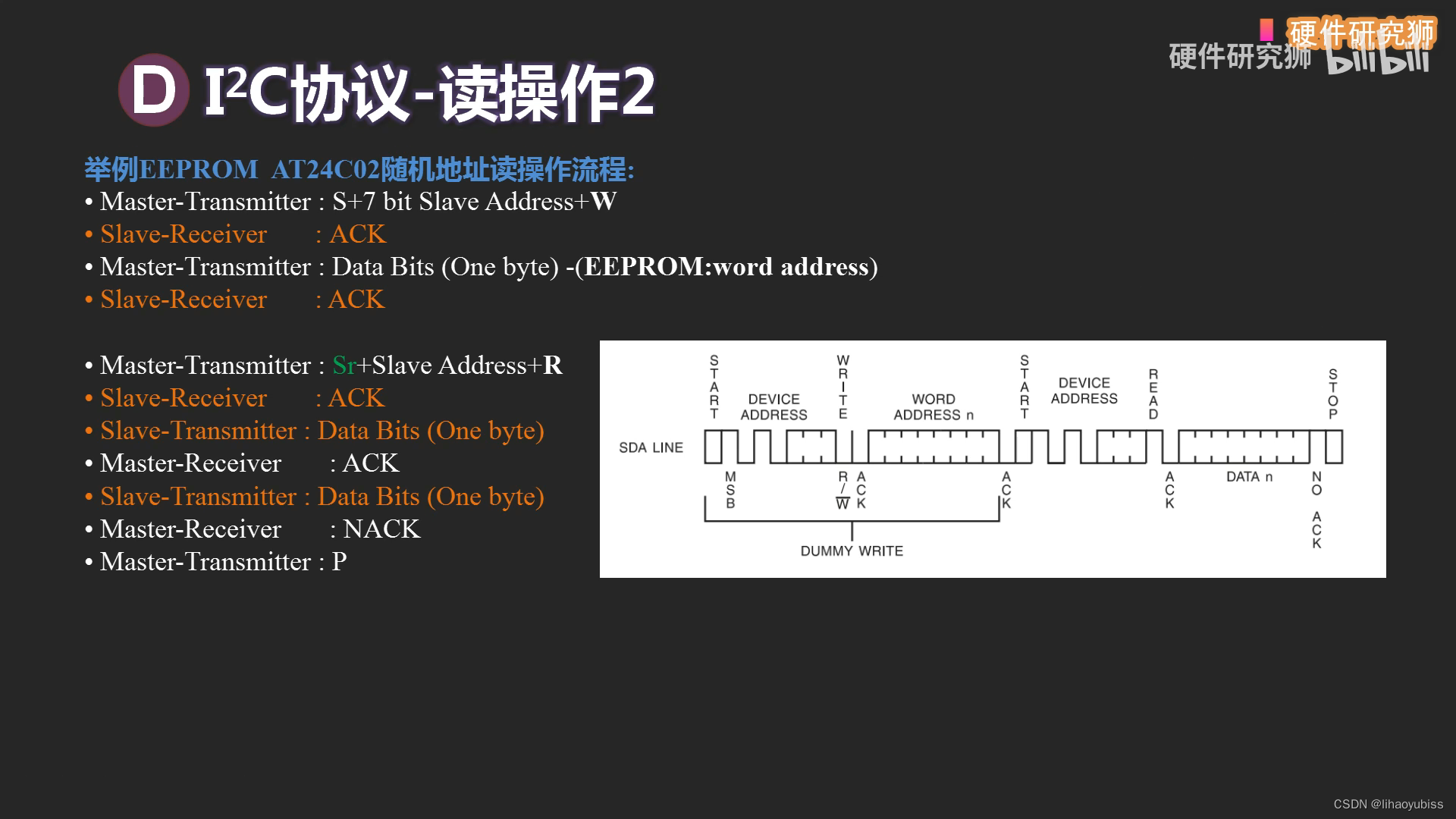

10.2读操作(指定地址)

1.M:S+7bitSlave地址+W

2.S:ACK

3.M:8bit寄存器地址

4.S:ACK

5.M:S+7bitSlave地址+R

6.S:ACK

7.S:8bit储存内容

8.M:ACK

9.S:8bit储存内容

10.M:NACK(只需读取1Byte,让Slave停止发送)

11.M:P

11.高速模式

先发S+0000-1xxx,即切换为高速模式

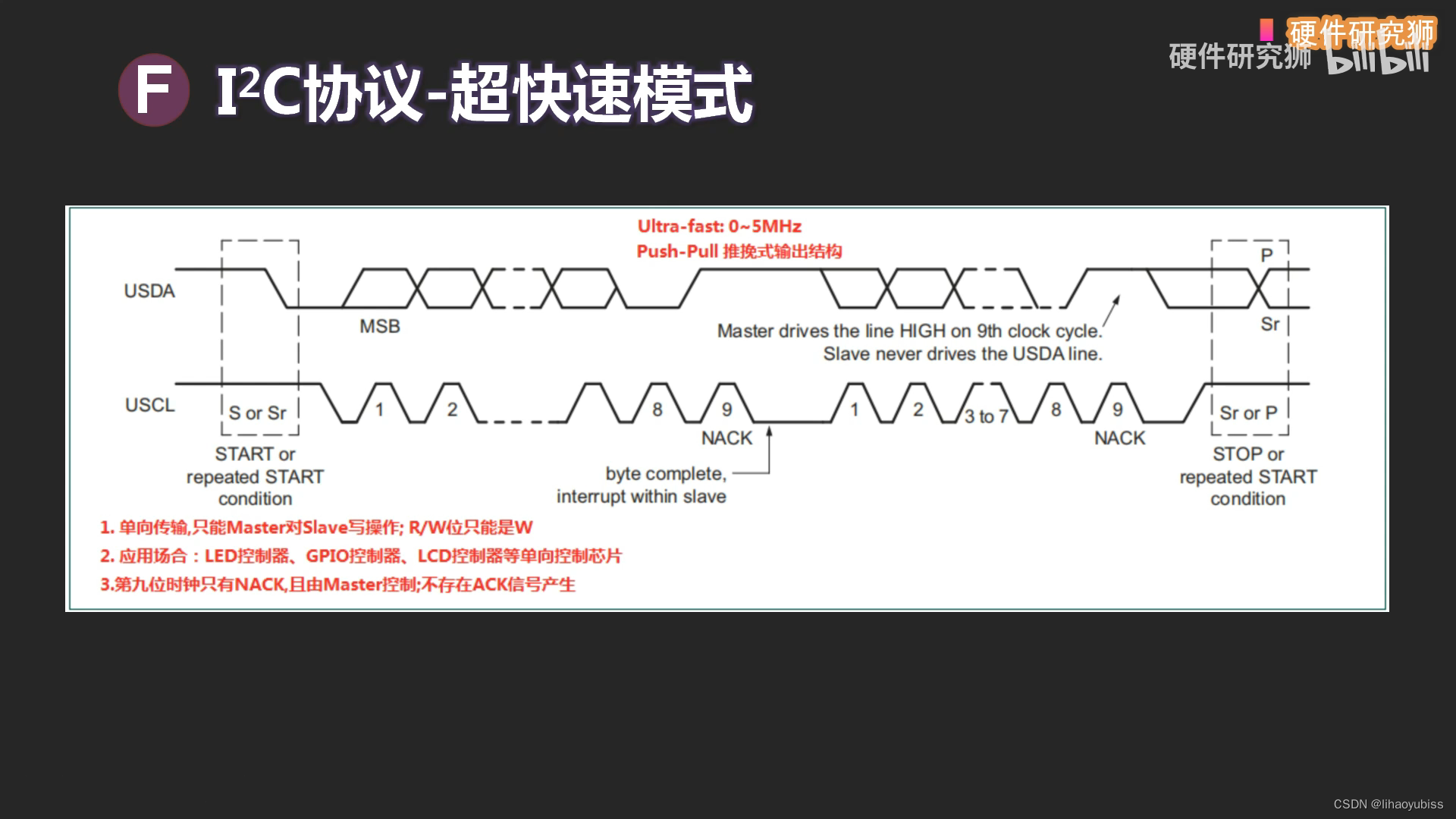

12.超快速模式

- 只能写

- 只有NACK,无ACK

Q:I2C到底是上升沿快还是下降沿快

A:上升沿是通过上拉电阻对寄生电容充电实现,下降沿是通过i2c设备内部晶体管放电,所以下降沿快。

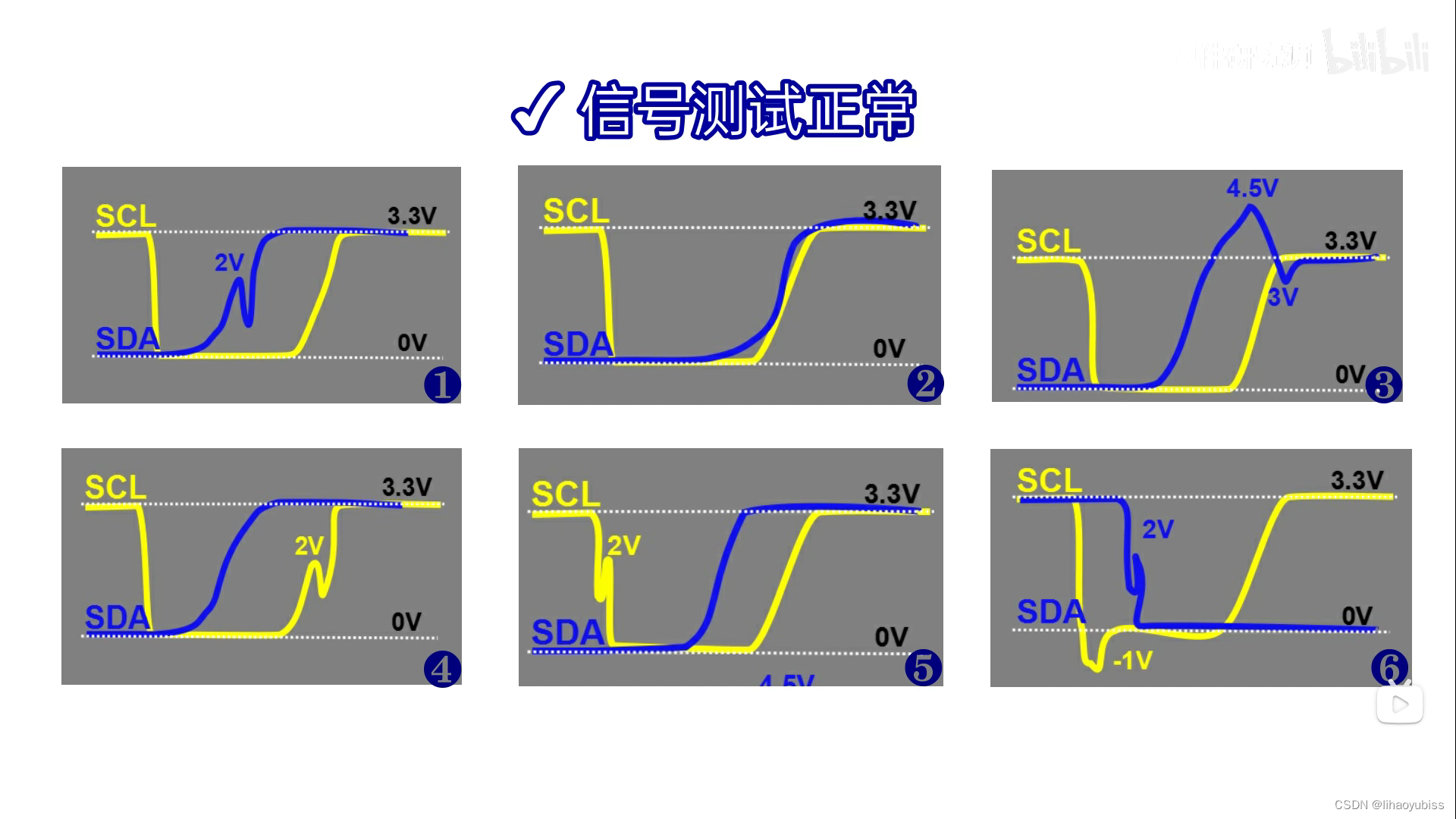

13.IIC信号稳定性测试

1.无影响,可正常工作

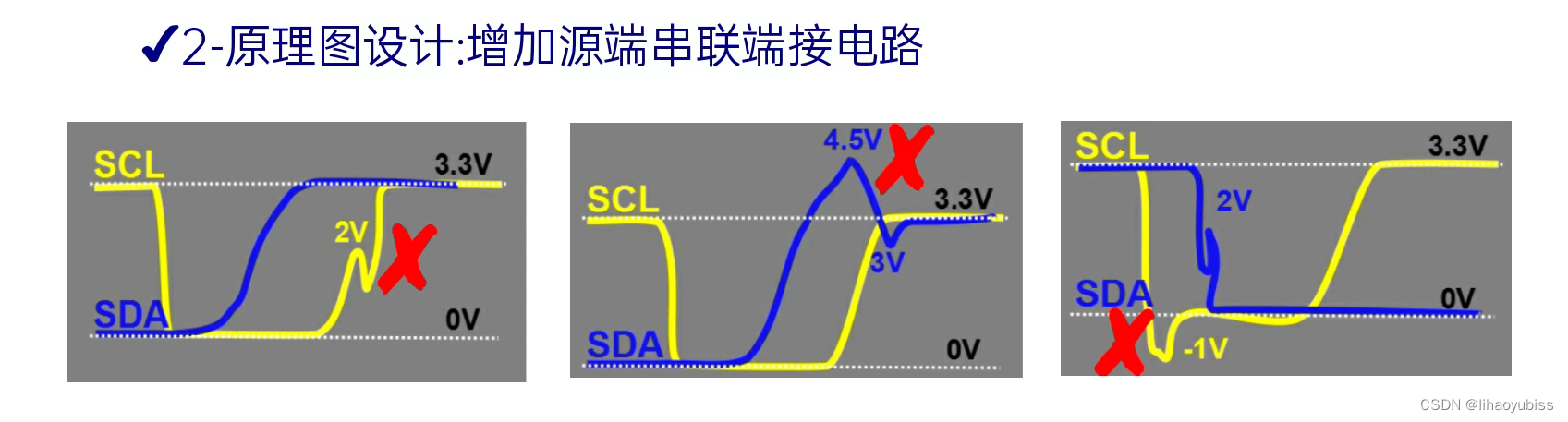

2.SCL和SDA波形接近、重叠,SDA建立时间不满足。影响较大

3/6.SDA/SCL过冲,超过芯片电压工作范围导致芯片工作异常,影响较大

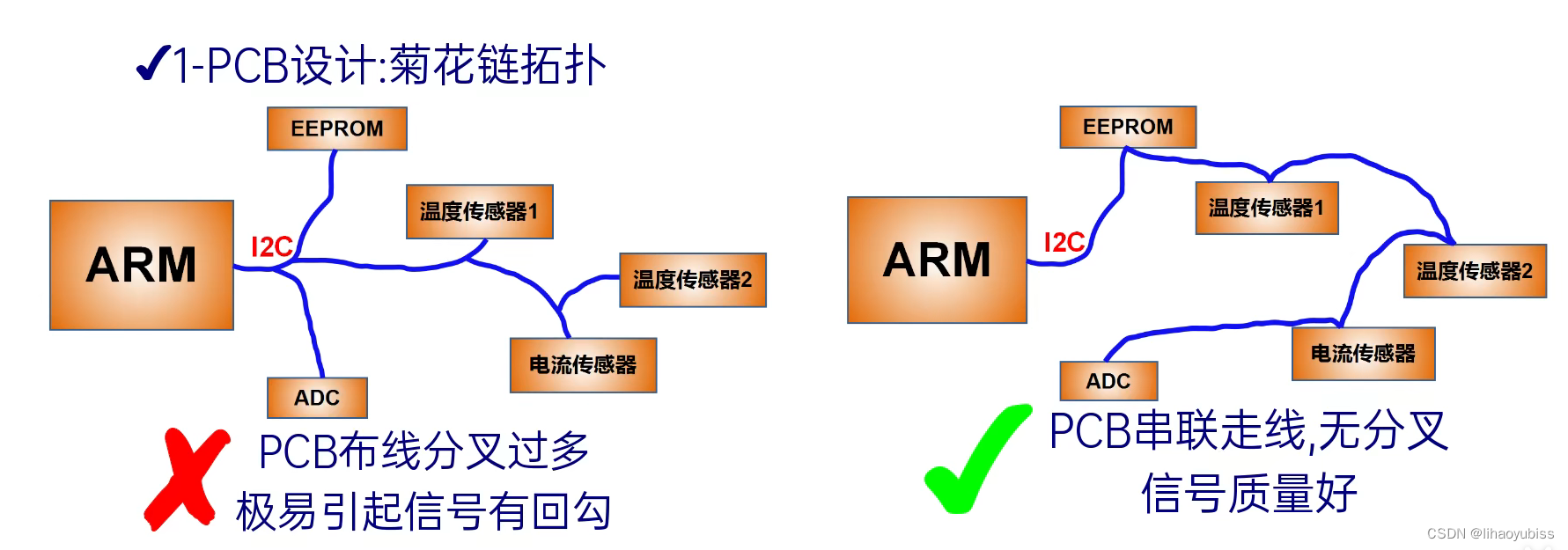

4/5.SCL信号有回钩,有概率导致SCL二次采样,影响较大

信号有回钩

菊花链拓扑,减少走线分叉,回钩就减少了。

信号过冲

源端串联75Ω电阻(类似于mos管栅极串联电阻消振)

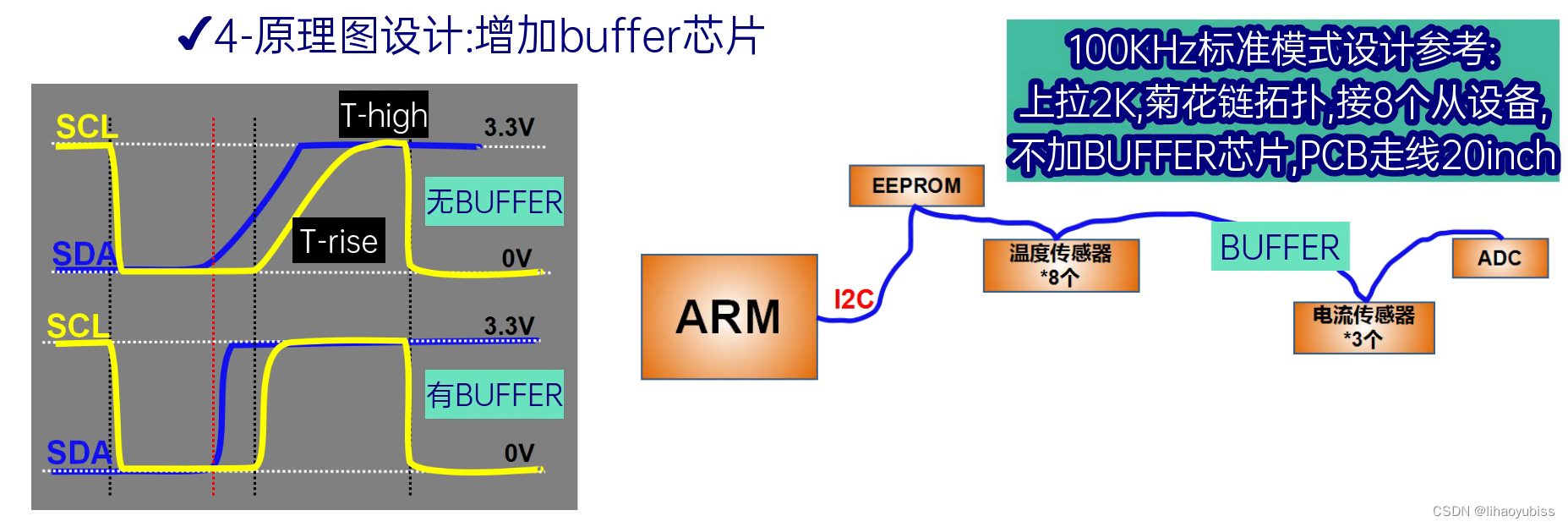

上拉时间过长(建立时间过短)

- 减小走线长度来减少寄生电容,减小上拉电阻来增大充电电流,提高电压跳变速度

- 通过增加buffer芯片来提高上升速度

- 降低IIC工作频率,使得SCL的低电平时间和高电平时间延长,SDA有足够的时间拉高。

14.IIC总线结构(OCOD门-开漏输出)

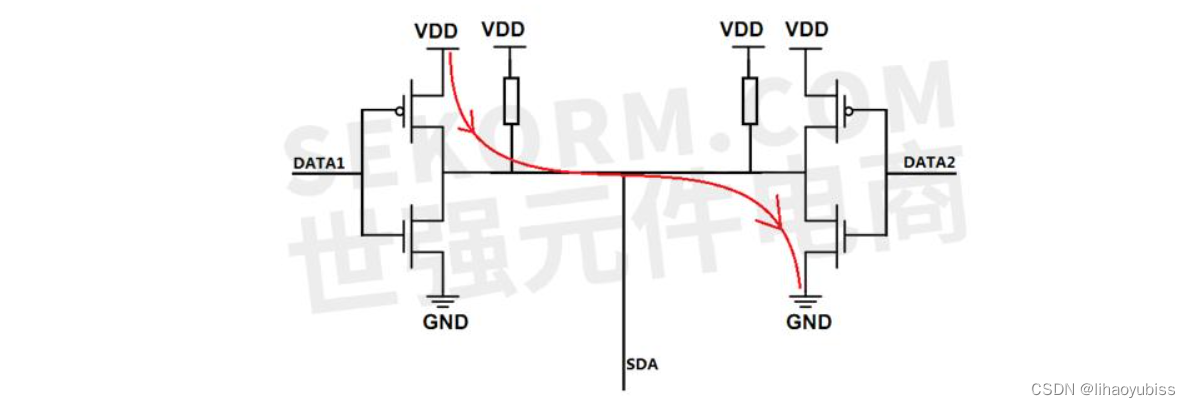

因为外部上拉电阻的存在,电路不存在问题,并且电平状态是可确定的。

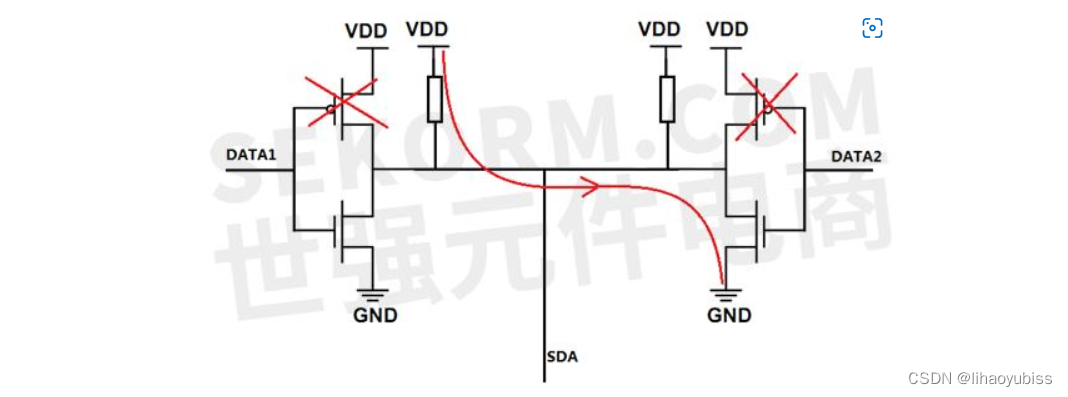

假如将IO配置为推挽,则如下:

当竞争发生时,就会存在短路问题,有烧坏器件的风险。

所以在一个I2C总线上挂载多个设备时,必须将IO配置为开漏模式以保护设备安全运行。

上拉电阻

电源电压决定上拉电阻的最小值,总线负载电容Cbus决定上拉电阻的最大值。

一般取值在1k-10kΩ

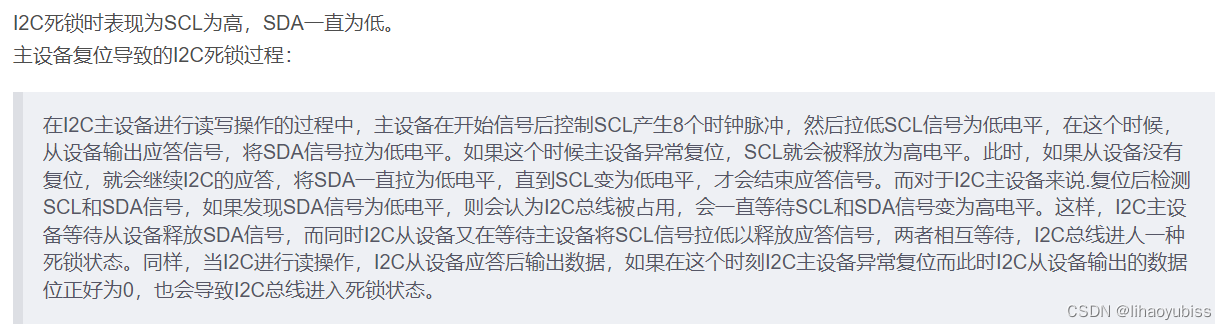

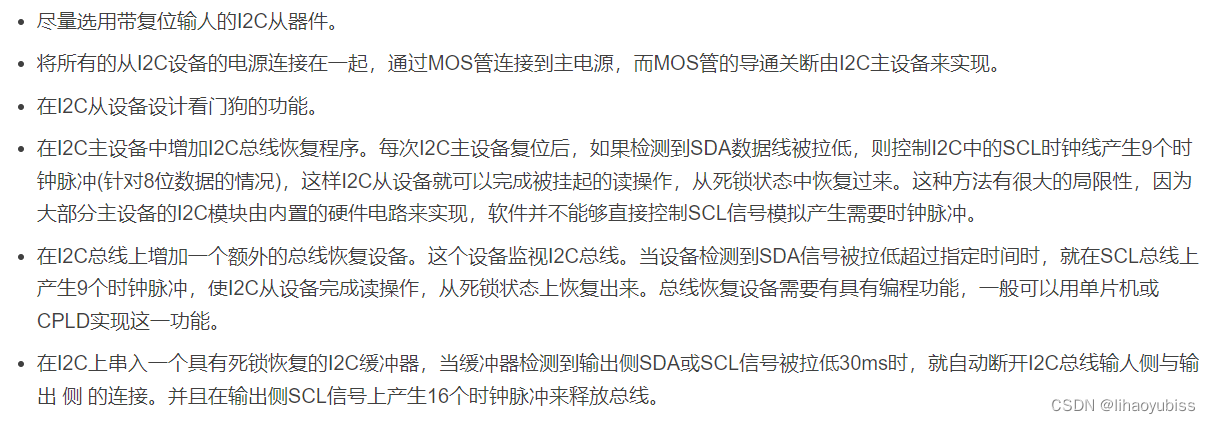

15.IIC死锁

解决方法

二、SPI(串行外设接口)

1.SPI vs IIC

因为SPI无应答机制,所以SPI[主设备]甚至并不知道指定的[从设备]是否存在。即外设掉线了也可以继续使用。(V5oled拔了可继续工作,V6则不行,就是SPI和IIC的区别)

2.常见时钟频率

- SPI不规定最大传输速率

- 当使用Dual SPI、Quad SPI工作时,工作频率分别等效为2倍、4倍

3.常见拓扑

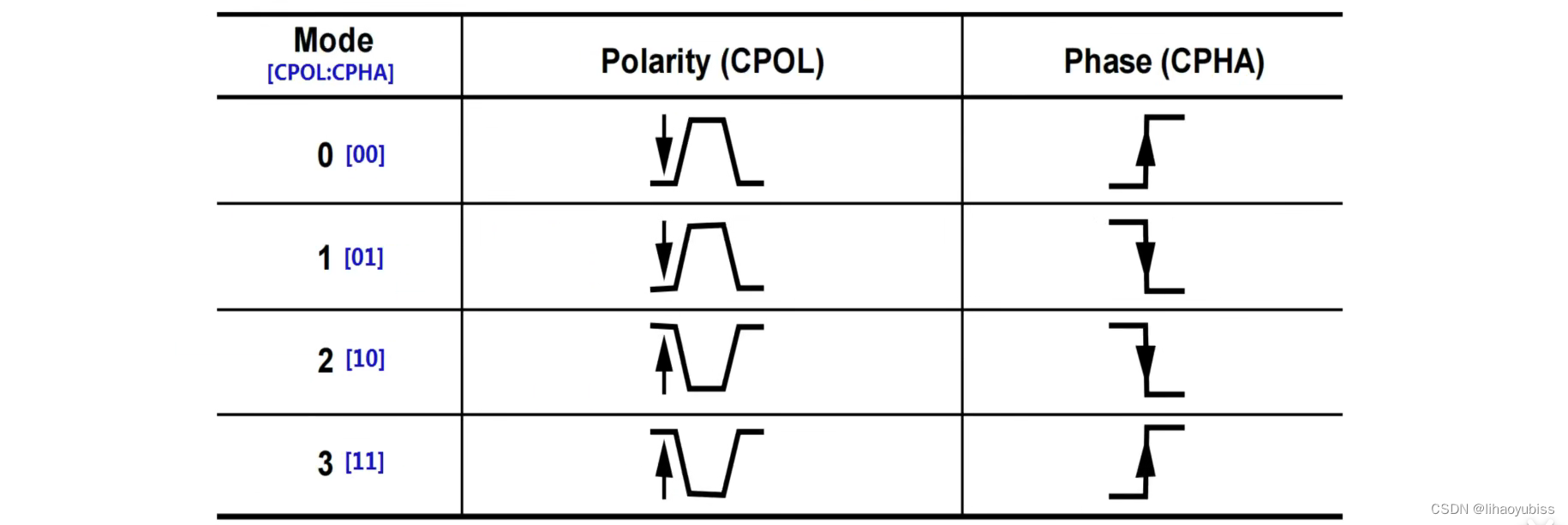

4.4种工作模式

模式0:CPOL为0,总线在空闲时,时钟信号为低电平,CPHA为0,采用时钟第一个边沿对数据进行采样,即该模式下上升沿采样

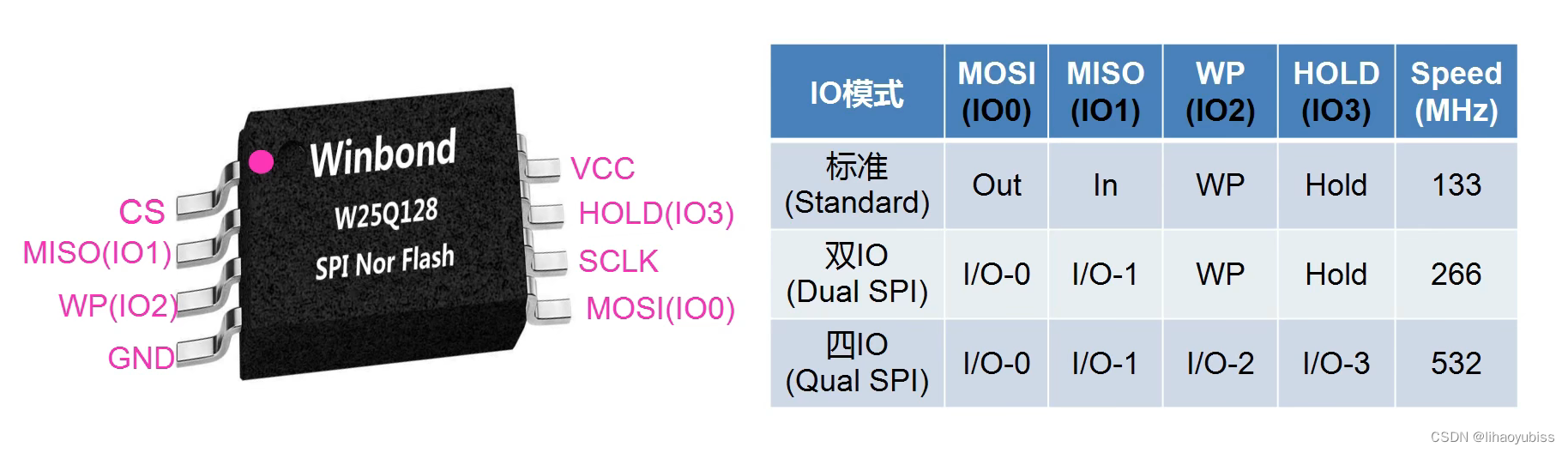

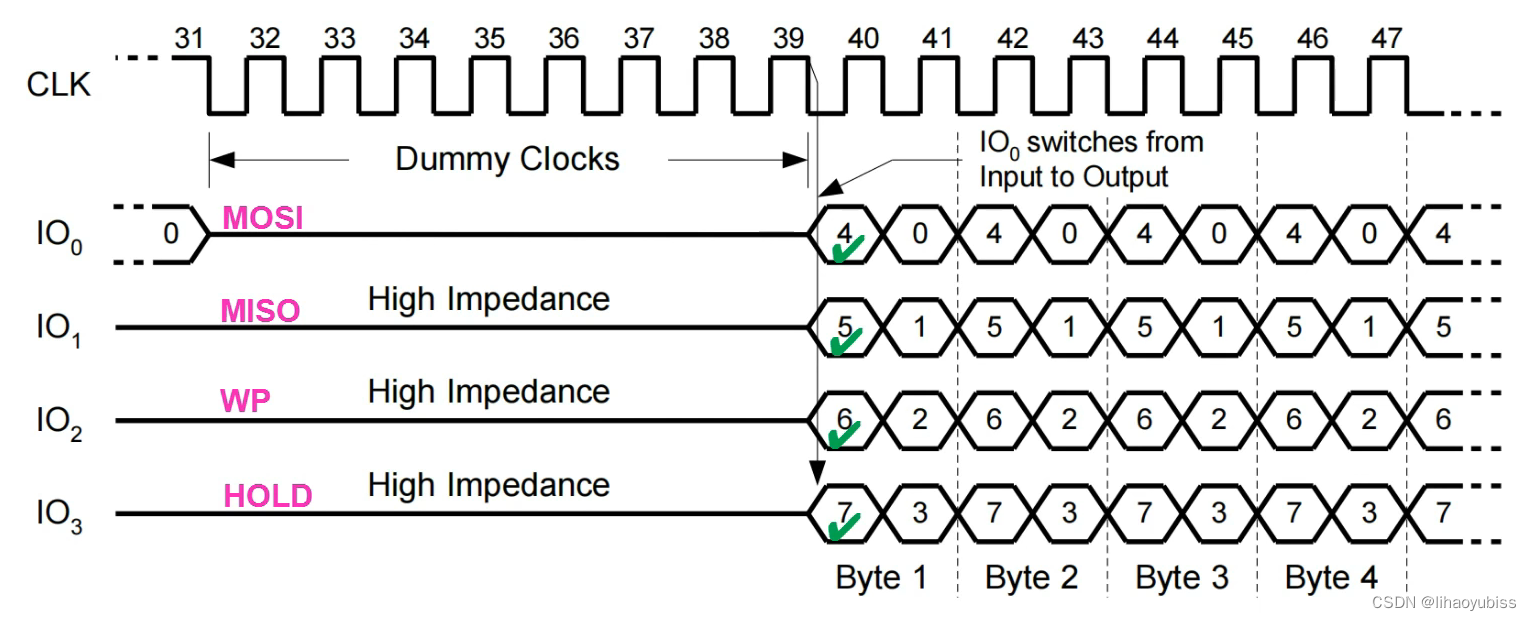

5.Dual SPI、Quad SPI

对于nor flash外设,标准模式下MISO发送数据,MOSI接收数据。Dual SPI下,MISO、MOSI在发送时同时发送,接收时同时接收,所以工作频率翻倍。

Dual SPI:

Quad SPI:

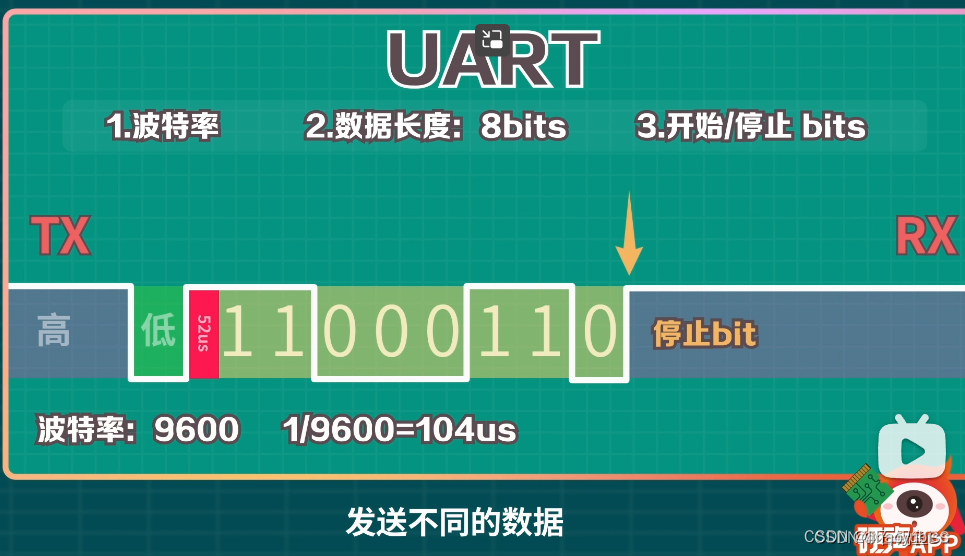

三、UART(通用串行数据总线)

- UART (通用异步收发器 、USART(通用同步异步收发器,比uart多了根时钟线。使用异步时与uart一样。

- 开始条件,发送逻辑0信号;停止条件,发送逻辑1信号

三个需要注意的参数(都可以修改)1)数据长度 2)起始\停止位 3)波特率

- UART传输的数据被组织成数据包。每个数据包包含1个起始位,5到9个数据位(取决于UART),可选的奇偶校验位以及1或2个停止位:

- 波特率:可以理解为时钟频率,9600波特率代表每秒读9600次,每个比特位持续时间就是1/9600秒,波特率一样时才能通信

1637

1637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?