目录:

一、相序错误保护

1、电路原理图

2、工作原理

二、三相缺相保护

1、工作原理

2、电路设计说明

3、实验结果

一、相序错误保护

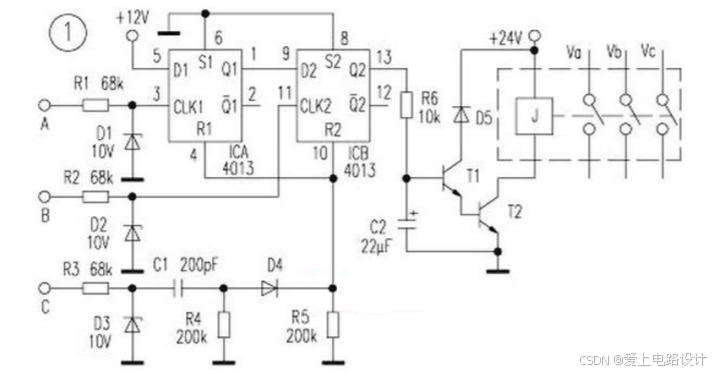

1、电路原理图

2、工作原理

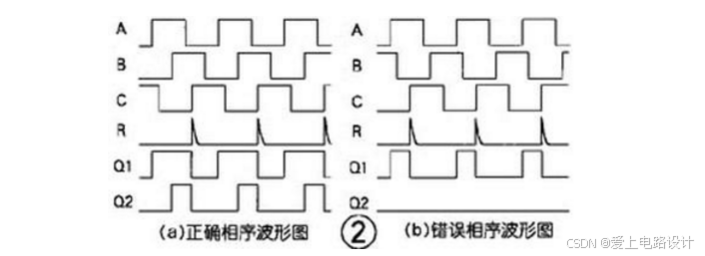

该电路主要由一片CD4013双D触发器构成。三相交流电经降压、整流后变换为低压脉冲信号输入到本电路的A、B、C端,A、B两端信号经过电阻和稳压二极管限幅、整形后,分别作为两个D触发器的时钟信号,C端信号经微分电路变为尖脉冲作用于两触发器的复位端R。

若相位顺序正确,即以 A、B、C的顺序出现正脉冲,如图 2(a)所示,则A的上升沿首先使 Q1 输出高电平,然后Q2在B的上升沿作用下变为高电平,最后C的上升沿在R端产生的尖脉冲使两个D触发器复位,Q1、Q2回到低电平,完成一次循环。

三相交流电是周期信号,Q2输出脉冲的频率与三相交流电频率相同,其电压的直流分量就是 C2(22uF)电容上的电压。该电,压使三极管导通,继电器接通用电设备的三相电源。若相序不对,则Q2输出保持低电平不变,三极管截止,保证了用电设备的三相交流电源不被接通。各点观测波形如图 2(b)所示。

二、三相缺相保护

1、工作原理

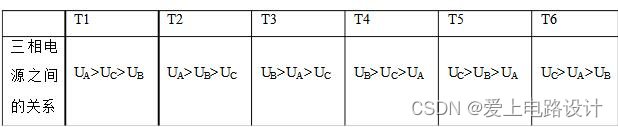

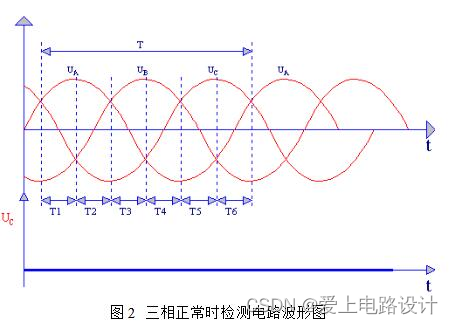

当三相输入电压正常时,其三相输入相电压波形如图2所示,为便于分析,将一个电源周期分为6等份,如图2所示T1、T2、T3、T4、T5、T6。在这六个区间,三相电源之间的关系如表1所示:

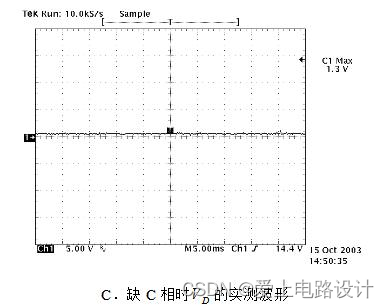

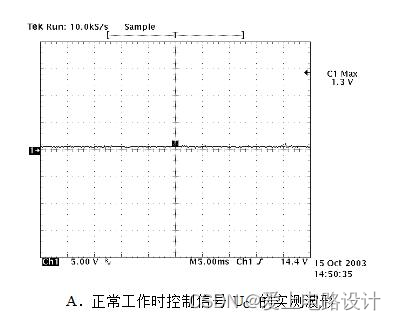

在区间T1内,UA > UC > UB ,A相电压最大,B相电压最小,因此,在图1中的光藕D1和二极管VD5导通,此时,控制信号UC为低电平,当时间从T1进入T2区间时,UA > UB > UC ,A相电压最大,C相电压最小,因此,在图1中的光藕D1和二极管VD4导通,控制信号UC为低电平,如此类推,在区间T3、T4、T5、T6时,控制信号UC均为低电平,所以,在一个电源周期内,控制信号UC为低电平,也就是说,当三相输入电压正常时(不缺相),控制信号UC一直为低电平,从而使缺相告警信号PHFL为低电平,表示输入正常。

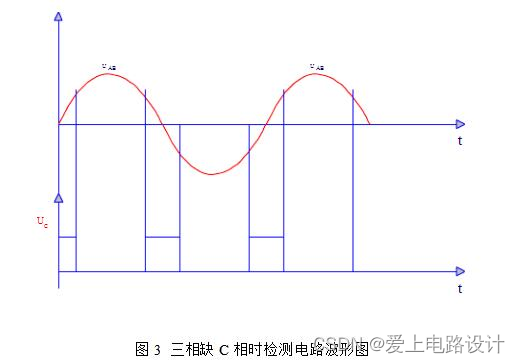

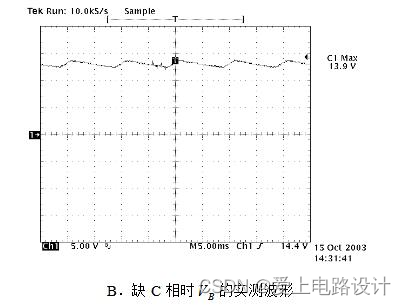

当三相输入电压缺相时,其检测电路波形图如图3所示,

由于缺C相时,线电压只有UAB一相,当UAB在过零点附近时,光藕D1不导通,其余二个光藕也不导通,此时,控制信号UC为高电平,从而使缺相告警信号PHFL为高电平,表示输入缺相,送ECU处理。

2、电路设计说明

1) 控制信号VC的计算

图1中,各点电压说明如下:

VA:光藕输出;VB:电压比较器LM339第4脚输入;VC:三极管VT1基极控制信号;VR:所有比较器的比较电压基准。光藕TLP621GR的电流传输比CTR取最小值,即CTRMIN = 100%。 电压基准VR为:

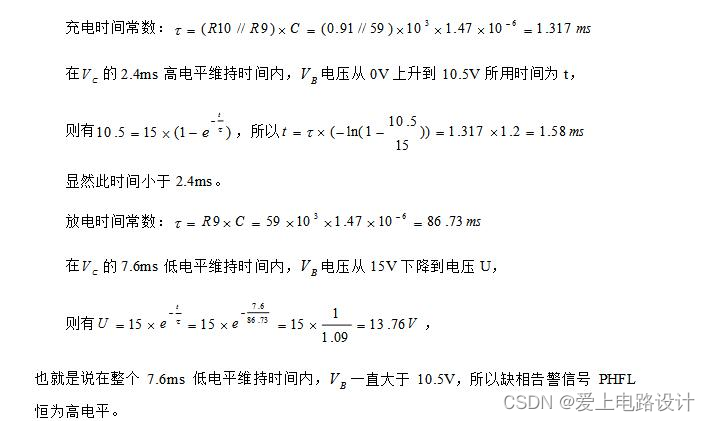

2)充放电回路分析计算

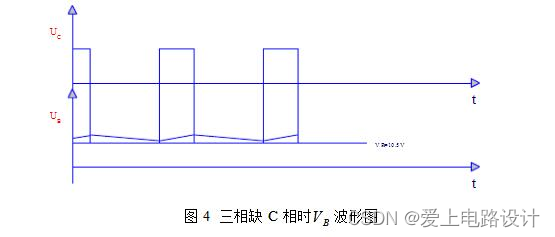

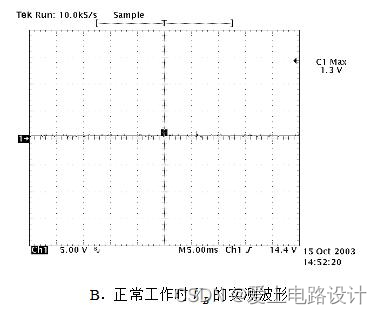

充放电回路由电阻R9、R10、VT2、C10、C11组成。当控制信号CV为高电平时,三极管VT1、VT2导通,+15V电源通过电阻R9、R10给电容C10、C11,当控制信号CV为低电平时,三极管VT1、VT2截止,电容C10、C11通过电阻R9放电,显然,BV实际上为一个直流电压迭加一个脉动信号,只要BV的波不小于10.5V,则电压比较器LM339的第2脚输出就一直为低电平,缺相告警信号PHFL为高电平,表示三相输入缺相。波形见图4。

3、实验结果

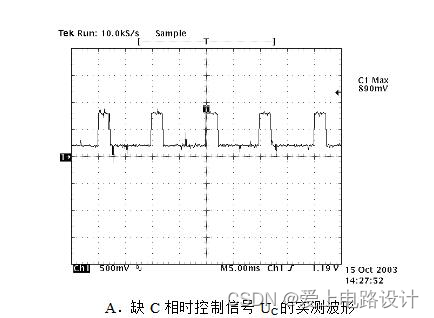

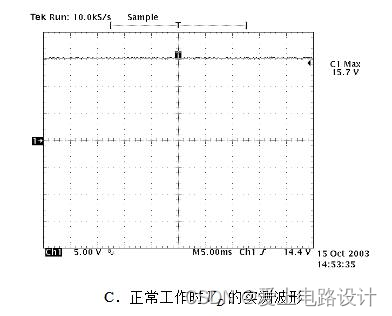

这次实验是在ZXD5000 100A(V2.0)开关整流器上进行的,缺相工作和正常工作时的测试波形如下图所示:

鹏北海,凤朝阳。又携书剑路茫茫。觉得不错,动动发财的小手点个赞哦!

8279

8279

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?