作者:罗宇哲,中国科学院软件研究所智能软件研究中心

上一期中我们介绍了ARMv8-A架构中的地址转换机制和访问控制机制,这一期我们将考察ARMv8-A架构中的应用级内存模型(Application Level Memory Model)。

一、ARMv8-A架构的应用内存模型

应用级内存模型指的是从应用软件的视角来观察和操作处理器的内存行为而形成的模型。ARM v8-A 架构中的内存主要有两种类型:

- Normal类型:对该种类型的内存可以进行常见的读写操作或只读操作,系统中大部分内存都是这种类型;

- Device类型:对该种类型的内存进行读写可能具有连带效应(side-effects,指对一个内存位置的读写操作会影响其它内存位置)或者从该种内存中的一个位置装载的值可能随着装载的次数而变化。通常内存映射外设(指使用访问内存的方法来访问的外设)会采用这种内存类型。

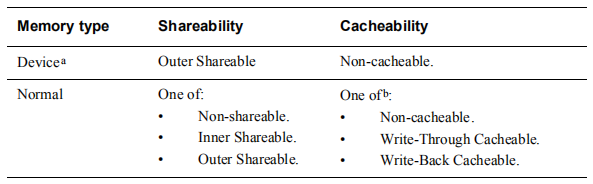

Normal类型和Device类型的内存有不同的内存属性[2]:

上表中Shareability是与一致性有关的内存属性,用来指示一个内存位置对于一些处理器是否是可共享的。共享意味着需要硬件保证一个内存位置中的内容对一定范围内可访问该位置的多个处理器是一致。Shareability属性有Non-shareable、Inner Shareable和Outer Shareable三个选项,其含义为:

- Non-shareable:该内存位置一般只能被唯一处理器访问,如果还有其他处理器能访问该位置,可能需要软件用缓存一致性指令

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8862

8862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?