46 上升沿检测

题目描述

在实际应用中,我们经常需要对某个信号的边沿进行检测,并以此作为后续动作的触发信号(例如电脑键盘的某个按键被按下或者被松开,在电路中则对应的是电平的变化)。

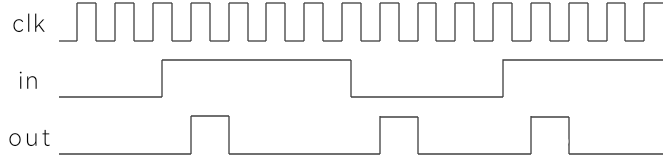

设计一个电路,包含clk信号、1bit输入信号in和1bit输出信号out,当in信号从0变为1时(相对于clk,该信号变化频率很慢),out信号在in信号上升沿附近输出1个时钟周期的高电平脉冲,其余时刻都为0,如下图所示

提示:如果在top_module中定义了reg,且out的结果与reg相关,可以想象,在仿真的开始阶段,reg的值是未定义的,那么out的波形也是未定义的,为了避免此情况的error, 可以使用initial初始化这些reg, 使初始的out 为0

输入格式

时钟clk, 被检测信号1bit in

输出格式

检测结果 1bit out

module top_module(

input clk,

input in,

output out);

reg q1,q2;

assign out = q1 & ~q2;

initial

begin

q1 =0;

q2 =0;

end

always @(posedge clk) begin

q2 <= q1;

q1 <= in;

end

endmodule47 双边沿检测

题目描述

根据上升沿检测的思路,设计一双边沿检测电路,即在输入信号的上升沿和下降沿附近时刻,各输出一个高电平脉冲,如下图所示

输入格式

1位时钟信号clk和1位输入信号in

输出格式

一位信号out

module top_module (

input clk,

input in,

output out

);

reg q1,q2;

assign out = (q1&~q2)|(~q1&q2);

always @(posedge clk) begin

q2 <= q1;

q1 <= in;

end

endmodule48 计数器

题目描述

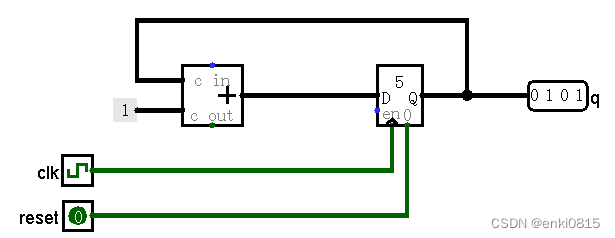

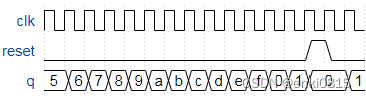

计数器是一种比较简单且常用的时序逻辑电路,下面电路图是一个从0到15循环计数的累加计数器,每个时钟的上升沿计数值加一,采用异步复位方式,高电平有效,复位值为0,该电路是由一个4bit加法器和一个4bit寄存器构成,波形如下所示。

试编写Verilog代码,完成上述电路功能。

输入格式

时钟clk,异步复位信号reset

输出格式

4位的计时器q

注意:这题需要clk和reset判断

module top_module (

input clk,

input reset, // 异步复位,高电平有效,复位值为0

output reg [3:0] q);

// your code

always @(posedge clk or posedge reset) begin

if(reset)

q <= 0;

else

q <= q+1;

end

endmodule49 十进制计数器

题目描述

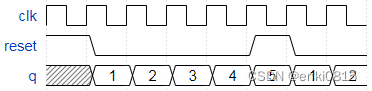

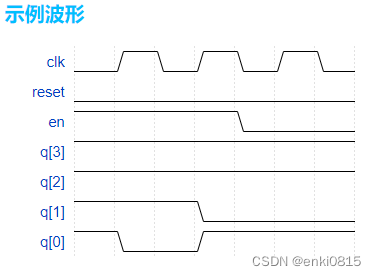

设计一个十进制计数器电路,从1到10循环计数,采用同步复位方式,高电平有效,复位值为1,如下面波形图所示

输入格式

一位线网型变量clk,时钟信号; 一位线网型变量rst,复位信号

输出格式

三位寄存器信号q, 计数器结果

module top_module (

input clk , //时钟信号

input reset , //同步高电平有效复位信号

output reg [3:0] q //计数结果

);

// 请用户在下方编辑代码

always @(posedge clk) begin

if(reset)

q <= 1;

else if( q==4'd10)

q <= 1;

else

q <= q+1;

end

//用户编辑到此为止

endmodule

50 带使能的计数器

题目描述

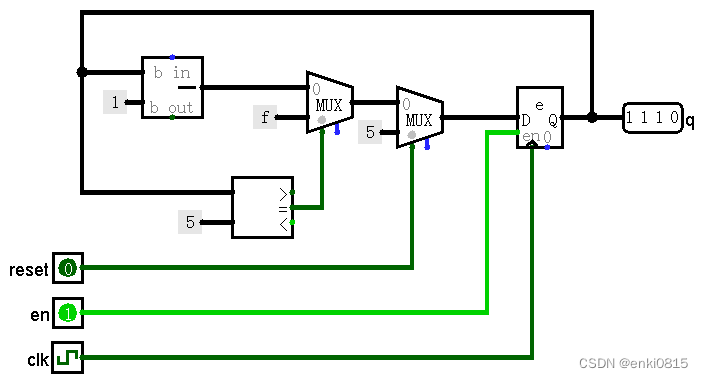

创建一带有使能信号的递减计数器,当使能信号有效(高电平)时,从15到5循环递减计数,每个周期减1,使能信号无效时,计数值保持不变,电路采用同步复位方式,高电平有效,复位值为5,电路结构如下图所示

输入格式

时钟信号clk, 同步复位信号reset, 使能信号en

输出格式

4bit计数信号q

module top_module(

input clk,

input reset,

input en,

output reg [3:0]q);

always @(posedge clk) begin

if(reset)

q <= 5; //高电平有效,复位值为5

else if(en)

if( q <= 5) // q=5 时

q <= 15; // q重新赋值15

else

q <= q - 1; //否则,每次q减1

else

q <= q;

end

endmodule

795

795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?