入坑OpenCL一周左右,万事开头难,但是发现后面的学习也不容易。。

通过设备管理器查看到自己的电脑配置的是Intel核显HD530,以下是自己搭建OpenCL运行环境的流程。

1)下载并安装Intel的SDK for OpenCL

打开网址https://software.intel.com/en-us/opencl-sdk/choose-download,选择SDK for OpenCL进行下载,下载之前需要使用邮箱注册。

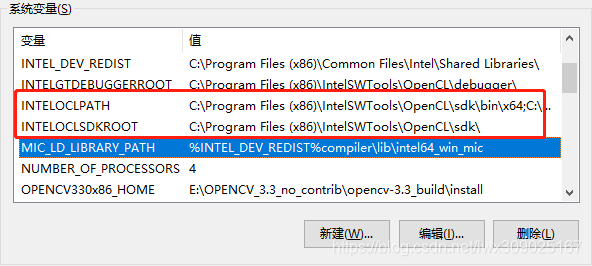

下载完毕后使用管理员权限正常安装,安装包会把开发用到的.h文件和库文件放入安装目录(我的是在C:\Program Files (x86)\IntelSWTools\OpenCL),并将头文件/库文件路径加入系统路径中。

2)环境测试

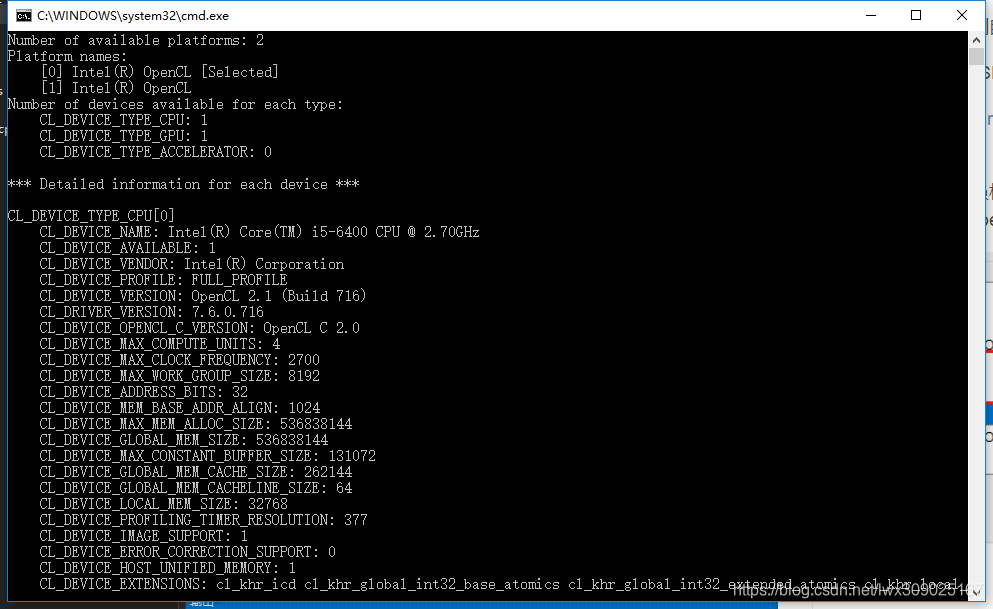

现在需要测试开发环境是否搭建成功,下载Intel提供的一个测试代码,解压后用VS打开。我安装的是VS2015,打开后会将项目工程(VS2010版)进行升级,之后编译成功,运行后命令行窗口打印出获取到的有关OpenCL设备的信息,如下图所示,表明OpenCL运行环境已经成功配置。

3)自己搭建OpenCL工程

第二步下载到的示例代码文件夹解压后,有一个templates文件夹,其中放置了x86/x64下debug/release模式的项目属性表。我们可以在自己新建的工程项目中按需添加这些属性表,即可完成对OpenCL的头文件、库文件的引用,十分方便。

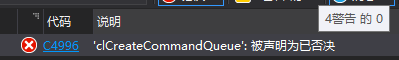

这里以《OpenCLInAction》中示例代码为例说明搭建OpenCL工程的流程。新建一个控制台工程,将示例代码的源文件加入该工程中,之后将上述的属性表按需加入项目的属性管理器中,完成对OpenCL的头文件、库文件的引用;之后进行编译,咦,出错了,告诉我调用的OpenCL函数被声明为已否决

查看头文件中的定义发现,之前安装的OpenCL版本已经是2.1了,头文件中默认抛弃了之前版本中的旧接口函数,而加入的《OpenCLInAction》中示例代码调用的就是1.2版本接口函数。解决方法就是在包含cl.h之前加入CL_USE_DEPRECATED_OPENCL_X_X_APIS的宏定义,我需要调用1.2版本的接口,按照如下设置

#define CL_USE_DEPRECATED_OPENCL_1_2_APIS

#ifdef MAC

#include <OpenCL/cl.h>

#else

#include <CL/cl.h>

#endif

再次编译没有产生错误,大功告成,可以开始愉快地撸代码了~

4)参考

https://www.cnblogs.com/Reyzal/p/7389993.html

本文详细记录了在Intel核显HD530上搭建OpenCL运行环境的步骤,包括下载安装Intel SDK,环境测试,以及解决版本不兼容问题的方法。作者分享了从新手入门到成功运行示例代码的全过程。

本文详细记录了在Intel核显HD530上搭建OpenCL运行环境的步骤,包括下载安装Intel SDK,环境测试,以及解决版本不兼容问题的方法。作者分享了从新手入门到成功运行示例代码的全过程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?