目录

一、 内容介绍

- 理解HLS

- HLS在Quartus上的实现

二、 理解HLS

2.1 HLS是什么?与VHDL/Verilog编程技术有什么关系?

HLS是一种高级综合技术,它允许开发人员使用高级语言(如C、C++和SystemC)来描述数字电路的行为和功能,然后将其转换为硬件电路实现。这种转换过程是自动完成的,因此开发人员无需手动编写硬件描述语言(HDL)。

HLS的主要目的是简化FPGA设计流程,提高设计效率和设计质量。通过使用高级语言来描述电路,开发人员可以更快速地进行设计和调试,同时也可以更容易地对电路进行修改和优化。此外,HLS还可以自动生成优化后的硬件电路,从而提高性能和资源利用率。

与传统的VHDL/Verilog编程技术相比,HLS提供了更高的抽象级别。VHDL和Verilog是硬件描述语言,通常用于详细描述硬件的逻辑和行为,包括门级和寄存器传输级的设计。这些语言需要设计者具备硬件设计和时序分析的专业知识,并且开发周期可能较长。

HLS与VHDL/Verilog的关系可以概括为:

HLS可以作为从高级语言到VHDL/Verilog的桥梁,将高级语言描述的算法自动转换成VHDL/Verilog代码。

HLS允许设计者在更高的抽象级别上工作,而不必深入到硬件细节,这有助于加速设计过程并提高生产力。

HLS有助于软件工程师参与硬件设计,因为它减少了对硬件专业知识的需求。

HLS工具的结果质量(Quality of Results, QoR)可能不如手动RTL设计,但在开发时间和生产率方面具有优势,特别是在快速原型设计和产品上市时间紧迫的情况下。

总的来说,HLS是一种补充和加速传统VHDL/Verilog设计流程的技术,它使设计者能够更快地实现从概念到硬件的转变。

2.2 HLS有哪些关键技术问题?目前存在什么技术局限性?

HLS(High-Level Synthesis,高层综合)的关键技术问题和局限性主要包括以下几个方面:

优化限制:与硬件描述语言(HDL)如Verilog相比,HLS在优化方面存在一定限制。例如,HDL可以更精细地控制硬件资源的使用,而HLS可能无法实现同样的优化效果。

动态参数处理:HLS通常禁止动态分配指针,因为这要求工具知道函数访问的存储空间,以便正确放置连接。

并行执行限制:HLS对于并行执行有限制,它不允许访问同一数组的函数并行运行,这可能限制了设计的并行性和性能。

内存过度分配:在某些情况下,HLS倾向于宽度扩展而不是深度扩展,这可能导致BRAM的过度分配和内存使用效率降低。

资源重用:HLS在资源重用方面可能不如手写HDL高效,需要通过内联子功能或复制函数等手段来实现资源的重用。

浮点运算支持:HLS可能不支持浮点累加器,需要使用部分和和树加法器等方法来实现浮点运算。

设计空间探索:HLS工具可能没有提供足够的设计空间探索支持,导致用户需要手动进行繁琐的尝试和错误过程。

性能估计和设计限制:HLS工具可能没有提供早期的性能估计,无法预先检测违反设计和平台限制的行为。

数据通信方式:HLS工具可能没有充分利用所有可能的数据通信方式,影响设计的性能和资源利用。

代码优化:HLS工具可能缺乏对用户代码进行优化转换的功能概述,导致生成的设计不是最优的。

报告和反馈:HLS工具可能在支持代码报告方面存在延迟,不利于快速迭代和设计改进。

特定情况下的效率:在某些特定情况下,如需要将大量加速器映射到硬件时,HLS工具可能无法高效实施,影响设计周期。

这些关键技术问题和局限性表明,尽管HLS提供了从高级语言到硬件设计的快速路径,但在自动化设计流程、优化和资源管理方面仍有改进空间。随着技术的发展,这些局限性有望得到解决,HLS的实用性和效率将进一步提高。

三、 HLS在Quartus上的实现

3.1 配置环境

Quartus prime 18.1

作为HLS实验环境搭建的必要软件之一,经验证Quartus Prime 17.1以及18.1版本可支持HLS开发。该软件可在Intel官网上注册后直接下载并按默认选项安装即可。

Modelsim Starter Edition 10.5b

ModelSim是Quartus Prime的附加软件之一。安装Quartus Prime的同时也会安装相应版本的ModelSim,所以无需专门安装该软件。

在此次HLS实验中,使用的版本是ModelSim Starter Edition 10.5b,此为HLS的默认调用版本并且不需要License。

Microsoft Visual Studio 2010 (Visual C++, 未使用license)

在整个HLS实验环境搭建中,建议安装使用Microsoft Visual Studio 2010因为经验证更新后的版本将不支持HLS开发。其中Profession、Ultimate、Standard三个版本均可从网上下载安装并未使用License,但是需要注意的是Standard版本仅支持HLS 18.1以及HLS 19.1,所以到时候需要手动匹配HLS版本方可运行。此外,在安装过程中需确保Visual C++被成功勾选。

在此次HLS实验中,使用的版本是Microsoft Visual Studio 2010 Ultimate。

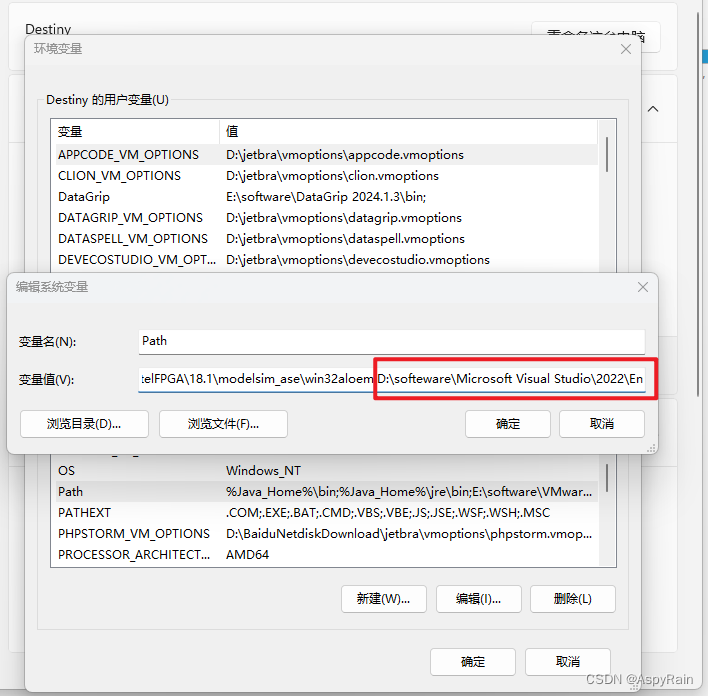

(需要注意的是在全部软件安装完成后,环境变量都已自动被设置,故而无需再手动设置,出现问题再配置)

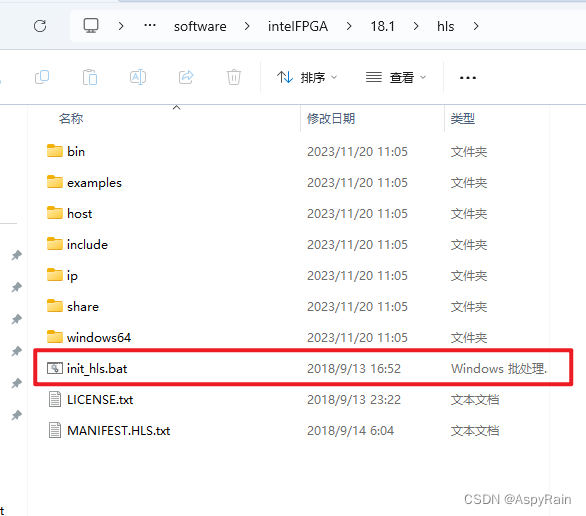

- 找到Quartus目录下的

init_hls.bat

一般在’intelFPGA/18.x/hls’

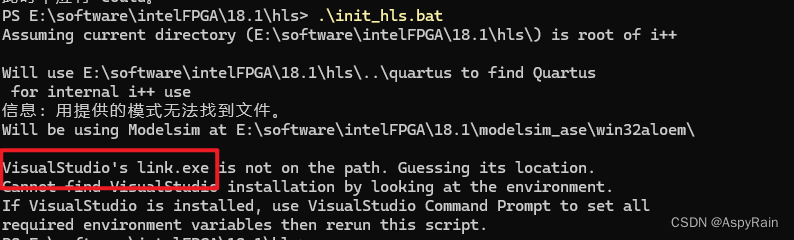

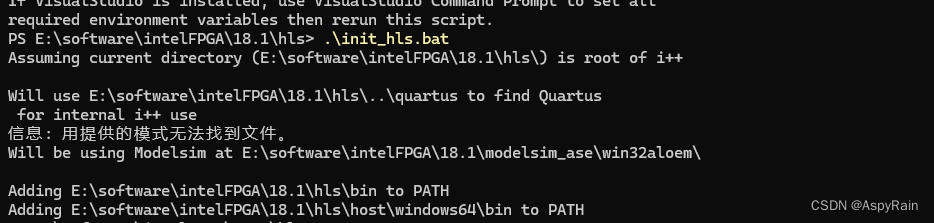

在命令提示符窗口(CMD)运行此程序

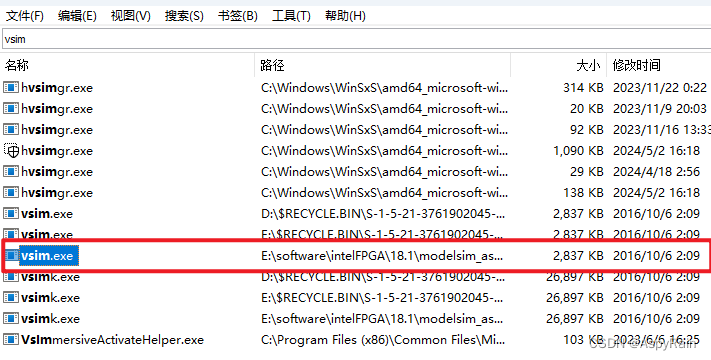

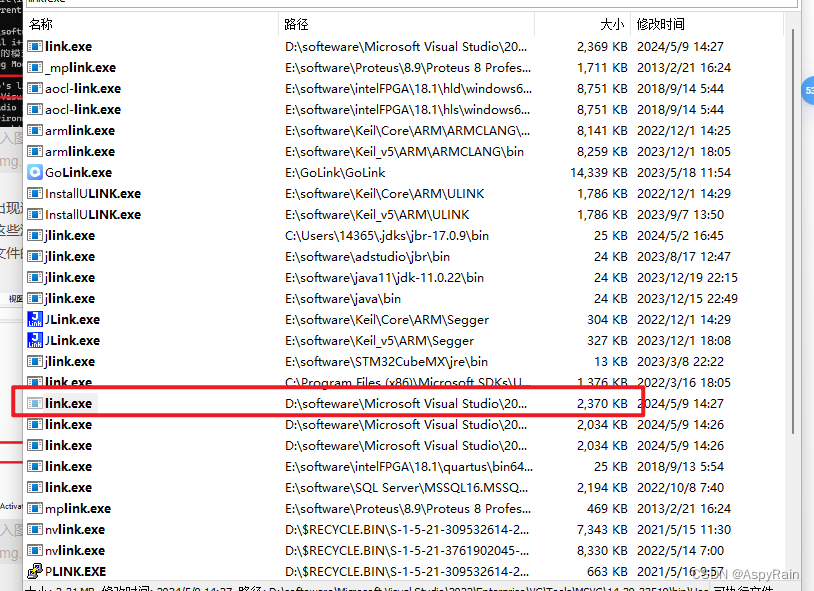

有可能会出现这样的错误,同样也有可能找不到modelsim的vsim.exe,如果你确定这些没找到的都安装了的话,就是环境变量没配置好,你需要找到这两个文件的位置,可以用Everything搜索

ok了,然后把路径添加到环境变量中

然后确认返回

如果还报错就把link.exe直接复制到modelsim的环境win32alem文件夹下

重新运行

运行成功后重启cmd

3.2 测试

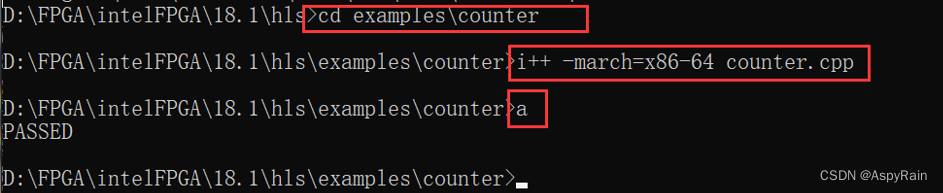

编译为FPGA程序

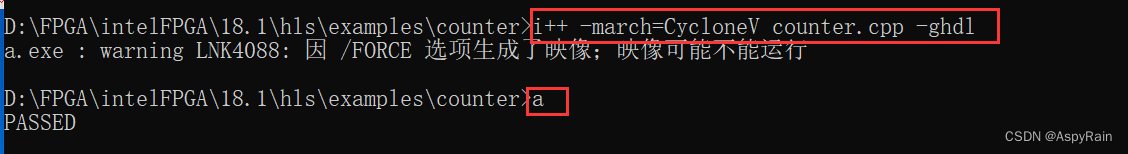

(1)输入指令“i++ -march=CycloneV counter.cpp”使用FPGA(CycloneV)进行编译并生成名为“a”的可执行文件。注意:此处若提示Warning,无需理会。

(2)输入指令“a”进行测试,若结果显示“PASSED”,则编译与测试成功。

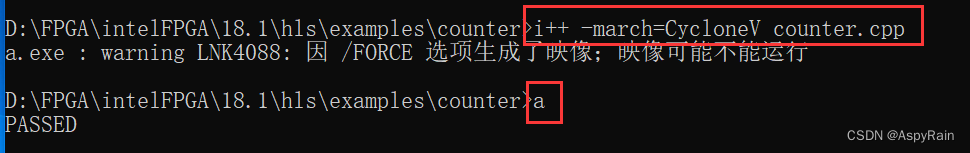

编译为FPGA程序

(1)输入指令“i++ -march=CycloneV counter.cpp”使用FPGA(CycloneV)进行编译并生成名为“a”的可执行文件。注意:此处若提示Warning,无需理会。

(2)输入指令“a”进行测试,若结果显示“PASSED”,则编译与测试成功。

(3)输入指令“i++ -march=CycloneV counter.cpp -ghdl” 使用FPGA(CycloneV)进行编译生成名为“a”的可执行文件并记录信号以帮助调试。注意:此处若提示Warning,无需理会。

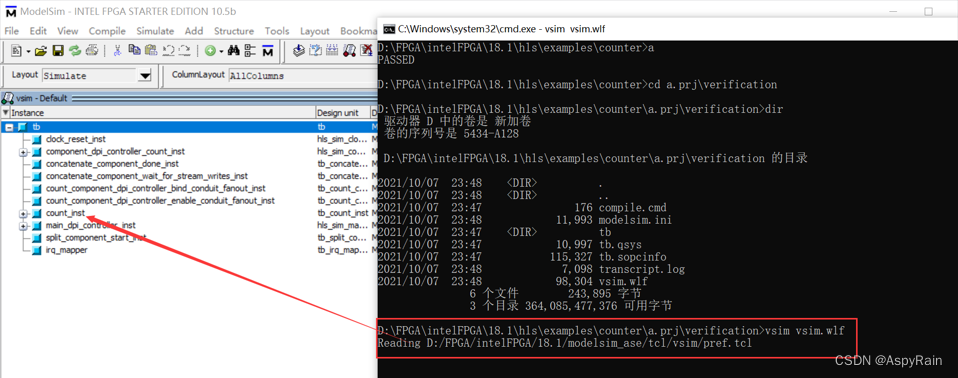

(4)输入指令“a” 执行可执行文件,若结果显示“PASSED”,则编译与测试成功。同时,在上一步中记录的信号的波形记录会自动生成名为“vsim.wlf”的文件并记录在路径“a.prj/verification”中,以便于使用ModelSim对该信号进行仿真。

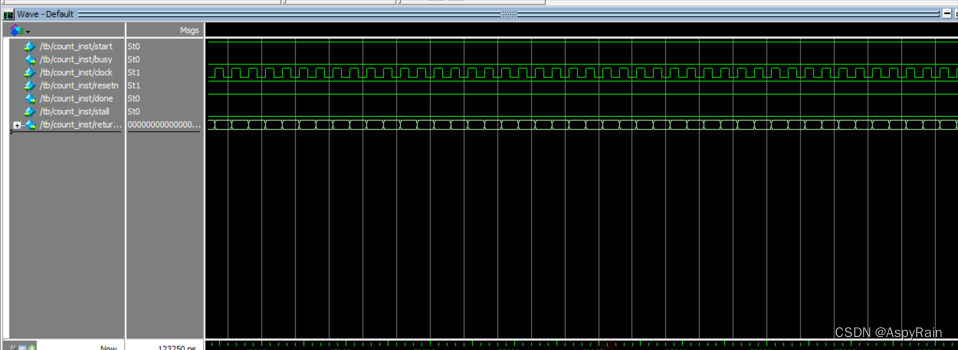

ModelSim仿真

(1)输入指令“cd a.prj”和“cd verification”或者“cd a.prj\verification”进入“vsim.wlf”所在的文件夹中,并输入指令“dir”查看该文件是否存在。

(2)输入指令“vsim vsim.wlf”使用ModelSim打开该文件并对记录的信号进行仿真。

683

683

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?