HLS入门——点亮LED仿真

一、HLS简介

(一)什么是HLS?

HLS是一种设计方法,使用HSL可以更快地开发电子系统,特别是那些需要特定硬件加速的复杂系统。通过使用HLS,你可以用高级语言(如C或C++)编写代码,然后自动转换成硬件描述语言(HDL),从而加速开发过程。

(二)HLS能做什么?

HLS允许开发者在更高的抽象层次上工作,这意味着你可以专注于算法和功能,而不是硬件的具体细节。当你需要优化性能或功耗时,HLS工具可以自动为你找到最佳的硬件实现方案。

(三)HLS的使用

- 编写代码:使用C或C++等高级语言编写你的算法或系统。

- 配置HLS工具:设置性能目标(如速度、面积或功耗)和约束条件。

- 综合:HLS工具将高级代码转换成硬件描述语言(HDL),如Verilog或VHDL。

- 验证:检查生成的HDL代码是否符合预期的功能和性能。

- 实现:将HDL代码用于FPGA或ASIC的生产。

(四)HLS的优势

- 加速开发:减少从概念到实现的时间。

- 提高效率:自动优化可以提高系统的性能和功耗。

- 灵活性:可以在不同的硬件平台上实现相同的高级代码。

- 可扩展性:随着技术的发展,HLS工具可以适应新的硬件和需求。

(五)HLS与VHDL/Verilog编程技术的关系

HLS与传统的VHDL/Verilog编程技术之间存在紧密的联系,但它们在设计流程和抽象层次上有所不同:

-

抽象层次:HLS提供了比VHDL/Verilog更高的抽象层次。开发者可以使用C/C++等高级语言来描述算法和逻辑,而不是直接使用VHDL/Verilog来设计硬件的门级或寄存器传输级(RTL)实现。

-

设计流程:在HLS中,开发者首先用高级语言编写代码,然后通过HLS工具自动转换成VHDL或Verilog代码。相比之下,VHDL/Verilog编程需要开发者直接用这些硬件描述语言来编写代码。

-

自动化:HLS的一个主要优势是自动化。它自动化了许多硬件设计任务,如资源分配、时序分析和优化,这在VHDL/Verilog编程中通常需要手动完成。

-

目标一致性:尽管方法不同,但HLS和VHDL/Verilog编程的最终目标是相同的,即生成可以部署在FPGA或ASIC上的硬件设计。

-

协同工作:HLS生成的HDL代码可以与手写的VHDL/Verilog代码结合使用,形成混合设计。这允许开发者在某些部分利用HLS的自动化优势,而在其他部分则利用VHDL/Verilog的精确控制。

(六)HLS的关键技术问题与局限性

尽管HLS提供了许多优势,但在实际应用中也存在一些关键技术问题和局限性:

- 语言支持:并非所有高级语言的特性都能被HLS工具完美支持,某些特性可能需要特别的处理或无法综合。

- 性能预测:预测HLS工具综合后的性能可能具有挑战性,因为自动化优化过程可能引入不可预见的结果。

- 调试难度:与传统的VHDL/Verilog相比,调试HLS生成的硬件可能更加困难,因为问题可能出现在高级代码或综合过程中。

- 特定领域限制:HLS可能在某些特定类型的硬件设计中表现更好,而在其他类型(如需要极端时序控制的设计)中可能不如手写VHDL/Verilog代码。

- 学习曲线:对于习惯于VHDL/Verilog的硬件工程师来说,学习HLS和相关工具可能需要一定的时间和努力。

- 工具依赖性:HLS的结果很大程度上依赖于所使用的特定工具和版本,不同的工具可能有不同的优化策略和结果。

二、点亮LED仿真

使用的是Vivado HLS 2019.2

(一)创建项目

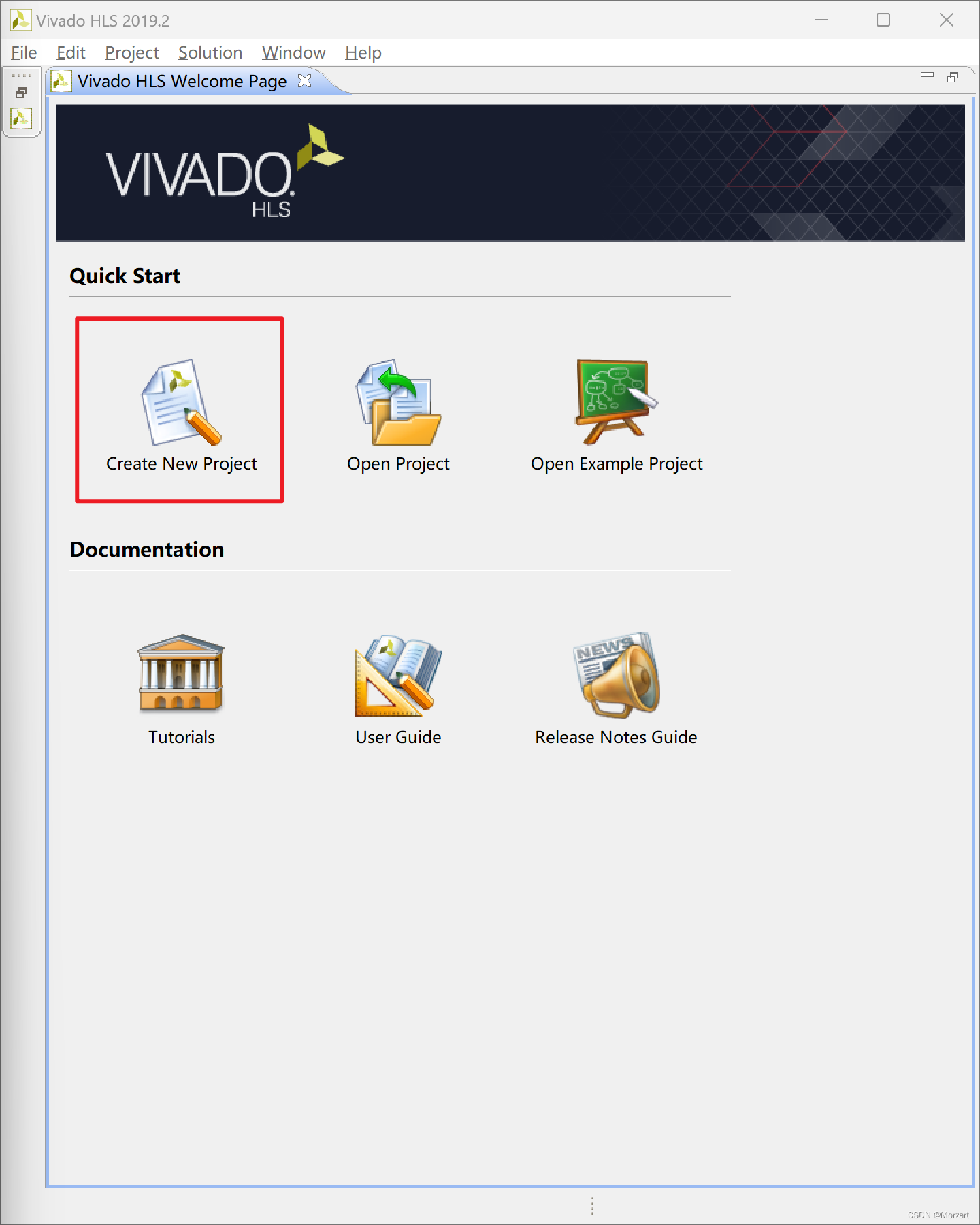

①打开Vivado HLS,点击Create New Project

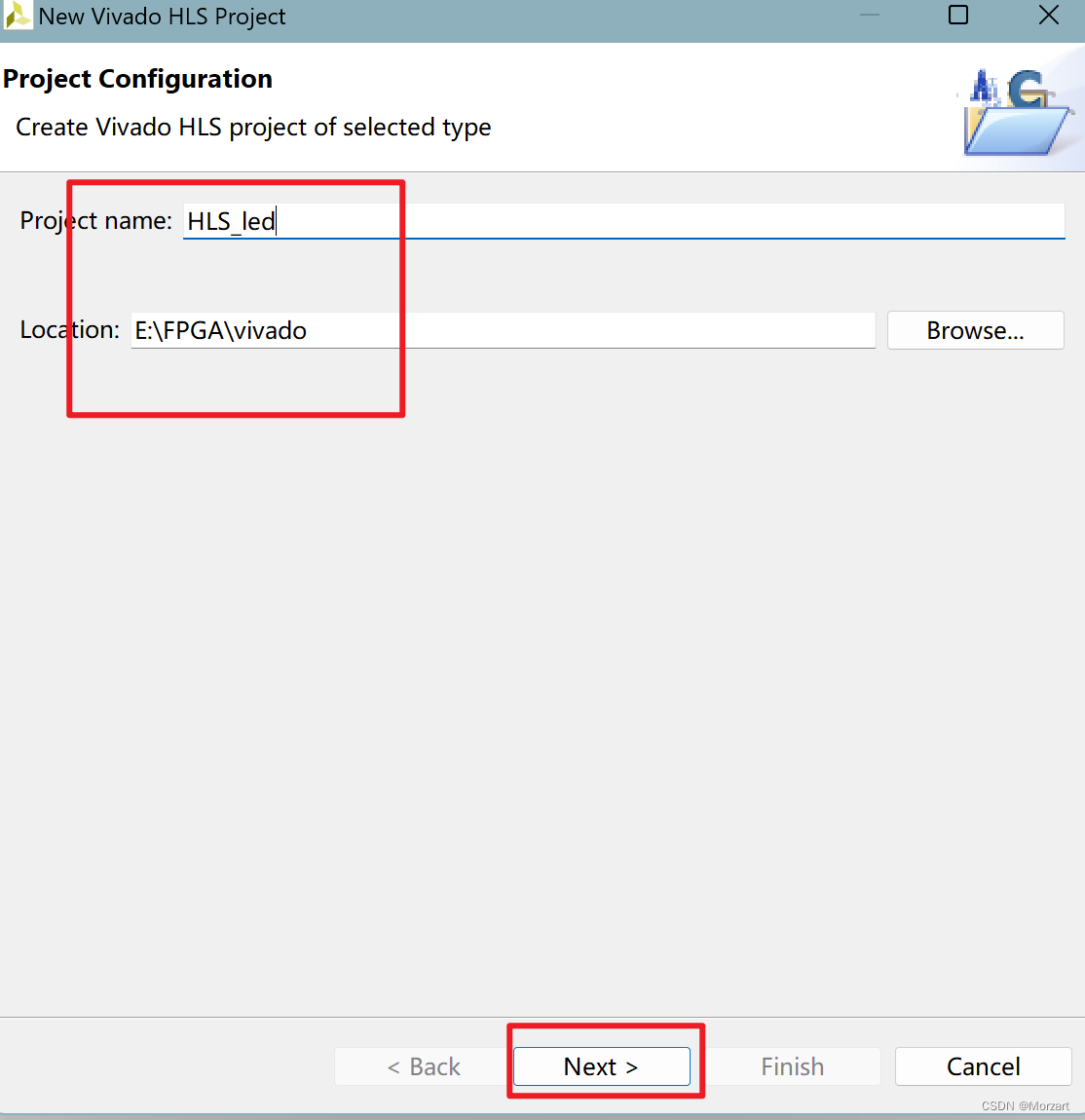

②输入相关工程信息

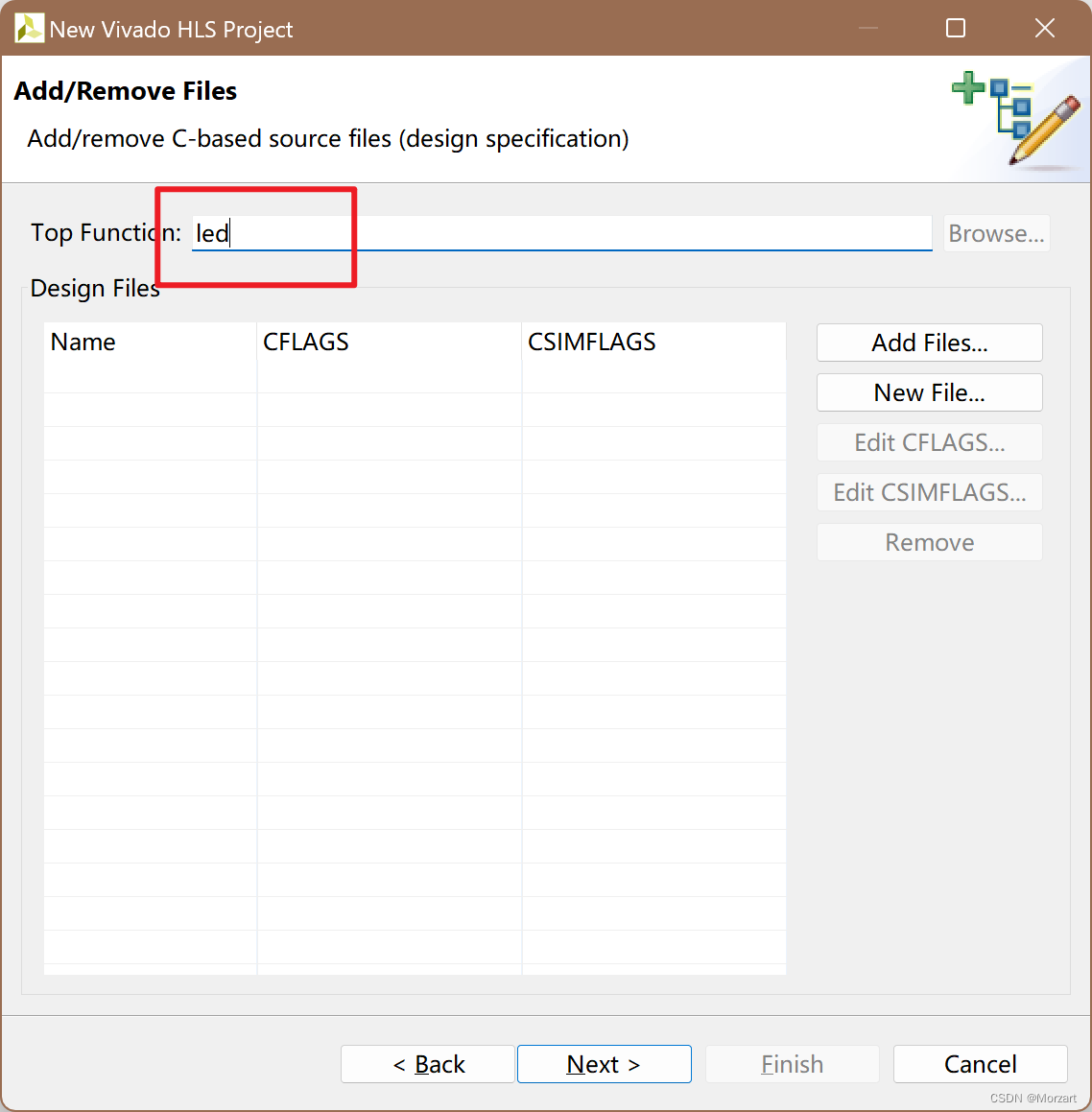

③选择顶层函数

④其他都点next,直到finish

(二)添加文件

①源文件添加

点击Source,右键后,选择New File,创建文件

led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

led.cpp

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

②仿真测试文件添加

右键Test Bench,选择New File

tb_led.cpp

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

(三)仿真与综合

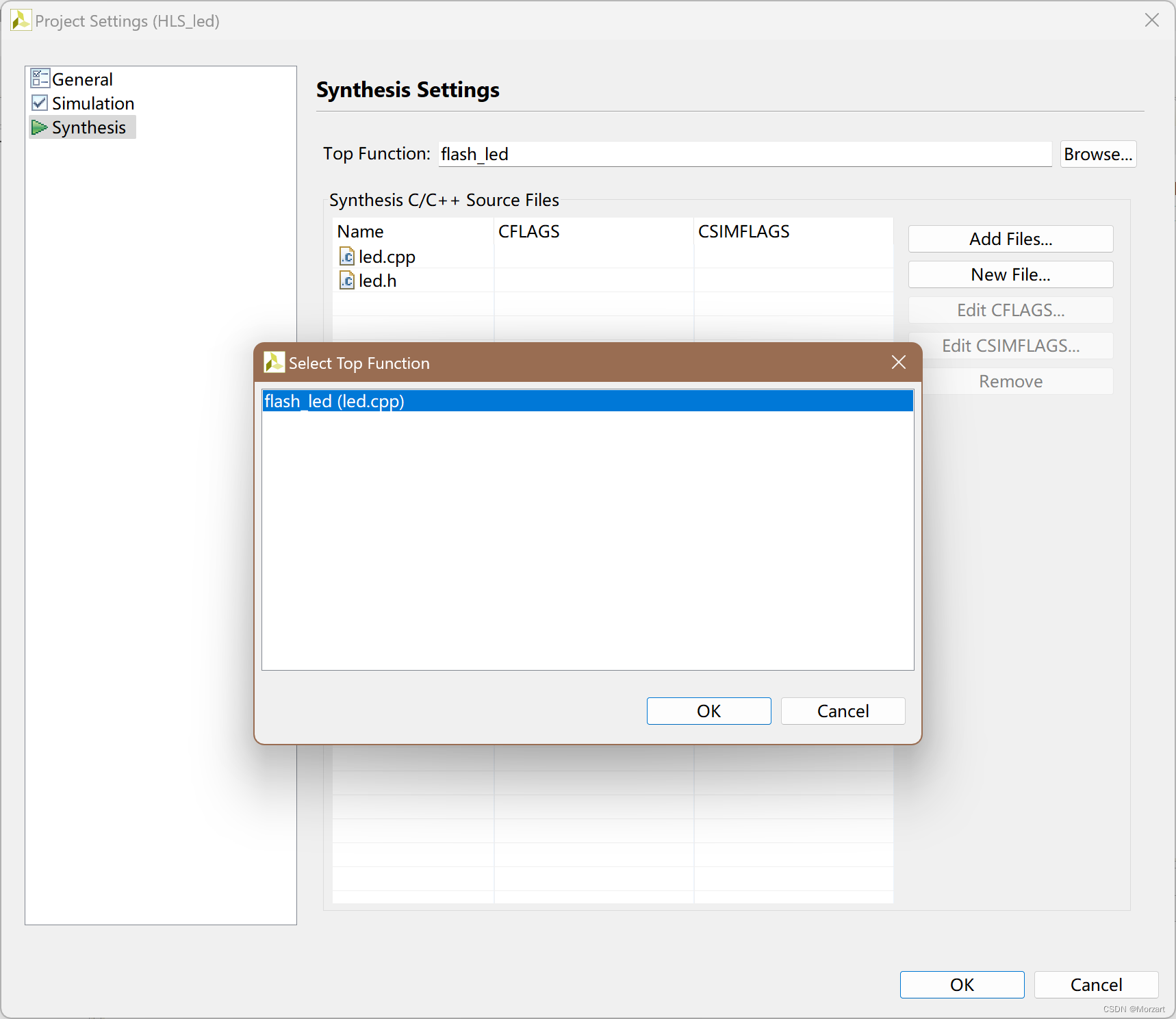

①点击project->project settings->synthesis->browser->选择顶层函数

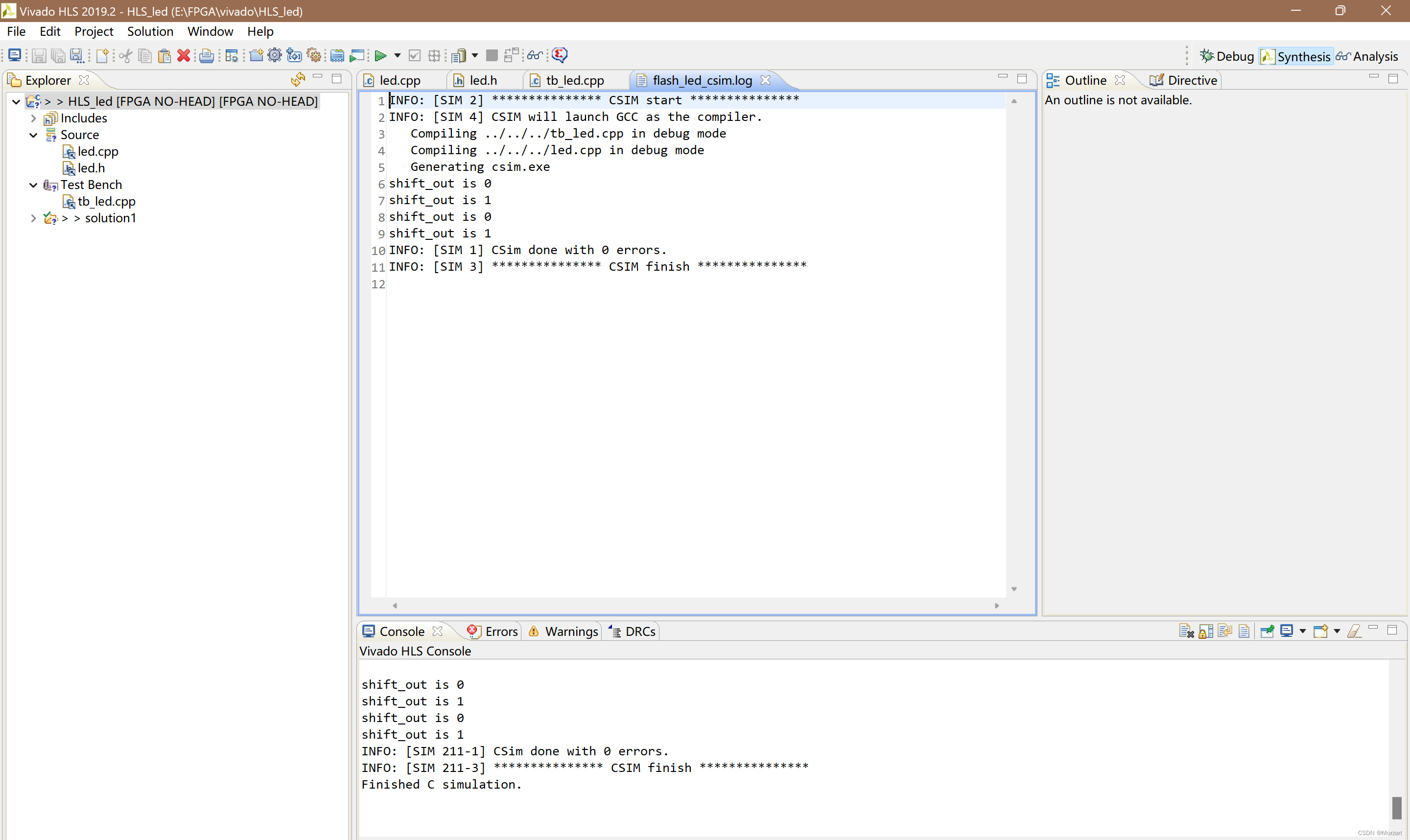

②点击project->Run C Simulation(输出01交替,表示C仿真结果正确)

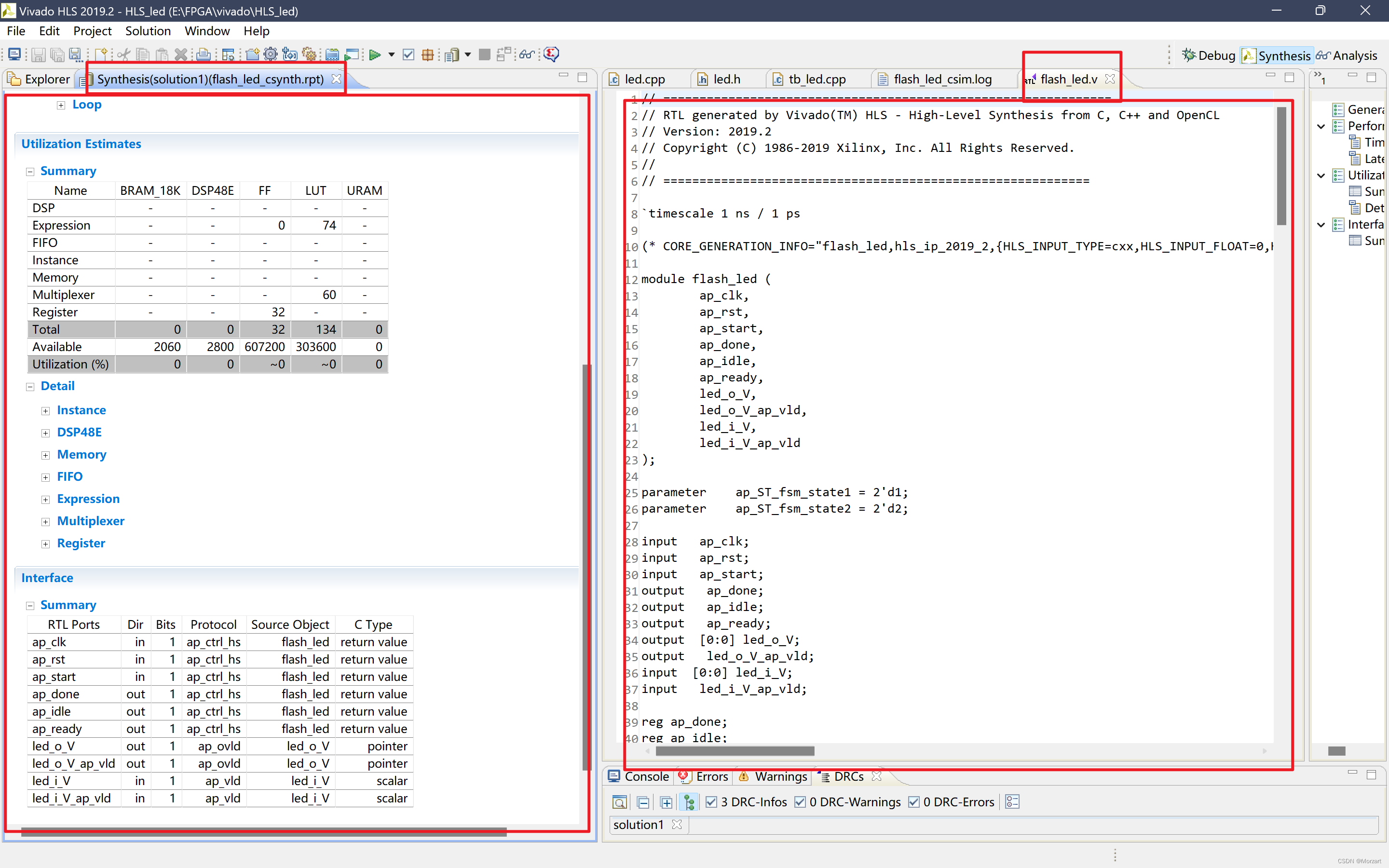

③点击Solution->Run C Synthesis->Active Solution

生成的总结文件(Synthesis(solution1)(flash_led_csynth.rpt))里有端口表格

以及solution1\impl\verilog中,有已经生成好的.v文件

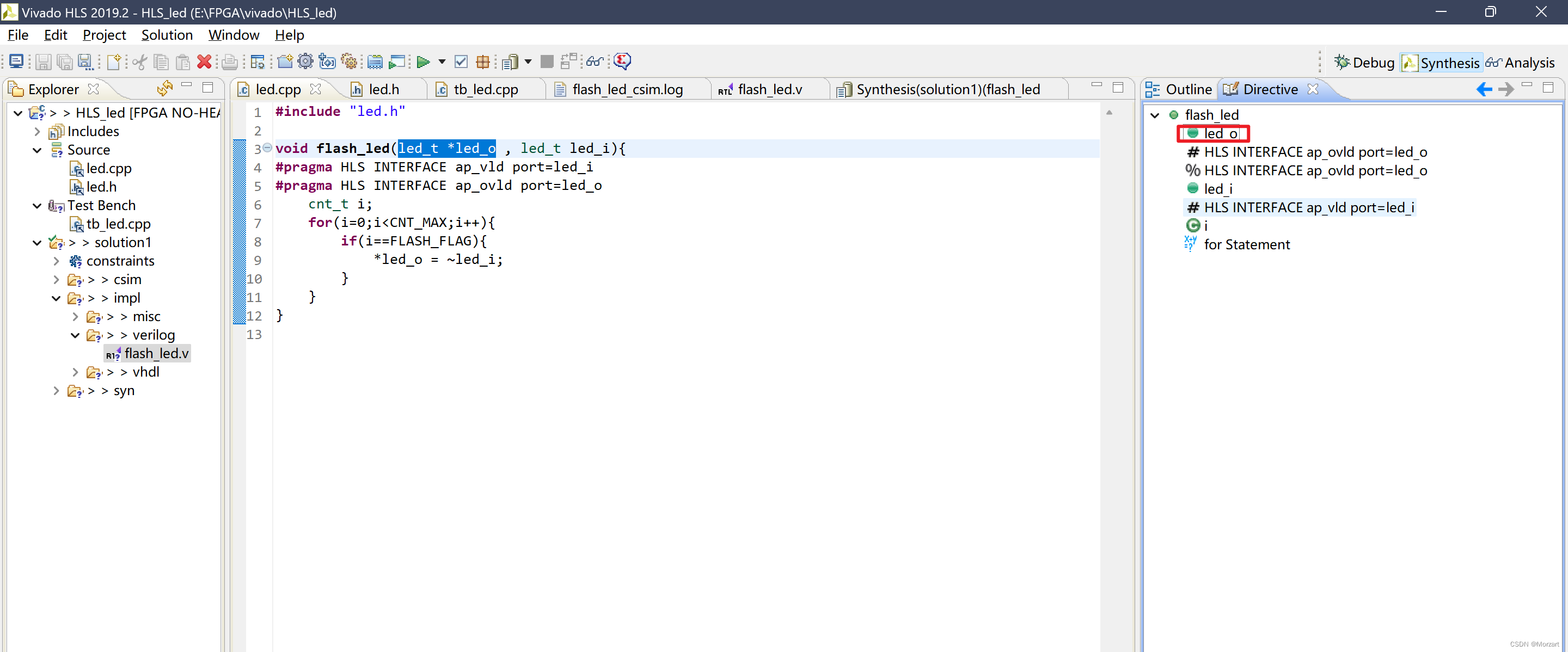

在Helloworld.cpp界面,右边的Drective界面,右键led_o,进入如下界面:

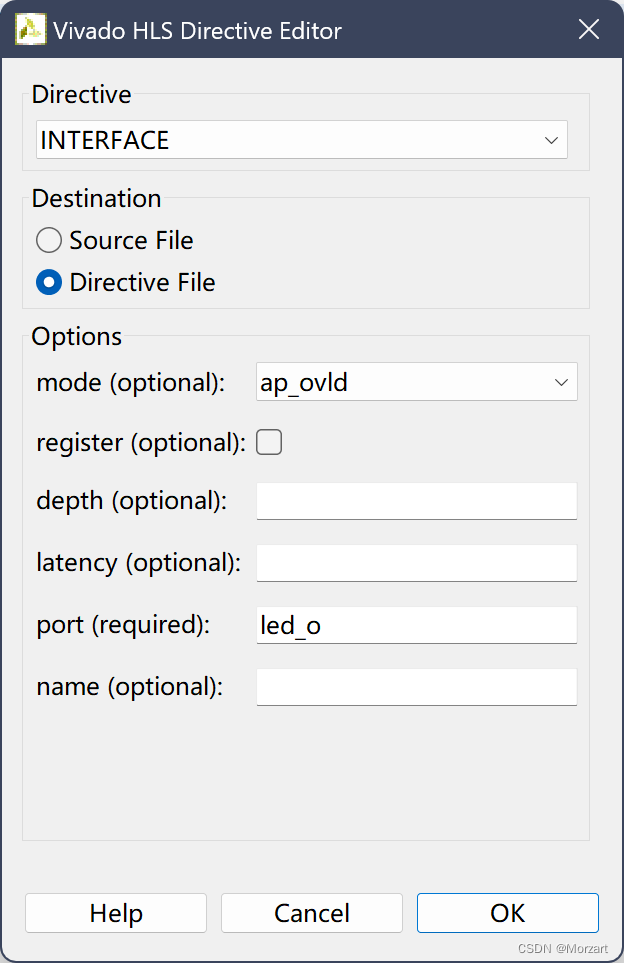

按下图来配置后点击OK

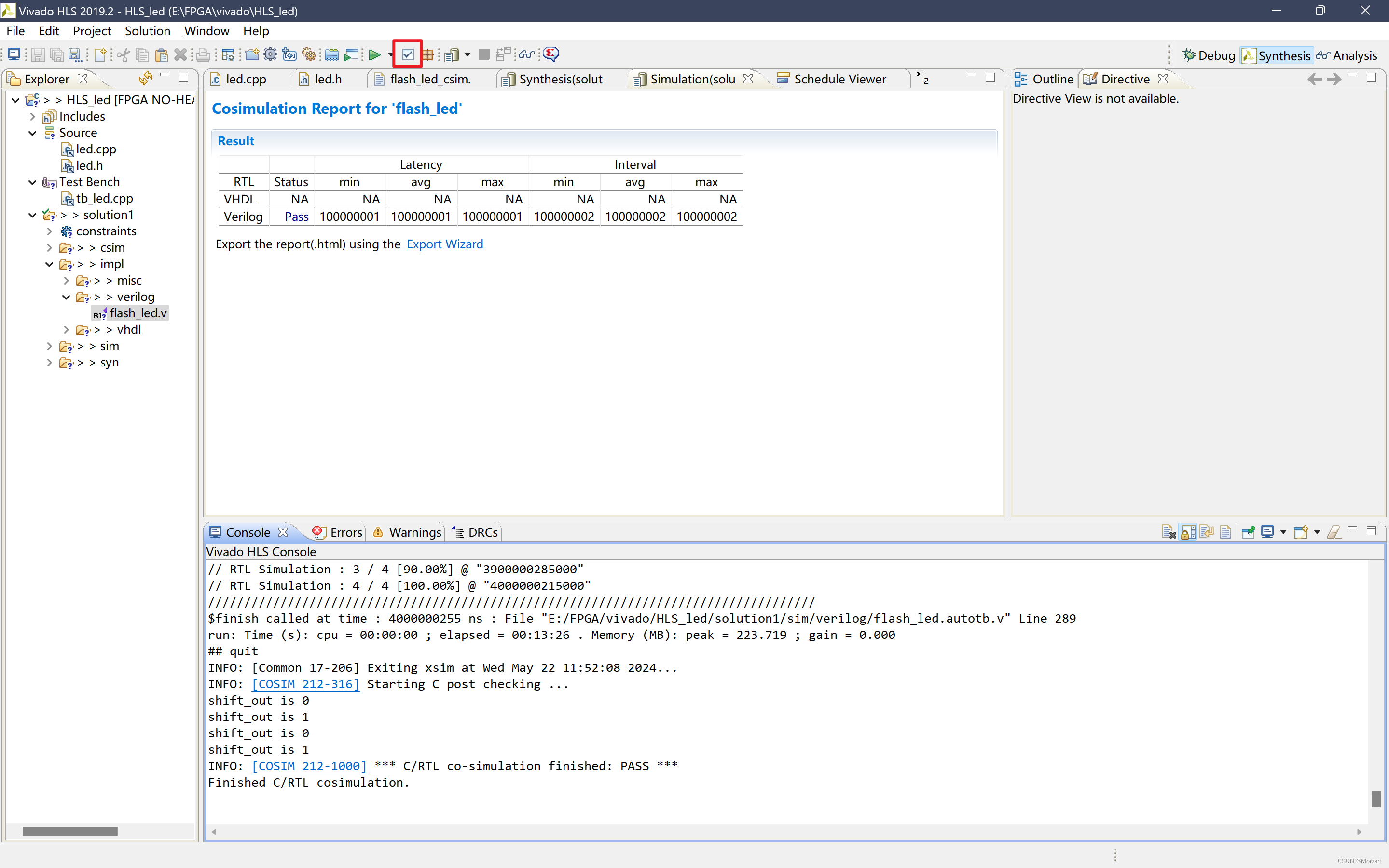

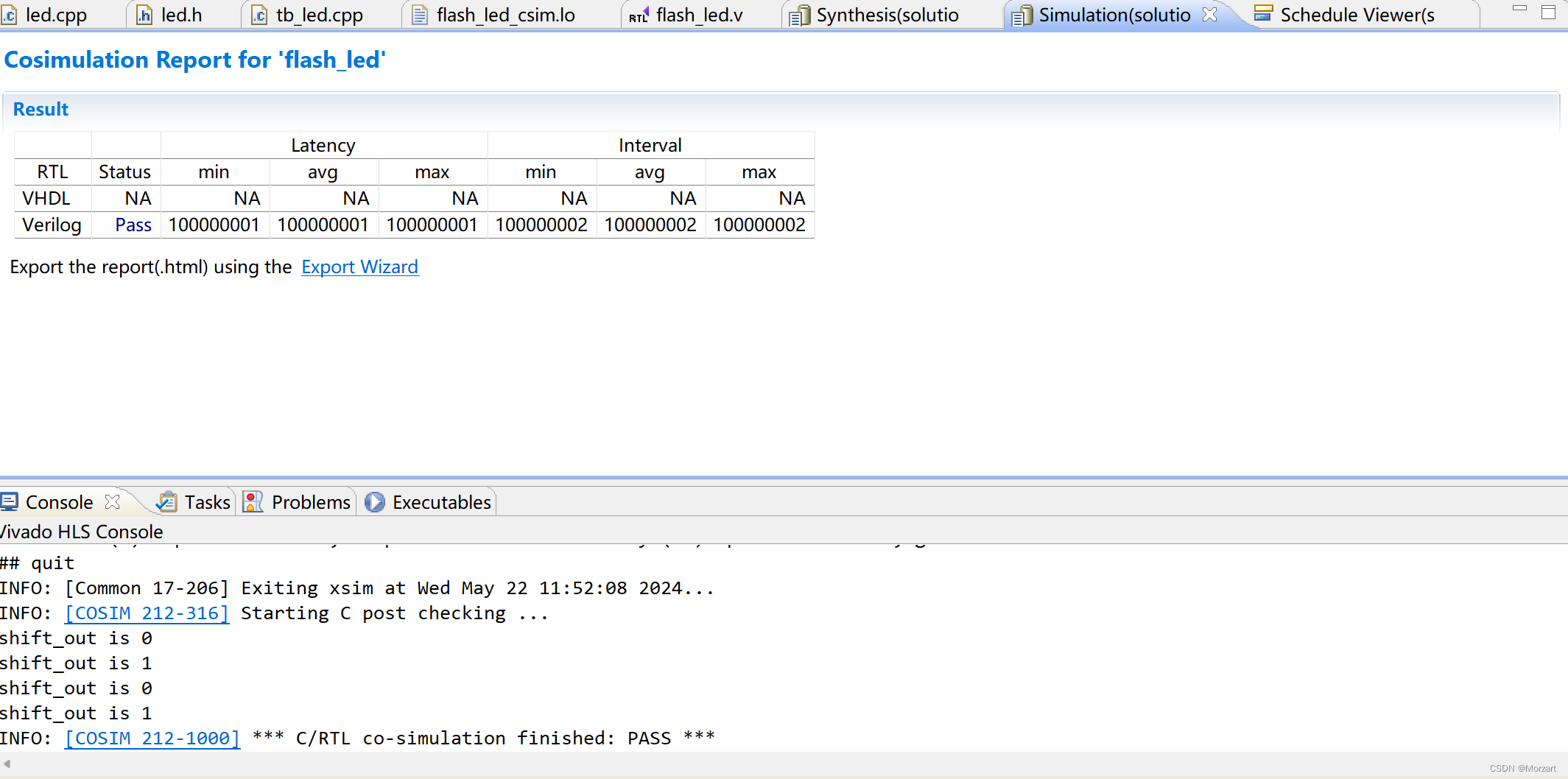

然后点击联合仿真:

结果:

三、总结

此次学习了如何使用Xilinx Vivado HLS 2019.2版本来实现一个简单的LED点亮仿真项目。这个过程包括了创建项目、添加源文件、编写C/C++代码、配置HLS工具、进行仿真与综合,以及最终的验证和实现步骤。

HLS(高级综合)作为一种设计方法,它允许开发者使用高级语言(如C或C++)来编写算法或系统,然后自动将其转换成硬件描述语言(HDL),如Verilog或VHDL。这种方法的优势在于能够加速开发过程,提高效率,增加灵活性,并具备可扩展性。

702

702

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?