题外话:本人是FPGA刚入门的新手,手头正好有块Xilinx的AC701评估板,官方例程太高端不适合入门,网上关于Artix-7的资料又太少,所以在学习的过程中把自己的心得与大家分享,希望能够一起交流。学习中借鉴了很多特权同学的教材,比如AT7套件的教程,基本上都做了移植,在这里谢谢特权同学。

---------------------------------------------------------------------------------------------------------------

本实例内容为PLL的配置和例化,通过PLL产生4个不同频率的时钟,分别驱动 4 个 LED 指示灯闪烁一样的频率。通过观察这 4 个 LED 指示灯的闪烁同步与否,可以确认 PLL 产生的这 4 个时钟的频率关系。

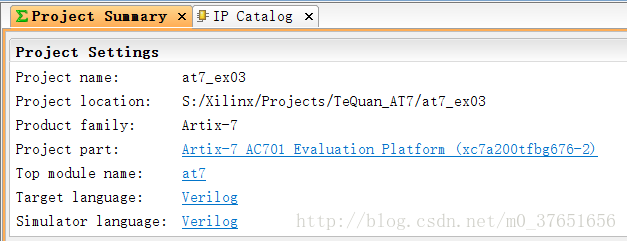

新建工程时选择AC701 Evaluation Board。

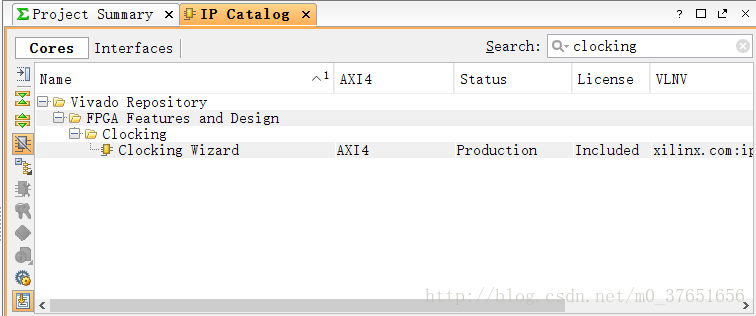

在IP Catalog中输入clocking,选择clocking wizard ip核。

首先配置Clocking Options页:

Primitive:选择为PLL

Input Clock Information:Primary Input Frequency(

MHz)设置为200(本例中选择输入时钟为SYSCLK,时钟源为SiT9102 LVDS 200MHz)。Source选择Differential clock capable pin,因为输入时钟为差分时钟,当改变输入时钟类型时一定要设置相应的时钟源!

本文档详细介绍了如何在Xilinx AC701评估板上配置PLL。从新建工程开始,逐步讲解了如何针对具体需求调整PLL设置,以实现高效、稳定的时钟生成。

本文档详细介绍了如何在Xilinx AC701评估板上配置PLL。从新建工程开始,逐步讲解了如何针对具体需求调整PLL设置,以实现高效、稳定的时钟生成。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3174

3174

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?