-

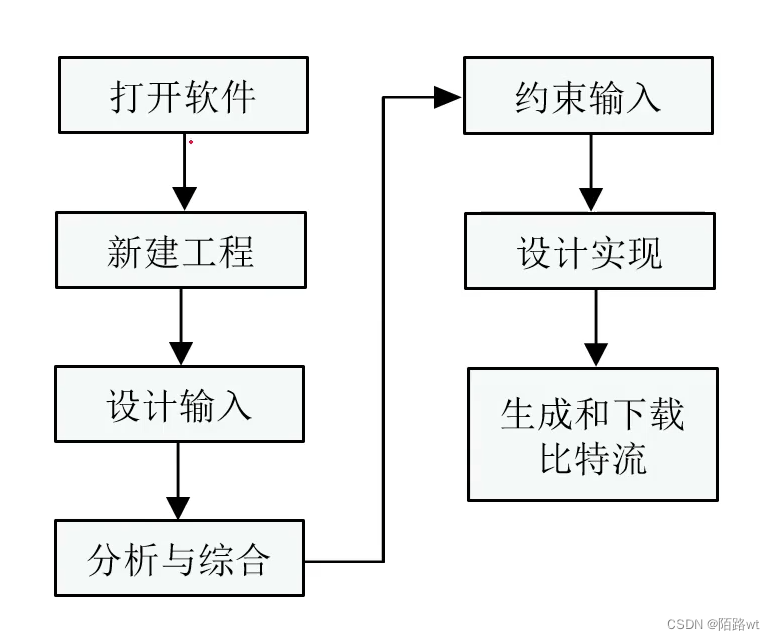

创建并完成一个简单的工程的流程

-

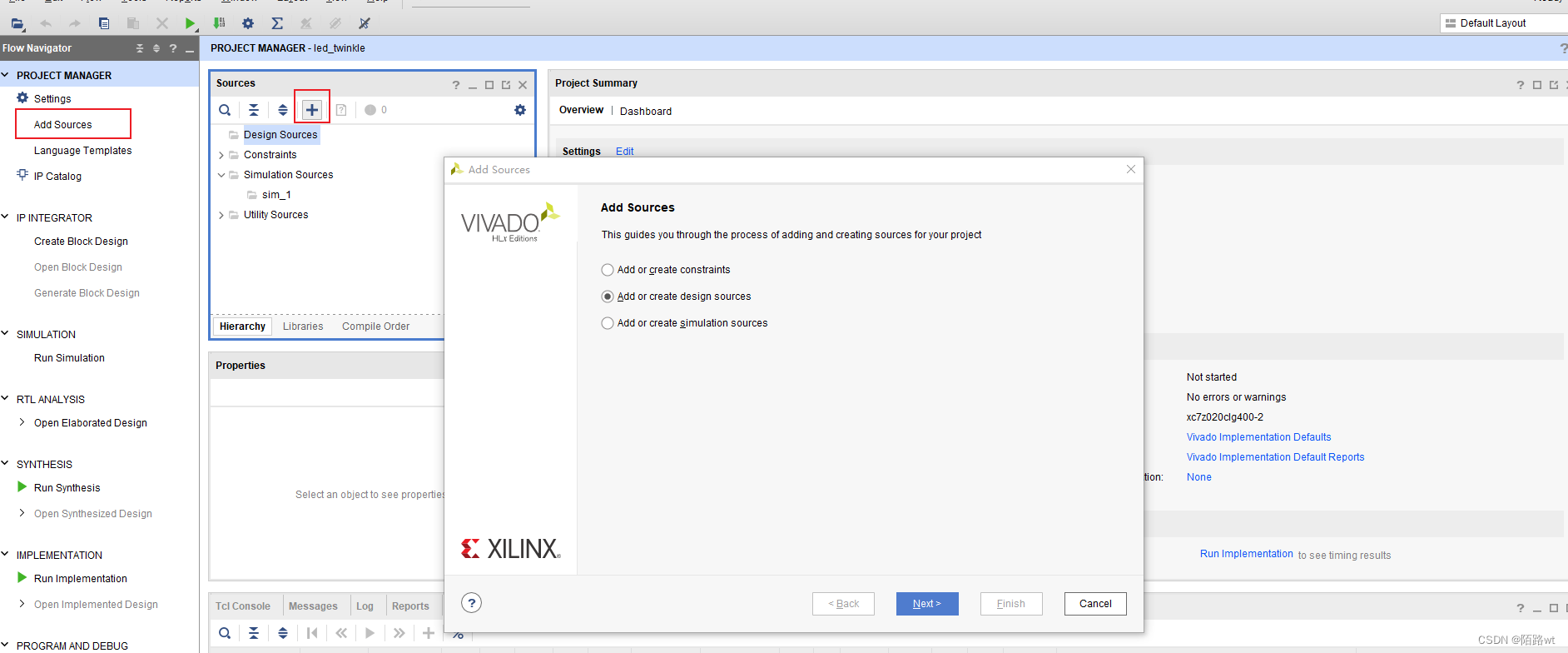

添加文件

-

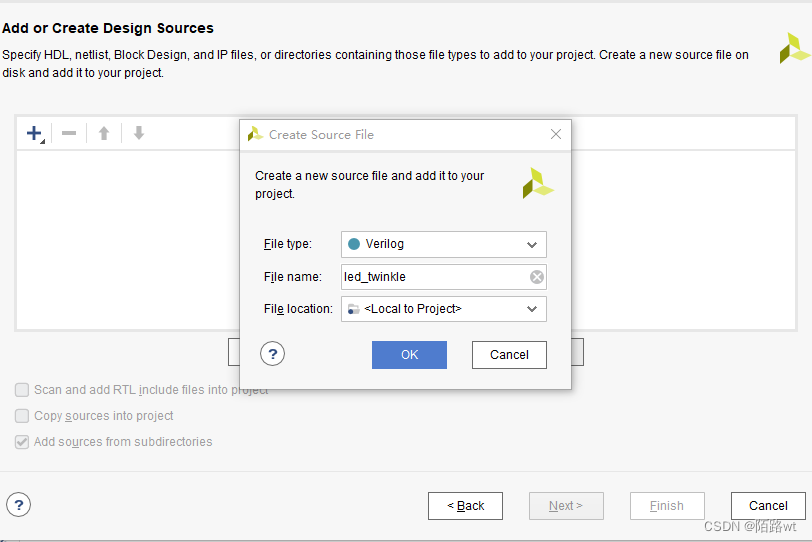

创建文件

-

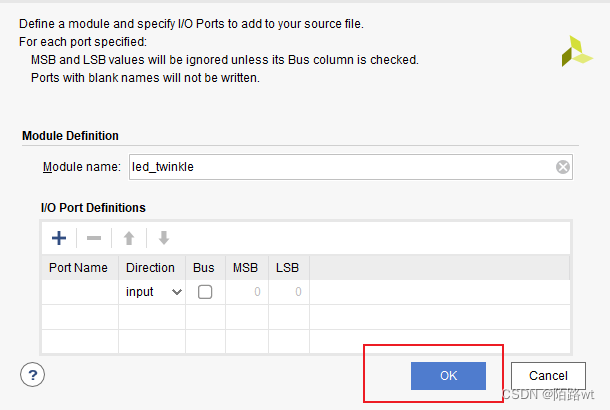

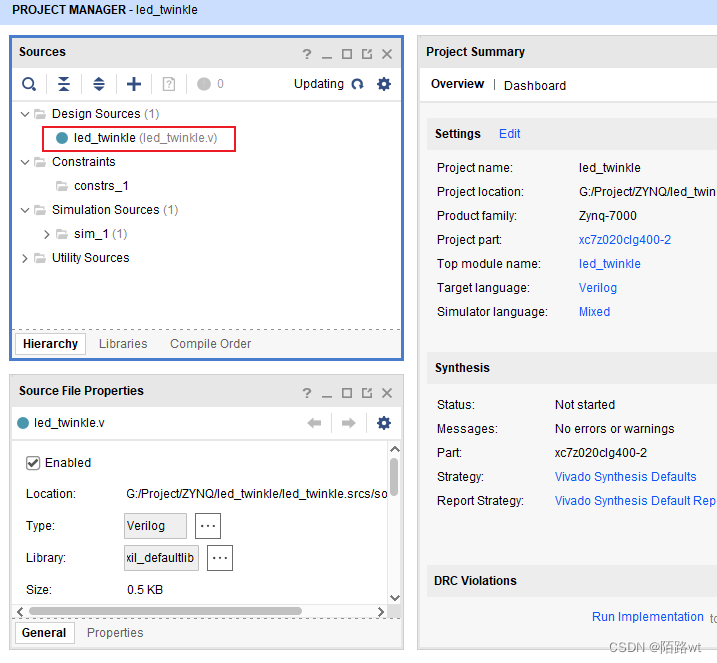

此时,文件就添加完毕了

-

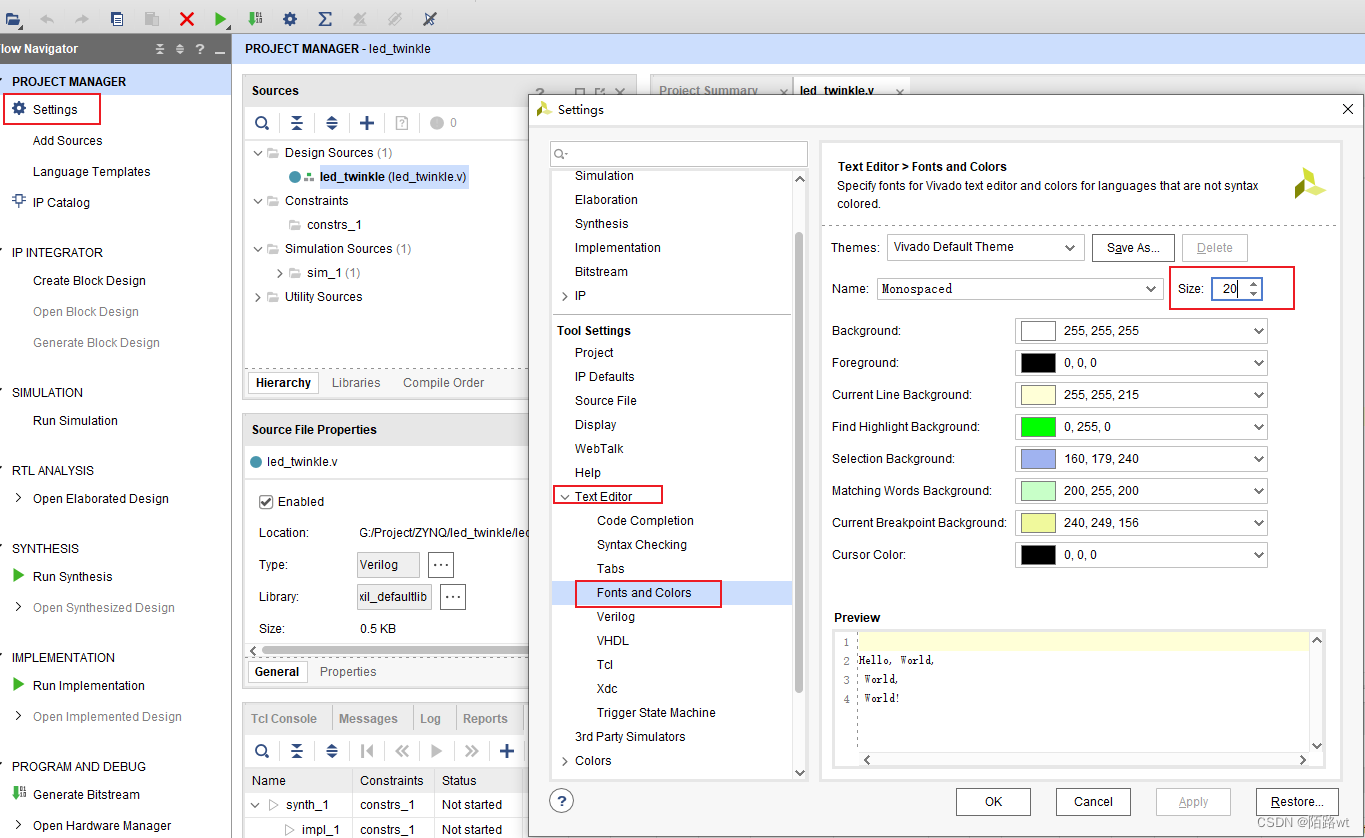

设置字体

-

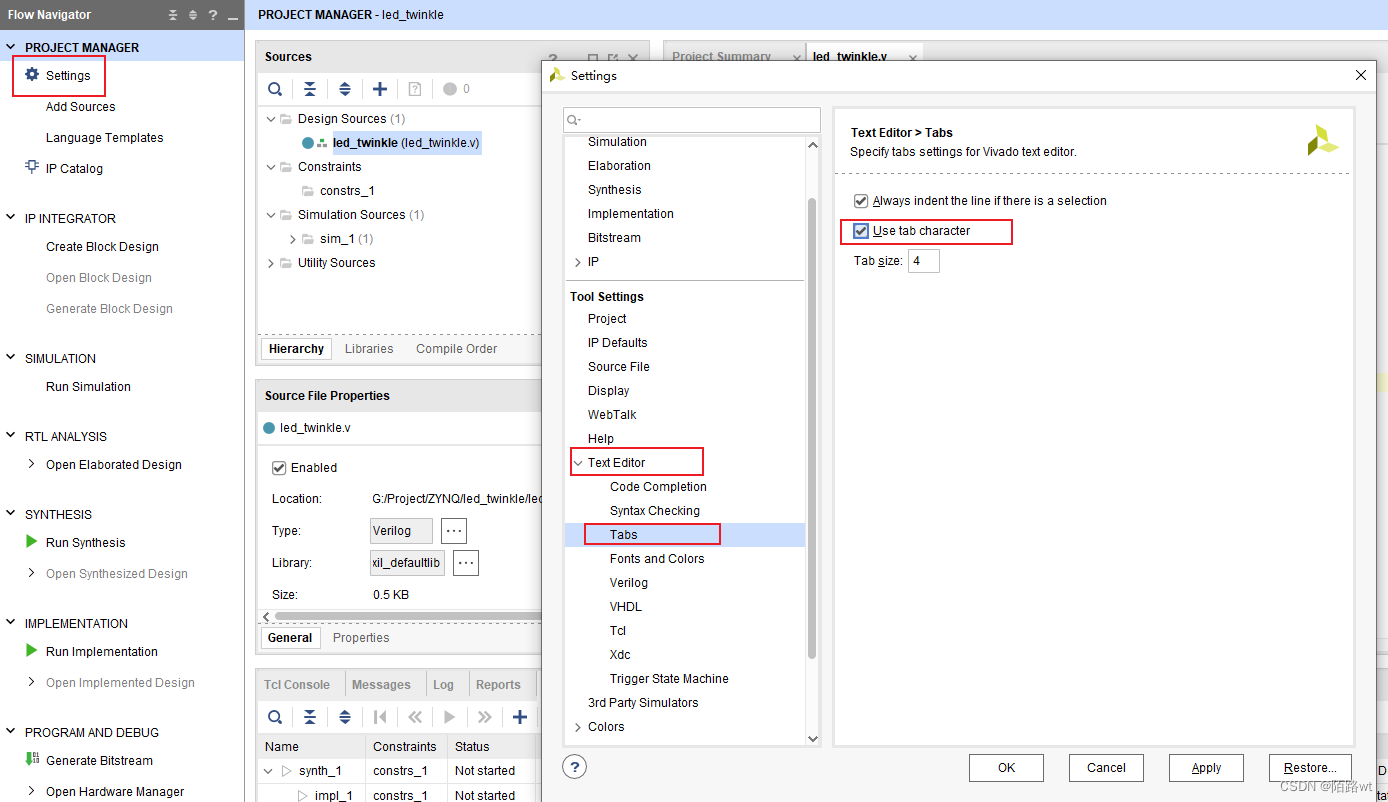

设置Table的空格字数为4个

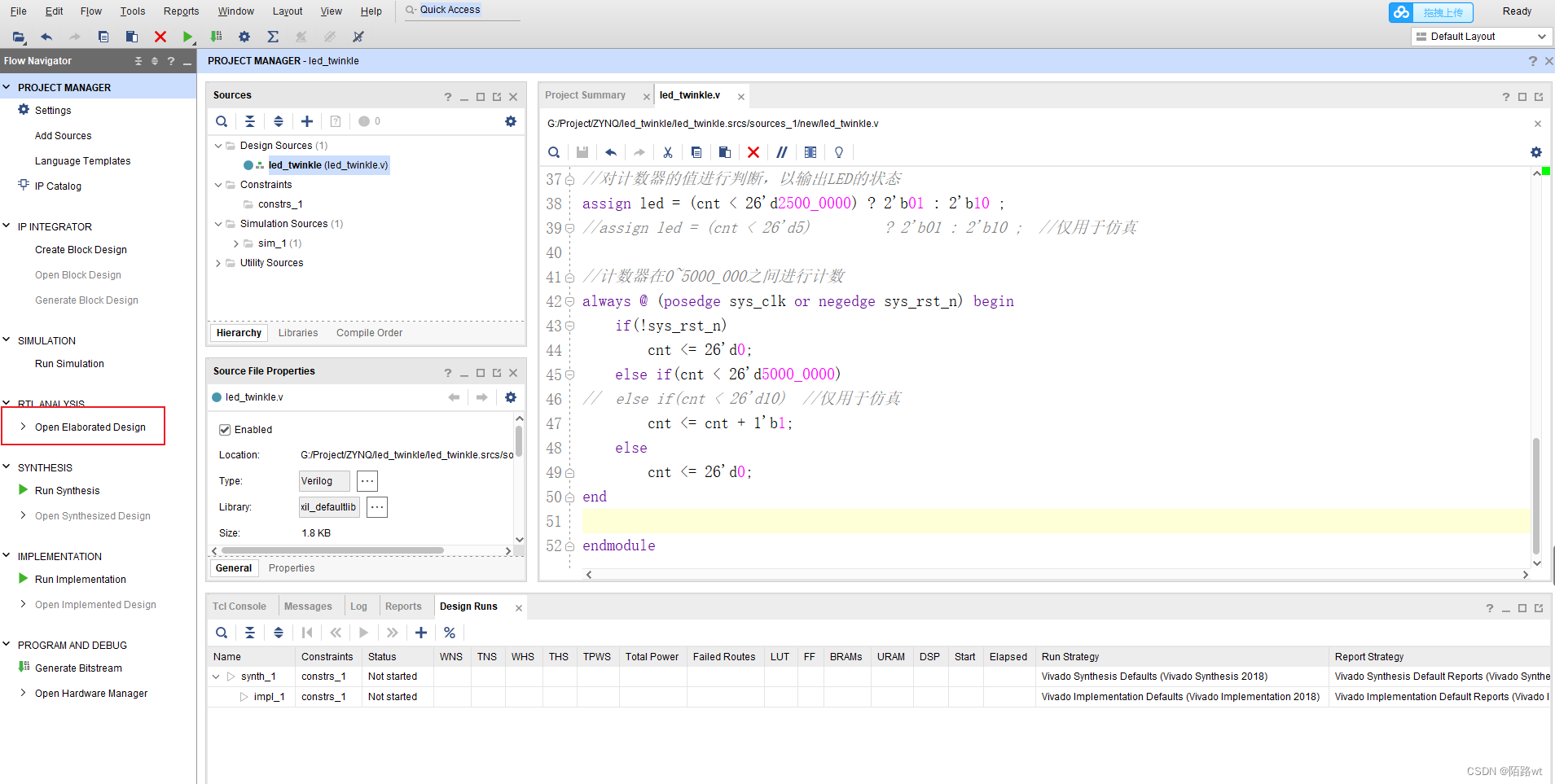

书写代码(拷贝的正点原子的例程)

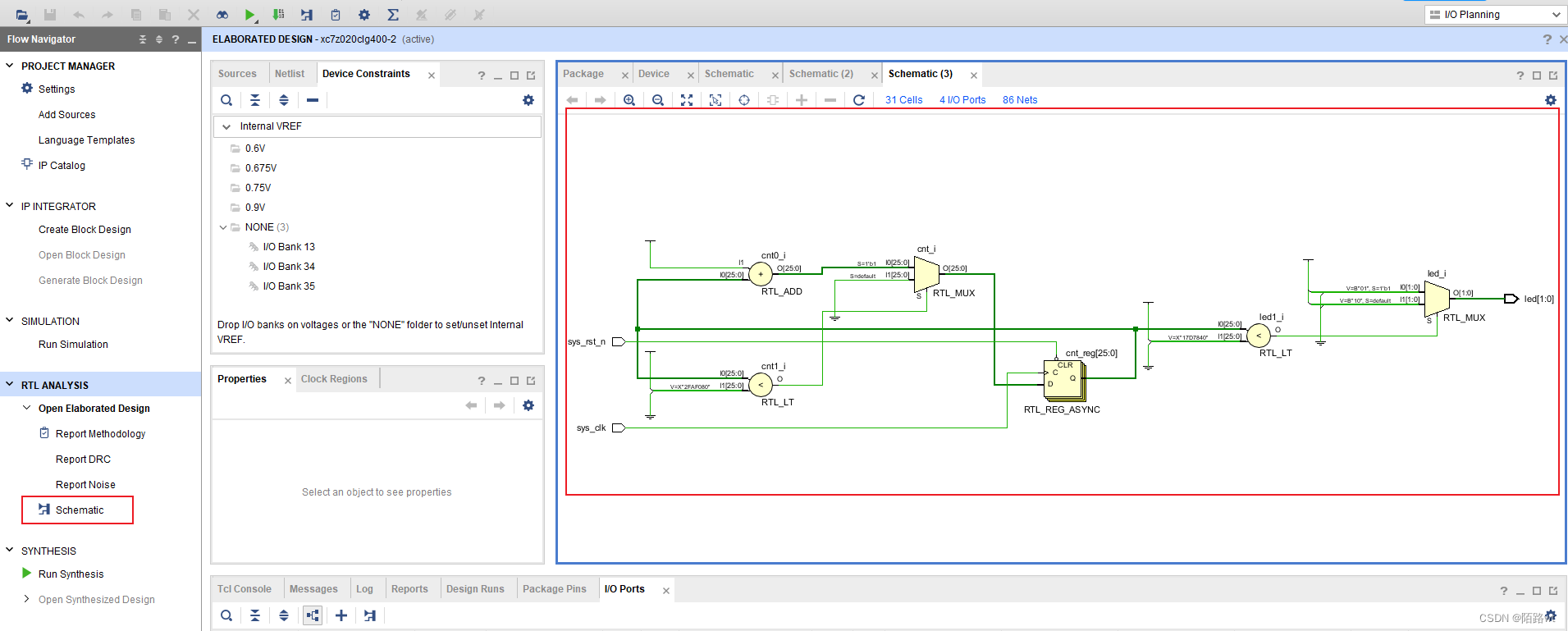

点击综合,生成设计后的原理图

点击综合,生成设计后的原理图

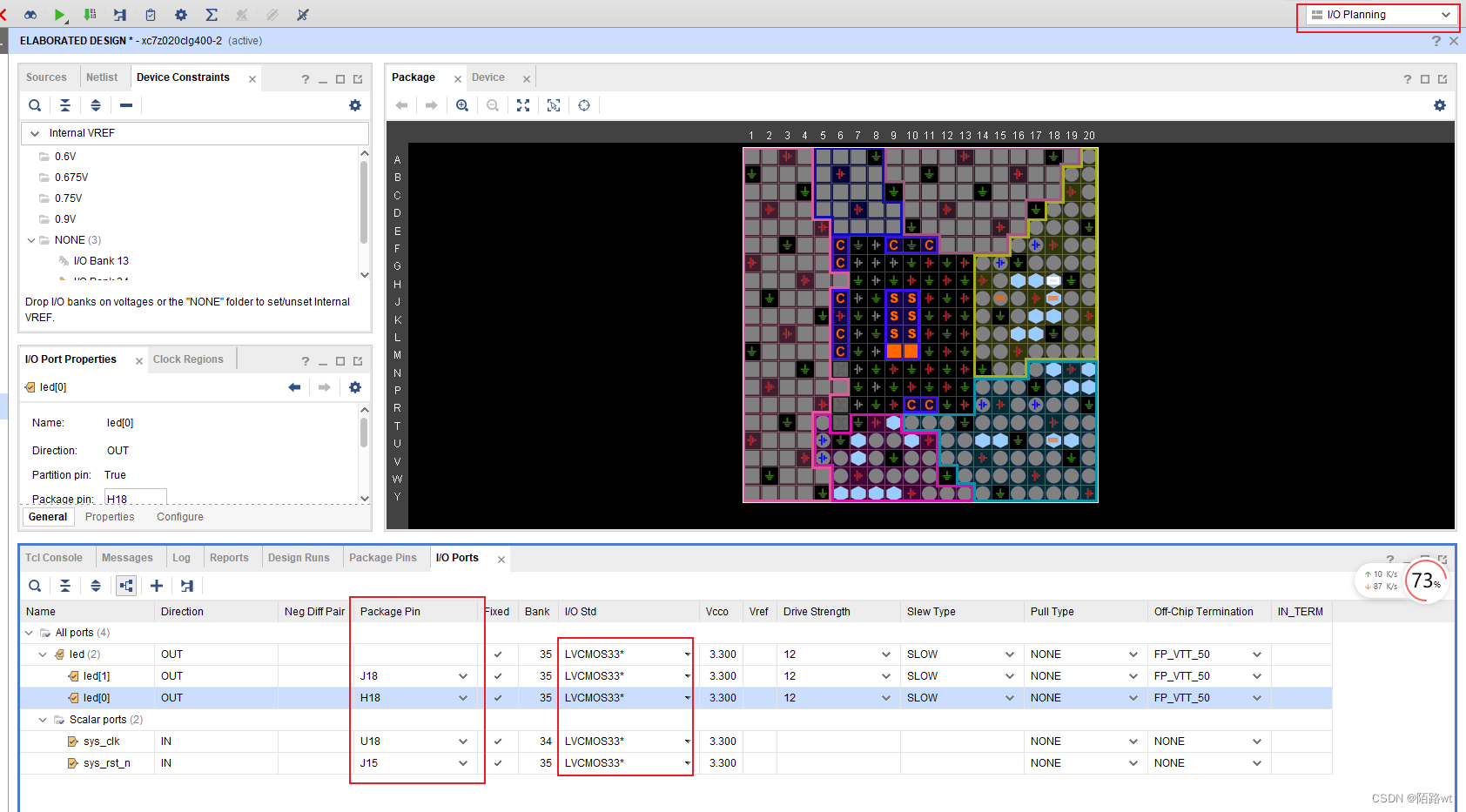

第一种方法:进行I/O引脚的分配 (需要查看电路板的原理图分配引脚,电压选3.3v)

保存文件,生成引脚的分配文件

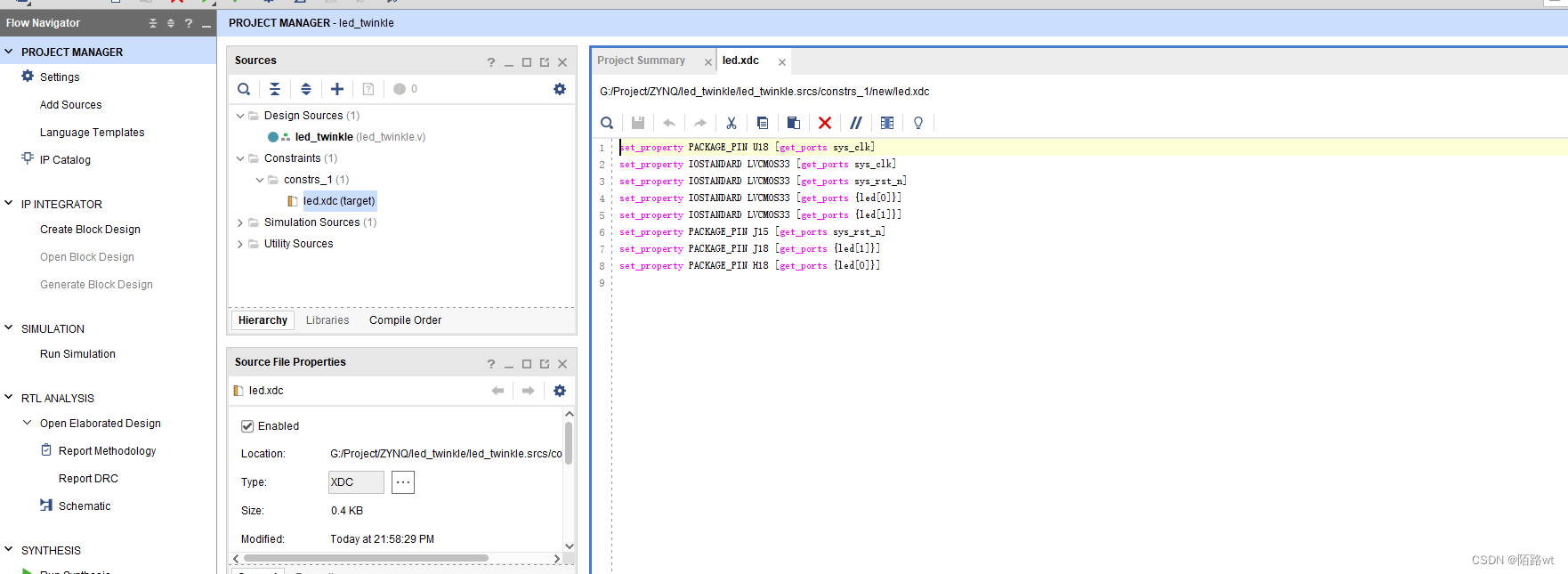

关闭RTL ANALSIS,就可以查看到xdc的文件 (此工程简单,故只有引脚的约束,没有时序的约束)

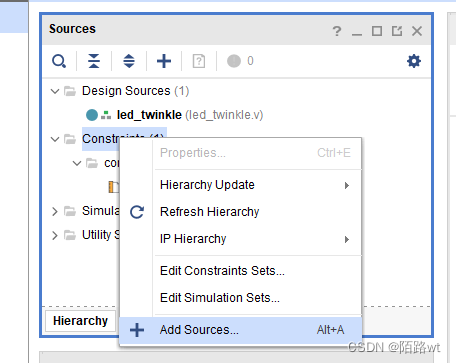

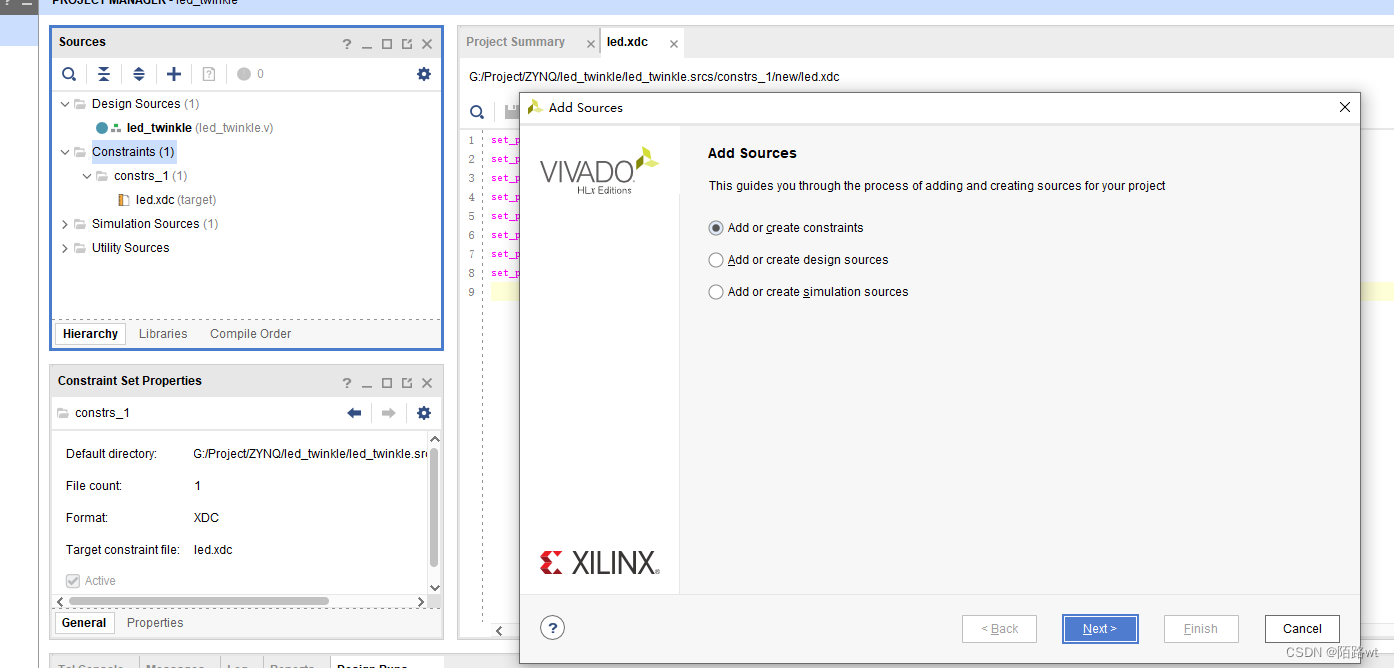

第二种方法:直接选中约束,创建一个约束

然后添加约束的程序(正点原子的资料里有)

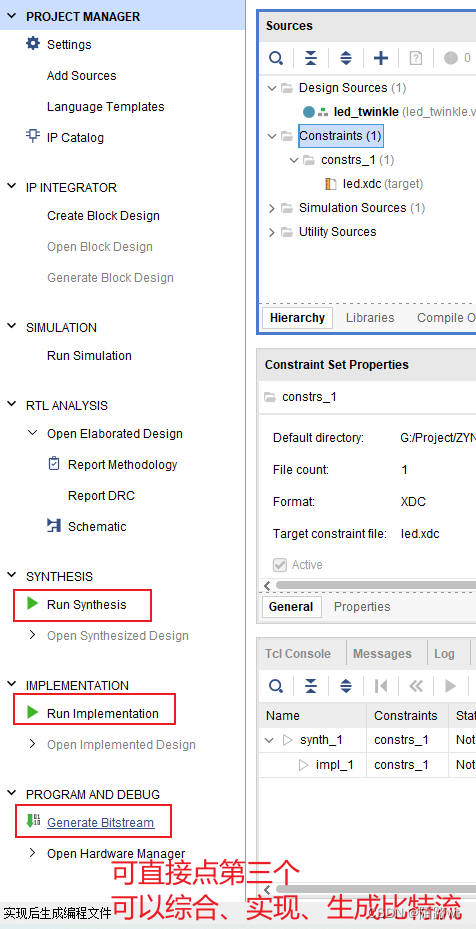

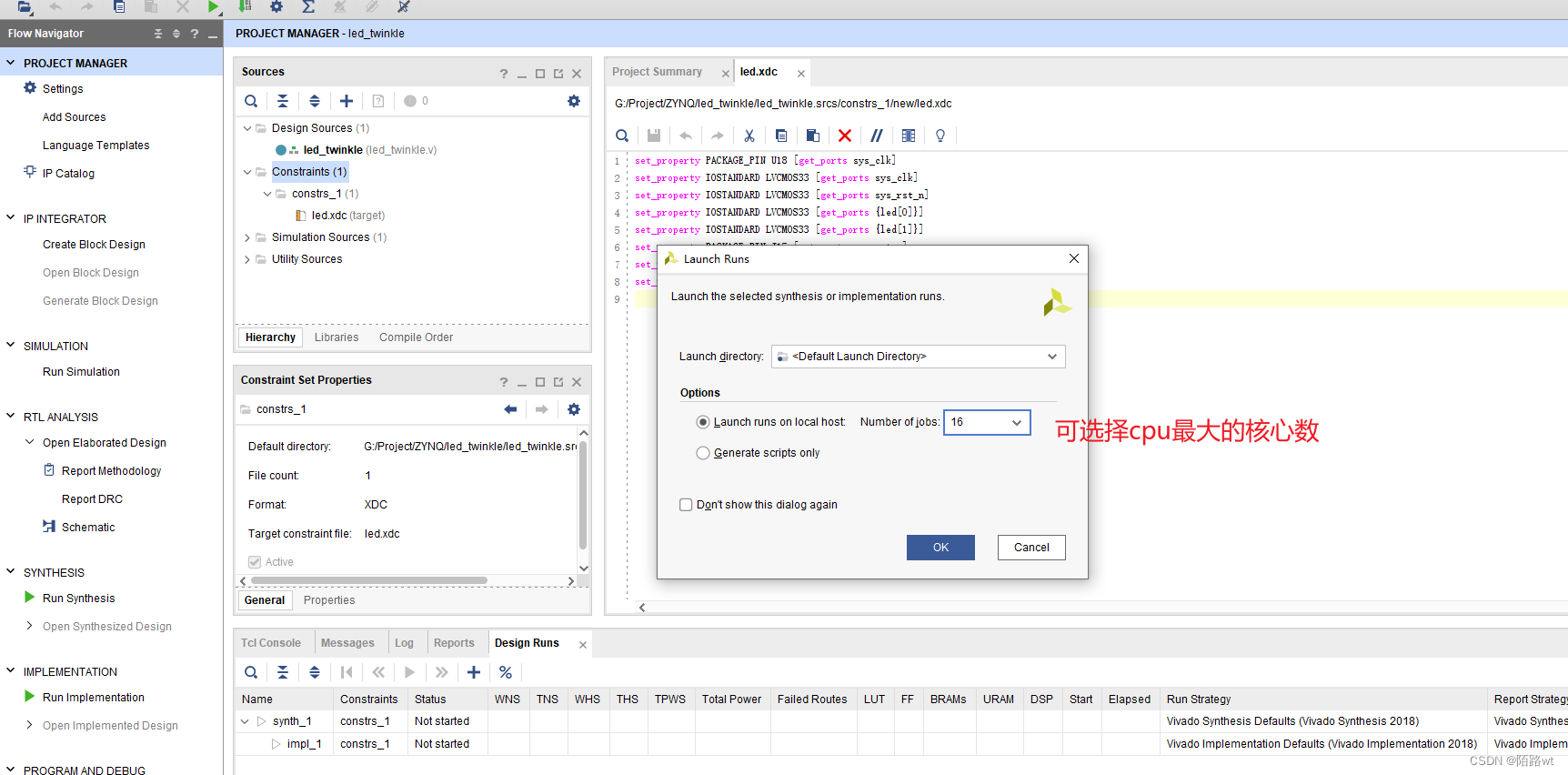

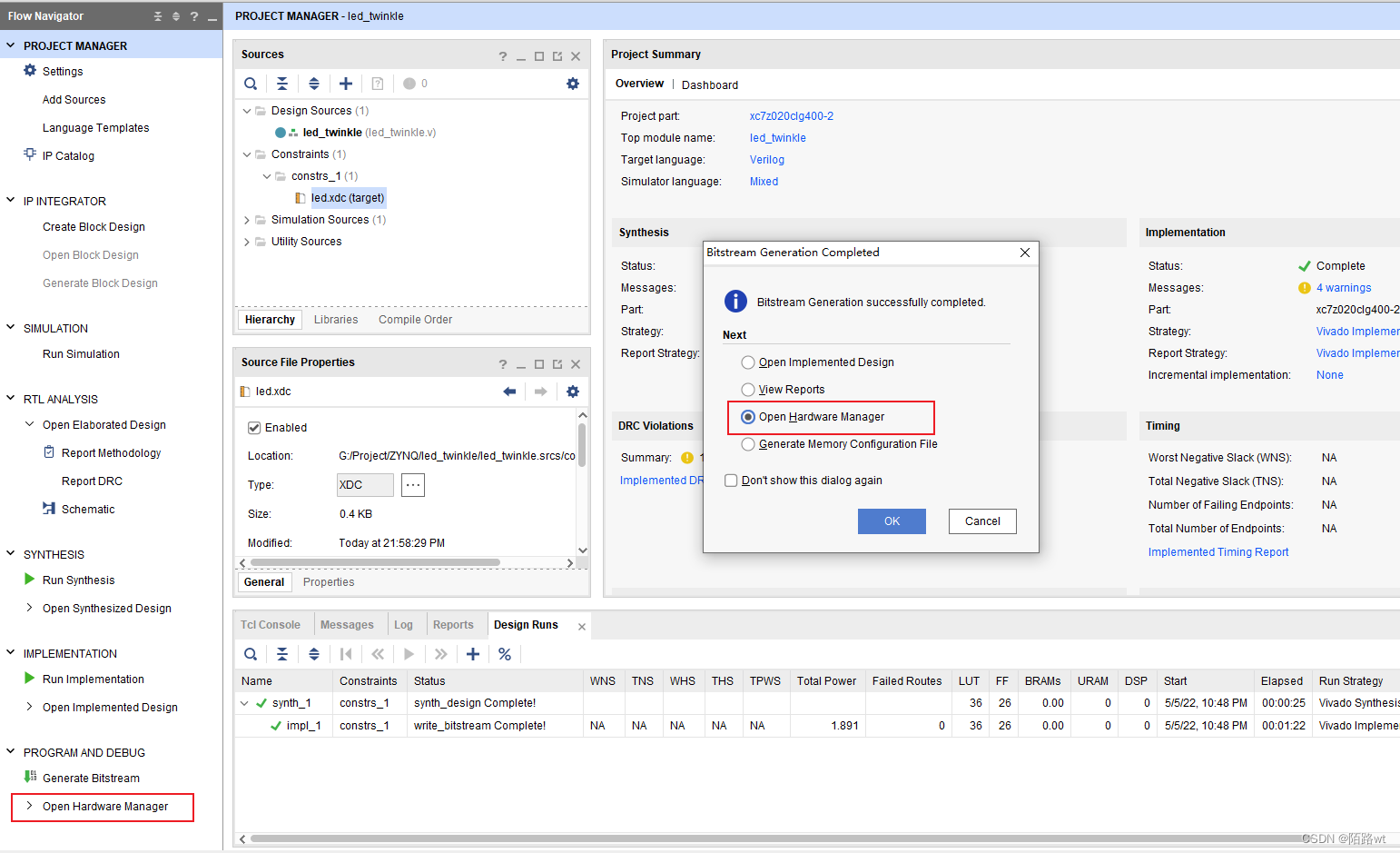

综合、实现、生成比特流

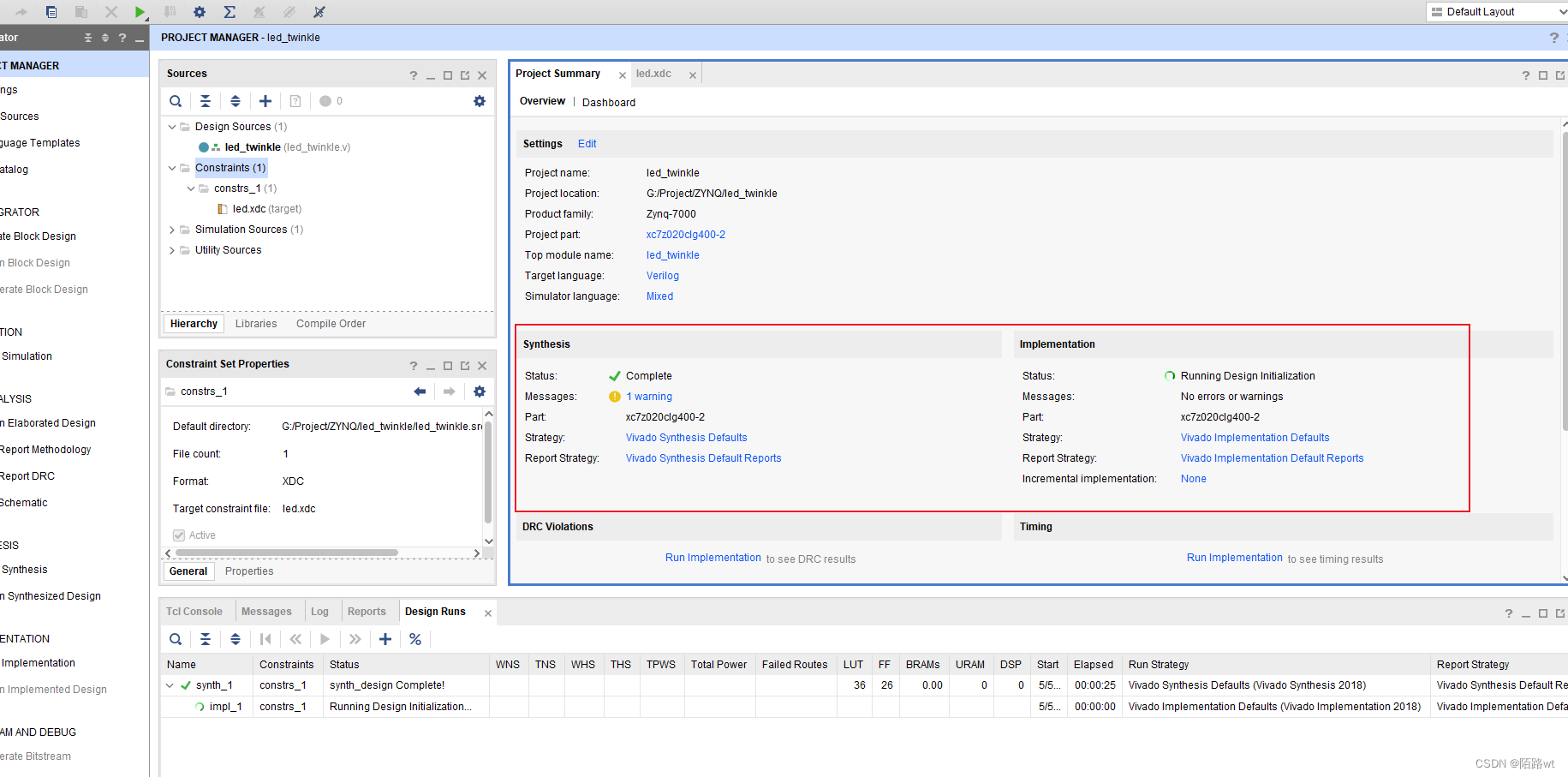

等待,观察进行到哪一步了

完成后会弹出提示,之后就可以下载程序了

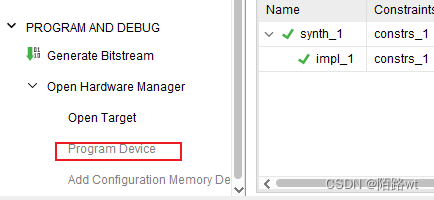

此处没连接,正常接上后就会有板子型号,点击下载就好了

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?