自SystemVerilog3.1a之后,SystemVerilog推出了一个与第三方语言进行交互的强大功能,称之为DPI,DPI的全称就是Direct Programming Interface,是SystemVerilog与其他编程语言的一种接口,目前经常被用到的是SystemVerilog与C(C++)之间的交互,本文示例也将以C语言和SystemVerilog示例。

0 大鱼吃小鱼的DPI

在上世纪的时候,开发SuperLog的Co-Design Automation公司实现了SuperLog与C语言的交互,称之为CBlend技术。同时,很多其他EDA公司也开始开发类似的技术。2001年的时候Co-Design Automation公司向Accellera发布了SuperLog扩展综合子集ESS。2002年Synopsys收购了Co-Design Automation,Synopsys结合Co-Design开发的SuperLog与C语言交互的CBlend技术也开发了适合自己仿真器的交互的 DirectC接口(VCS DirectC),然后将DirectC和CBlend捐献给了Accellera,Accellera的SystemVerilog标准委员会把这两个捐献技术合并在一起,并定义了DPI接口,使得DPI能够与任何仿真器一起工作。又经过若干年的发展,DPI又进阶为了DPI-C(IEEE 1800-2012之后),渐渐地DPI逐步的被DPI-C替换成为了主流。后续我们说的DPI如果没有特殊说明均指DPI-C。

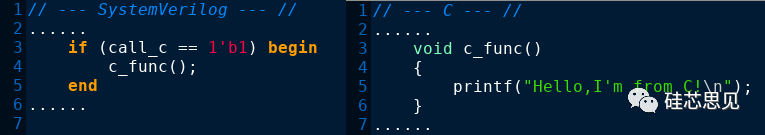

通过DPI可以在SystemVerilog中调用C语言中的function(C语言中没有task),当然,也可以通过DPI调用SystemVerilog中的task和function。如下例:

DPI实现了SystemVerilog与其他语言的接口,所以其一般由两部分组成,即SystemVerilog层和其他语言层,并且这两层彼此之间是相互独立的,两者的编译也是相互独立的,进行这样两层结构的出发点是设计人员对于其他语言开发的模块在SystemVerilog中使用的迫切需求(特别是C和C++)。在DPI的这种分层结构中,遵循的是一种“黑盒”规则:组件的规范和实现明确分开,实际实现对该语言编写代码的其余部分是透明的,而对于通过DPI使用其方法的语言为不透明的。例如,C语言编写的方法,对于通过DPI使用其的SystemVerilog来说是一个黑盒子但是SystemVerilog无需更改即可对其进行调用。那么在具体的使用过程中应该如何快速的使用DPI-C呢,我们下面分别从SV调用C函数和C调用SV方法进行示例说明。

1 SV中import方法

语法:

import "DPI" [from_c_name =] [pure][context] function type

本文介绍了SystemVerilog的DPI(Direct Programming Interface)特性,它允许SystemVerilog与C语言进行交互。DPI-C已经成为主流,允许在SystemVerilog中调用C函数,反之亦然。文章详细阐述了DPI的三种导入方法(context、pure和generic)及其应用场景,以及如何在SystemVerilog中export函数和任务给C程序。通过实例展示了DPI的使用步骤,并提到了svdpi.h和svdpi_src.h头文件在C程序中的作用。

本文介绍了SystemVerilog的DPI(Direct Programming Interface)特性,它允许SystemVerilog与C语言进行交互。DPI-C已经成为主流,允许在SystemVerilog中调用C函数,反之亦然。文章详细阐述了DPI的三种导入方法(context、pure和generic)及其应用场景,以及如何在SystemVerilog中export函数和任务给C程序。通过实例展示了DPI的使用步骤,并提到了svdpi.h和svdpi_src.h头文件在C程序中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?