题外话:西安发生了疫情(新冠和出血热),但是一切都会过去,雨后总会天晴!!!

在后仿真过程中经常会遇到关于setup和hold violation的问题,但是关于setup和hold time的产生原因和由来很多人还比较朦胧,为此本文通过解剖一个边沿触发器简要说明setup和hold产生原因。

解剖示例

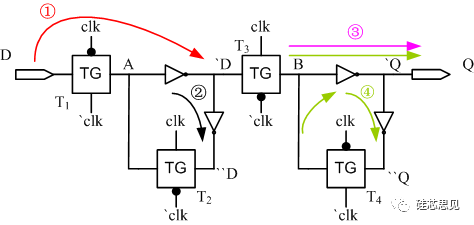

上图为触发器的简要示意图(clk和’clk为反向时钟)。T1和T4同时导通,T2和T3同时导通,且T1、T4和T2、T3导通状况互反。其中T1、T2、T3、T4均为传输门,均为电平敏感,所以所谓的时钟跳变可以理解为高低电平的相互跳变所致。而电路中实际的延时信息主要由于电信号导通时通过电子器件时耗费的时间。

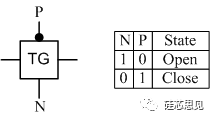

【注】传输门的开关状态如下图所示。

工作过程

clk和’clk互为相反的信号,clk为低电平(’clk为高电平)时,T1和T4导通,此时数据进入到`D和``D,因为此时T4导通,图中绿色箭头线中的数据保持上一拍的数据结果。

当clk高电平(’clk为低电平&#x

本文通过解剖边沿触发器的工作过程,详细解释了setup和hold时间的概念及重要性。setup时间指数据在时钟上升沿之前必须保持不变的时间,hold时间则是在时钟上升沿之后数据需要保持稳定的时间。文章还讨论了setup和hold为负值的特殊情况,帮助读者深入理解数字电路中的定时违规问题。

本文通过解剖边沿触发器的工作过程,详细解释了setup和hold时间的概念及重要性。setup时间指数据在时钟上升沿之前必须保持不变的时间,hold时间则是在时钟上升沿之后数据需要保持稳定的时间。文章还讨论了setup和hold为负值的特殊情况,帮助读者深入理解数字电路中的定时违规问题。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

800

800

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?