关于PLL(词条来源于Kimi):

锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够锁定一个振荡信号的频率和相位与一个参考信号。锁相环广泛应用于电子工程中,主要有以下几个用途:

-

频率合成:通过改变PLL中的调谐参数,可以生成具有不同频率的信号,这在无线通信、广播和电子音乐合成等领域非常重要。

-

时钟恢复:在数据通信中,PLL可以用来从接收到的信号中恢复时钟信号,以确保数据的正确同步。

-

频率调制/解调:在调制过程中,PLL可以用于调整载波信号的频率以编码信息;在解调过程中,PLL可以用来跟踪接收信号的频率变化,从而提取出原始信息。

-

时钟分配:在数字电路设计中,PLL可以用于分配时钟信号,确保不同部分的时钟同步。

-

噪声抑制:PLL具有滤波器特性,可以抑制高频噪声,提高信号的稳定性。

-

信号跟踪:在某些应用中,PLL可以用于跟踪信号的变化,例如在无线通信中跟踪移动设备的频率变化。

-

电压控制振荡器(VCO):在PLL中,VCO是一个关键组件,它可以在电压控制下改变频率,这在许多电子设备中都有应用。

-

同步:在多相位或多通道系统中,PLL可以用来同步不同的信号或数据流。

锁相环的基本组成部分通常包括相位检测器(Phase Detector)、环路滤波器(Loop Filter)、电压控制振荡器(VCO)和反馈路径。通过这些组件的相互作用,PLL能够锁定并跟踪外部信号的频率和相位。

程序练习:

1、新建工程,按部就班;

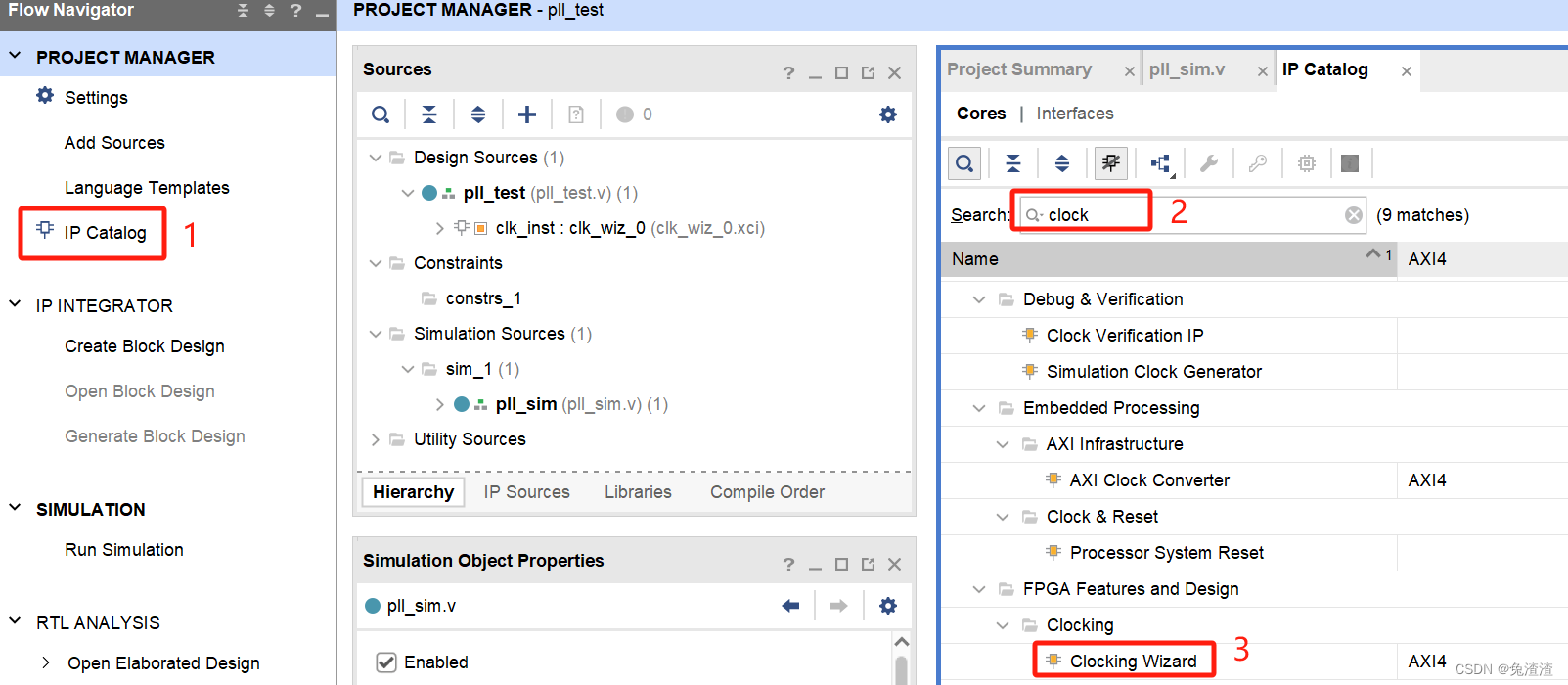

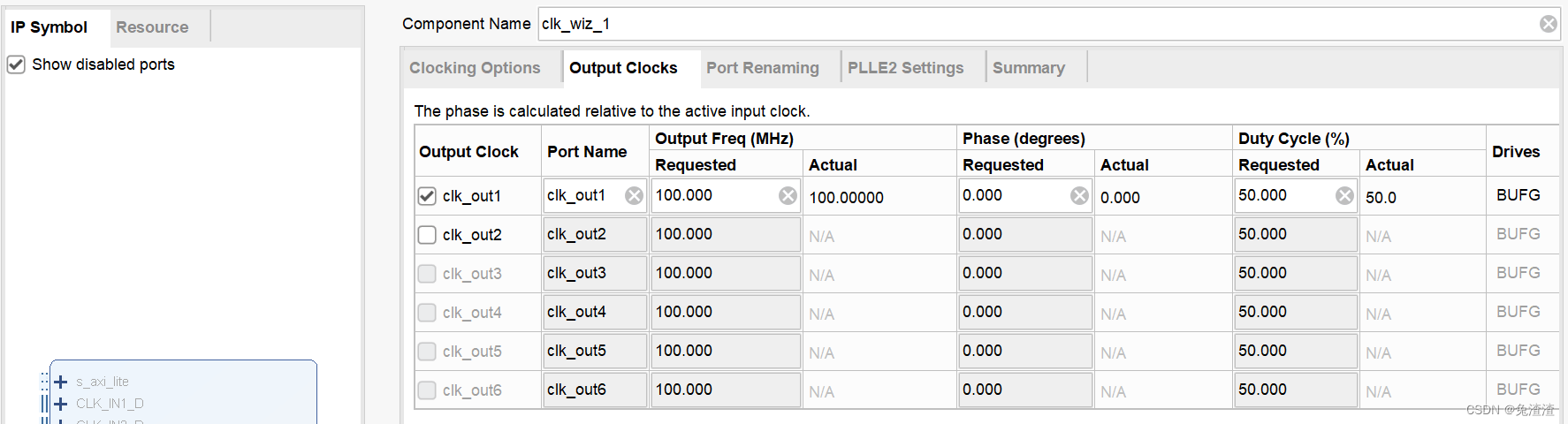

2、添加IP核,设置需要输出时钟的频率;

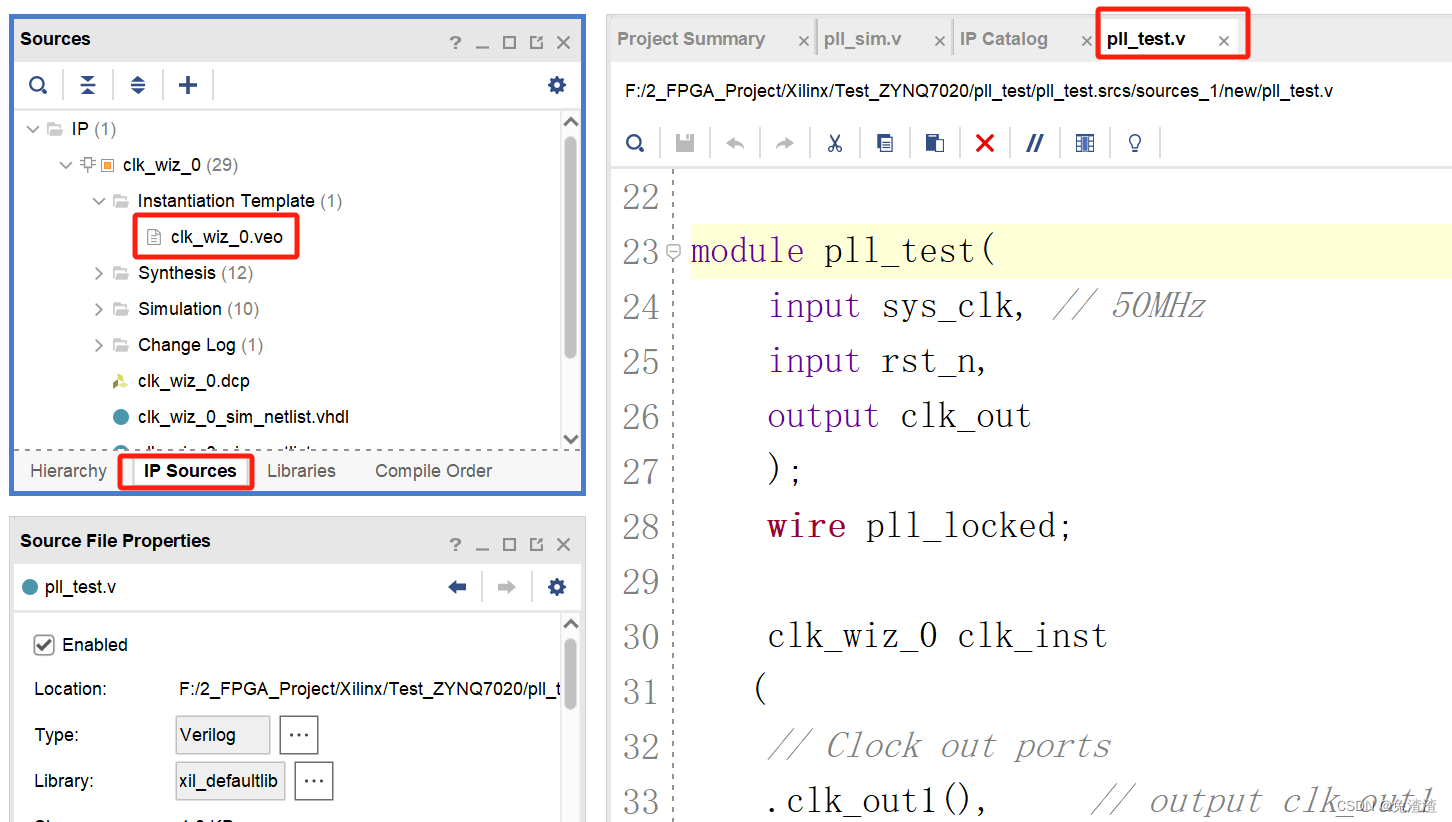

3、按照模板编写pll实例文件;

4、编写仿真文件,进行仿真;

注:这里发现用Vscode安装插件编写代码更加方便简洁,后续需完整搭建。

5、关联IO。

声明:仅作学习记录

1953

1953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?