野火学习备忘录——PLL

PLL(Phase Locked Loop,即锁相环)是最常用的 IP 核之一,其性能强大,可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟,实际上,即使不想改变输入到 FPGA 时钟的任何参数,也常常会使用 PLL,因为经过 PLL 后的时钟在抖动(Jitter)方面的性能更好一些。Altera 中的 PLL 是模拟锁相环,和数字锁相环不同的是模拟锁相环的优点是输出的稳定度高、相位连续可调、延时连续可调;缺点是当温度过高或者电磁辐射过强时会失锁(普通环境下不考虑该问题)。

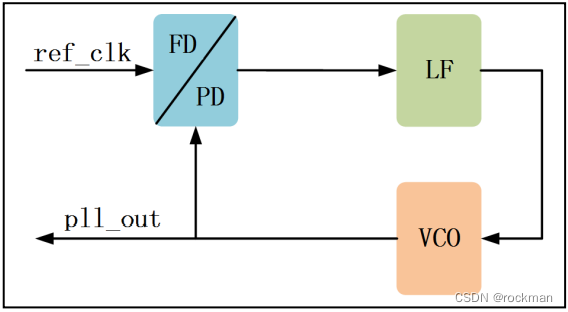

PLL的大体结构

FD/PD:鉴频鉴相器,输入鉴频鉴相器的两路信号分别是参考时钟ref_clk和比较时钟,通过计较两个时钟的大小,如果两个时钟相等,则鉴频鉴相器输出为0,如果参考时钟大于比较时钟,鉴频鉴相器会输出一个变大成正比的值,反之则会输出一个变小成正比的值。

LF:环路滤波器,鉴频鉴相器输出的值通过环路滤波器 用于控制噪声的带宽,滤掉高频噪声。同还会输出电压幅值

VCO:压控振荡器,自身有一个基准的震荡频率。输入到压控振荡器信号的幅度越高,则压控振荡器的输出的频率越高。

假设输入的参考时钟为50MHz,VCO的基准频率为10MHz,则FD/PD会输出一个变大的值,随之LF输出的电压幅度也会变大,最后VCO输出的频率也会变大 。直到比较频率等于参考频率,就能稳定输出。

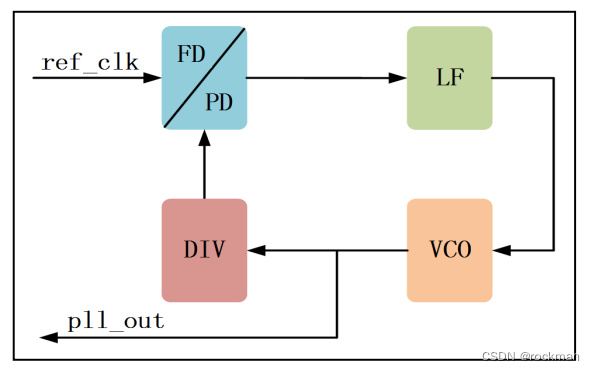

倍频PLL大概结构图

DIV为分频器,假设DIV为2分频,参考频率为50MHz,则VCO的输出比较频率应为100MHz。

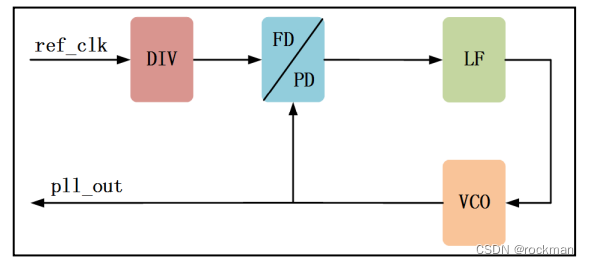

分频的PLL大概结构图

如果想要一个25MHz的频率,则DIV为2分频。

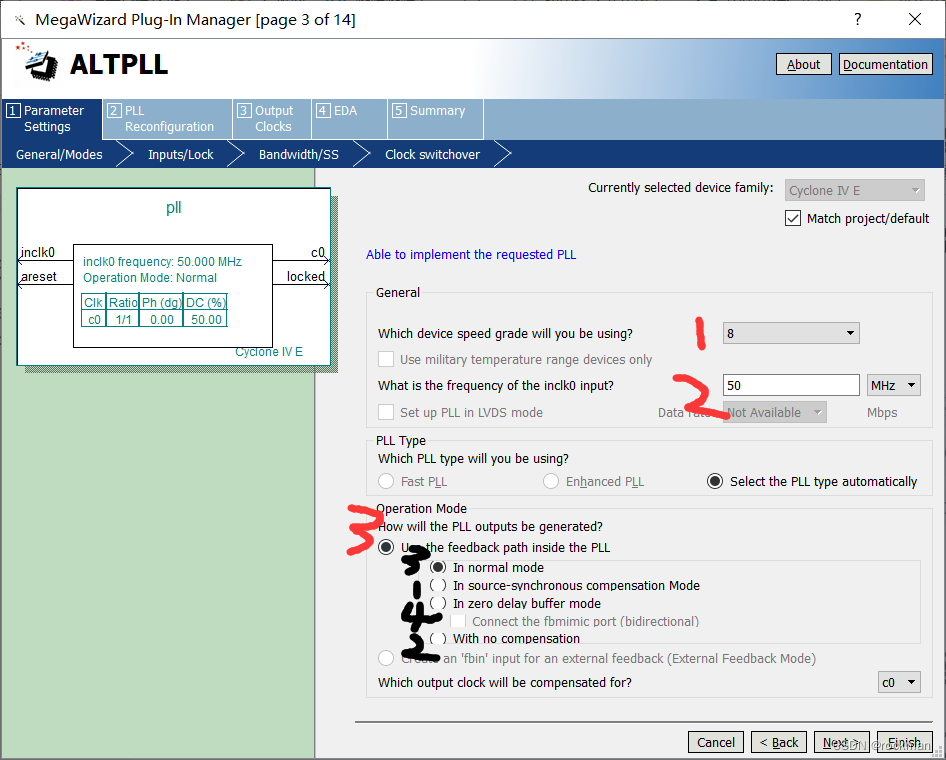

下面我们就来配置PLL.

一

1.为速度等级,数字越大,速度等级越低,越小则越大。

2.此为输入的时钟频率。

3.PLL输出的四种模式

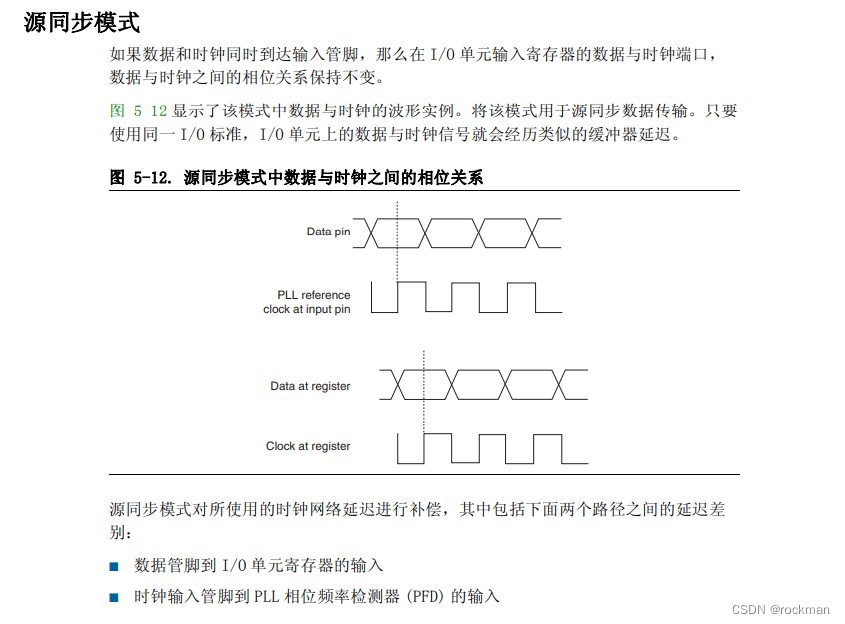

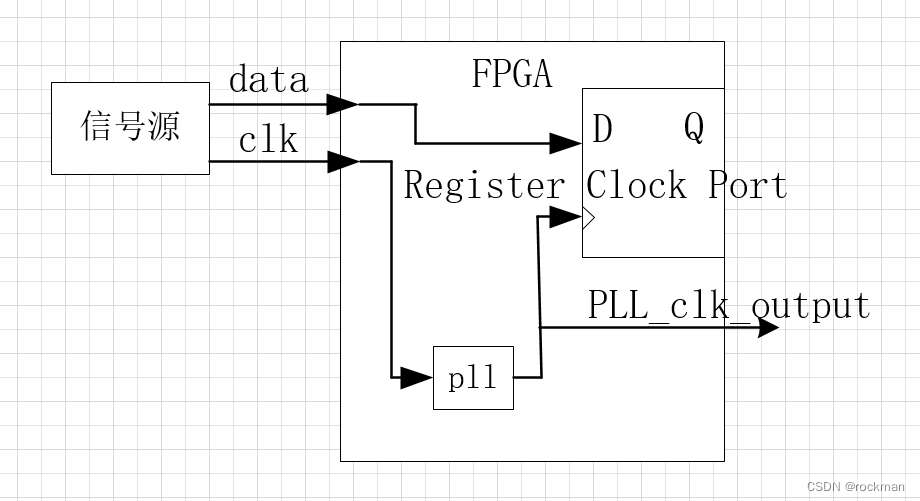

第一种,源同步模式,常用在高速的数据接口。

由官方数据手册可知,源同步模式保证数据和时钟在进入寄存器之前还保持着原来的相位关系。

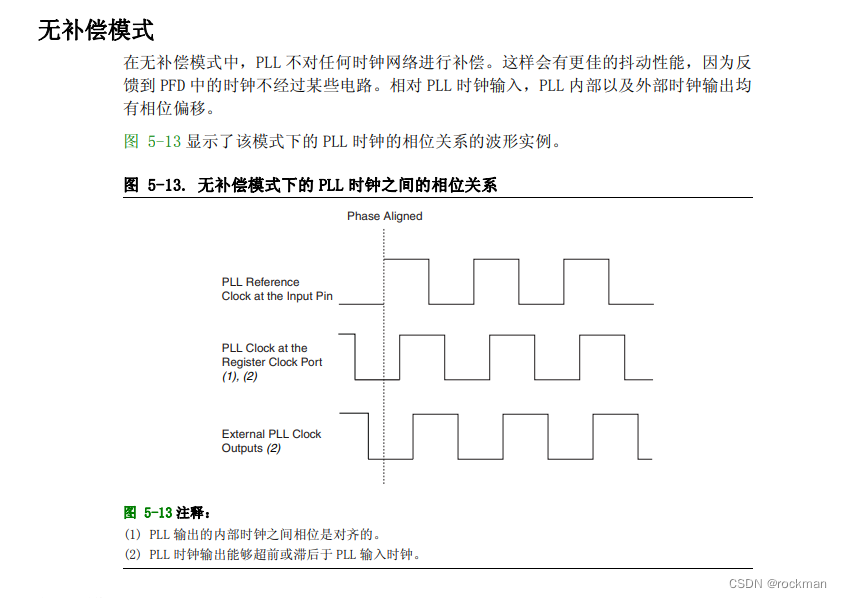

第二种是无补偿模式

锁相环不对时钟做任何的补偿处理,当时钟达到寄存器或者直接输出时钟时,相位可能超前或者滞后与原来的相位关系。

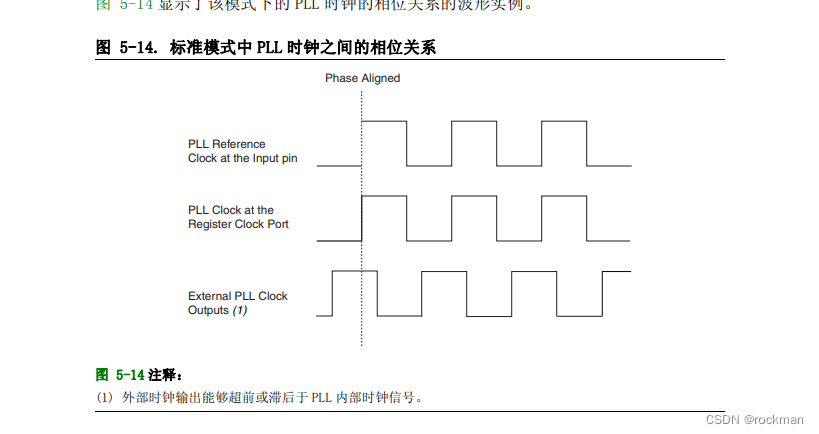

第三种时标准模式

时钟经过PLL到寄存器是有补偿的,而直接输出PLL产生的时钟会有相位偏差。所以标准模式一般使用在内部寄存器上,不作输出。

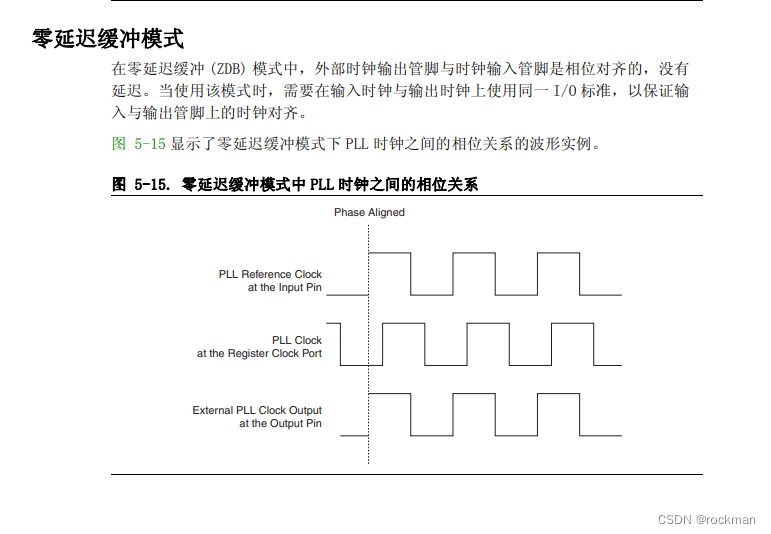

第四种是零延迟缓冲模式

由图可知,时钟在经过PLL到达寄存器时,PLL没进行补偿,所以产生了相位误差。而经过PLL输出时,是进行了补偿,所以输出时钟无原来时钟没有相位误差。所以零延迟缓冲模式适合进行时钟输出。

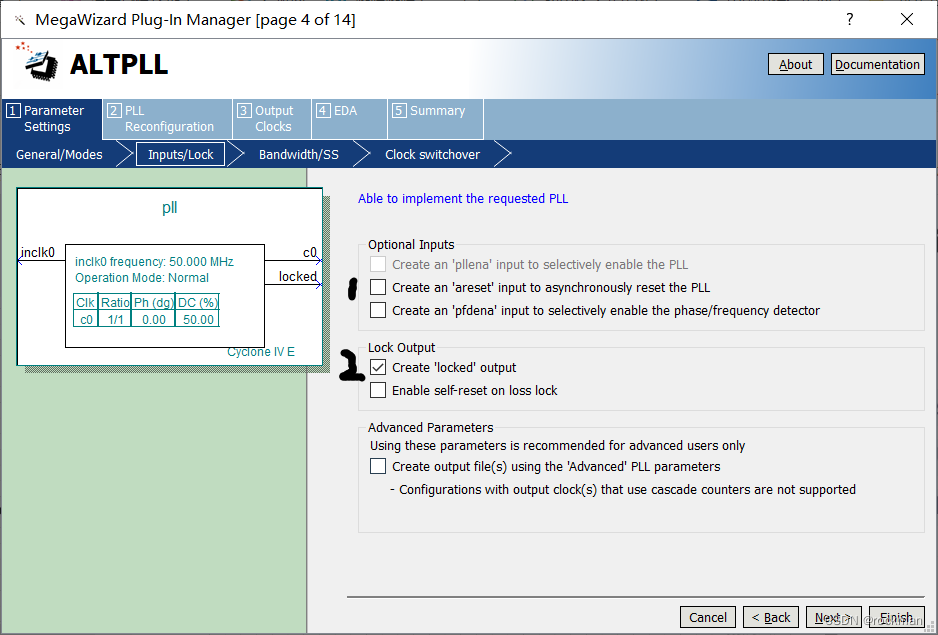

二

1.PLL异步复位。

2.锁定输出,高电平时表示PLL输出时钟可用。

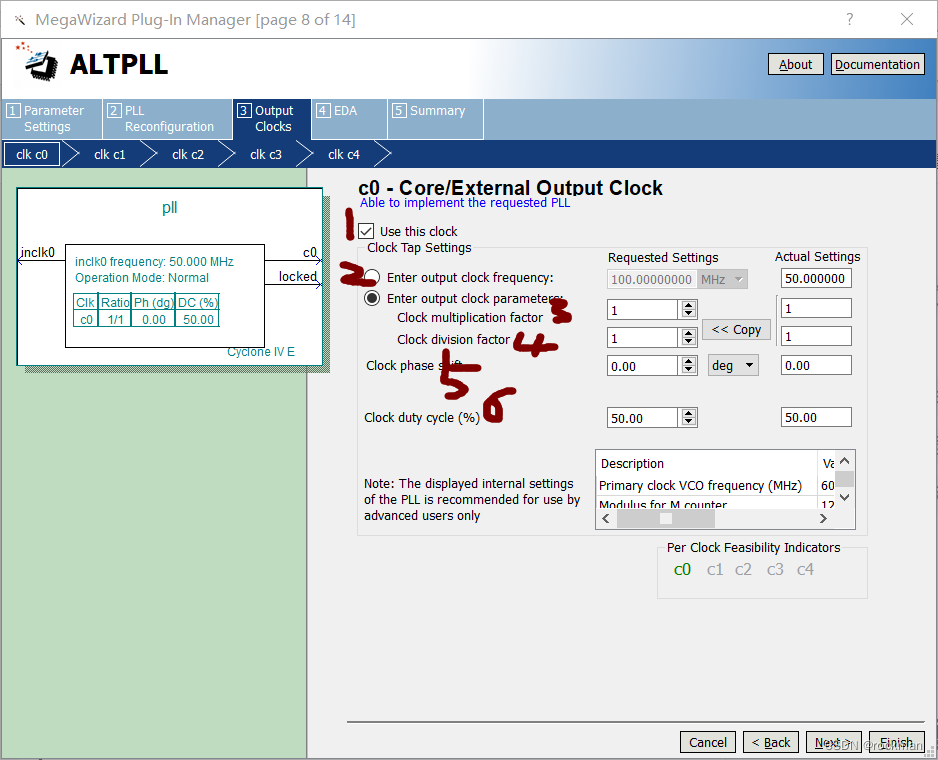

三

1.是否输出该时钟

2.直接配置,输出150M直接填150即可。

3.参数配置,乘法因子,对应上图倍频的DIV,为3时输出150M

4.除法因子,对应上图分频的DIV值,为2时,输出25M

5.相位调整

6.占空比配置。

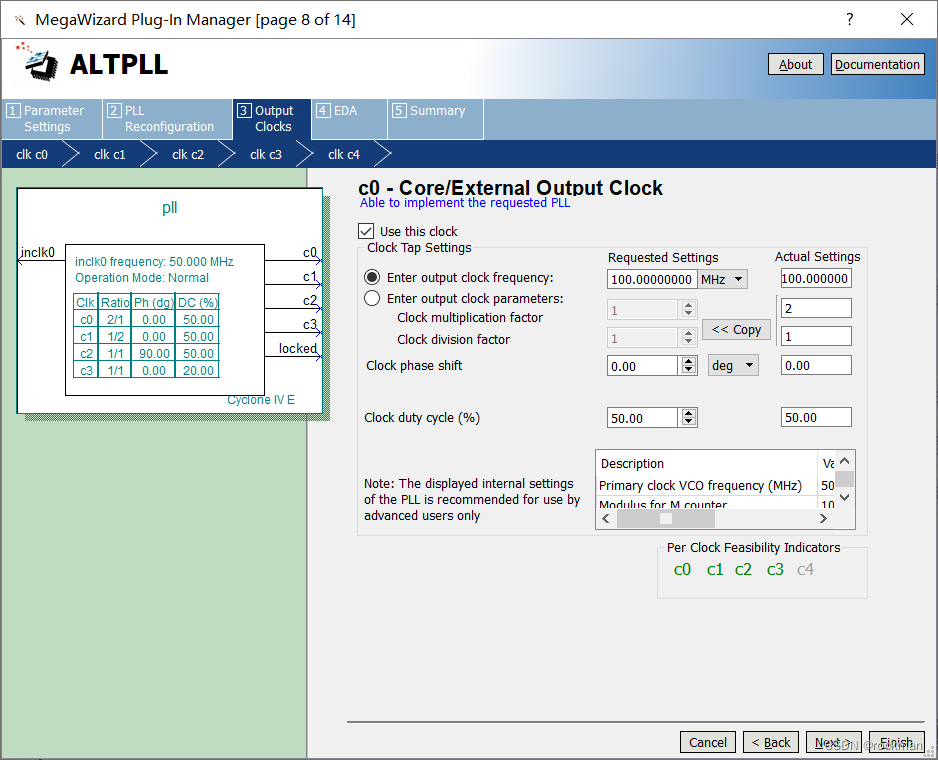

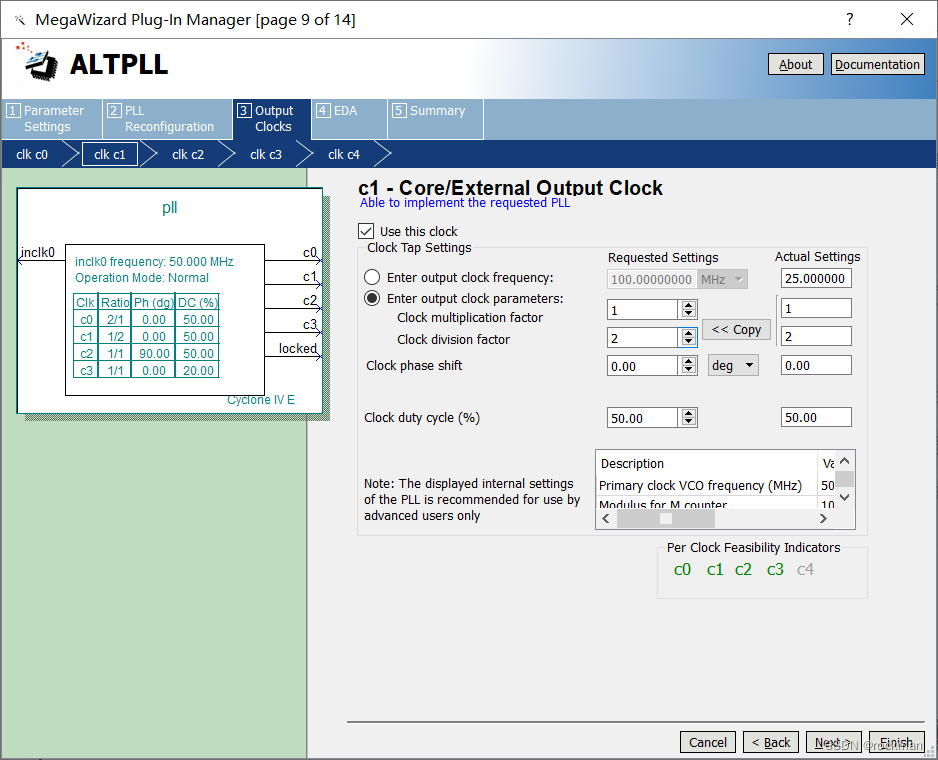

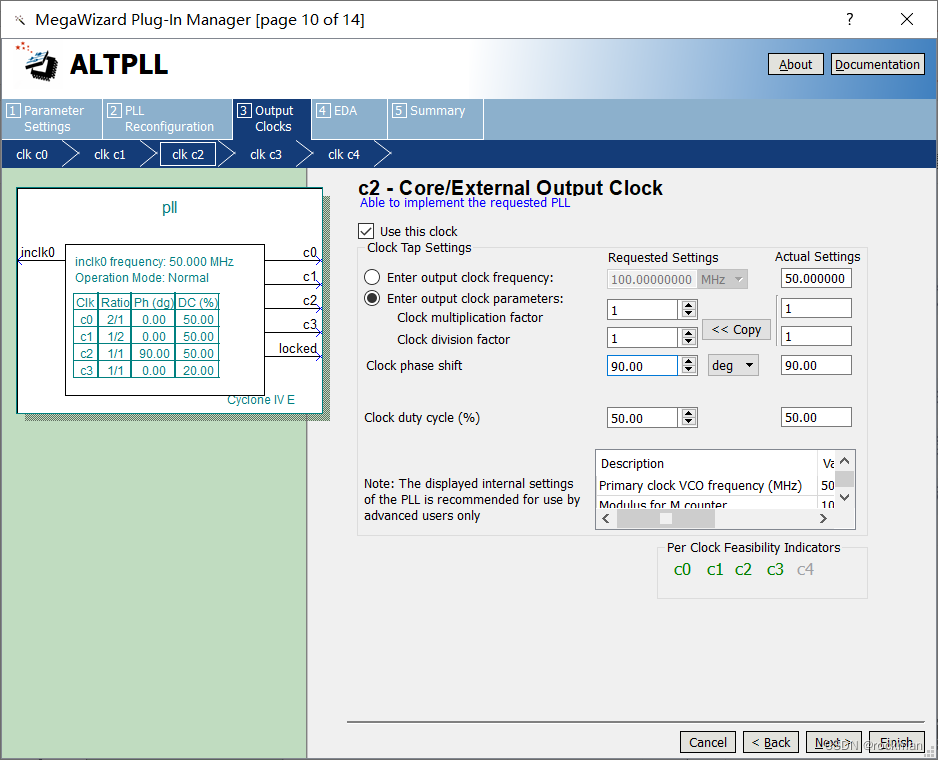

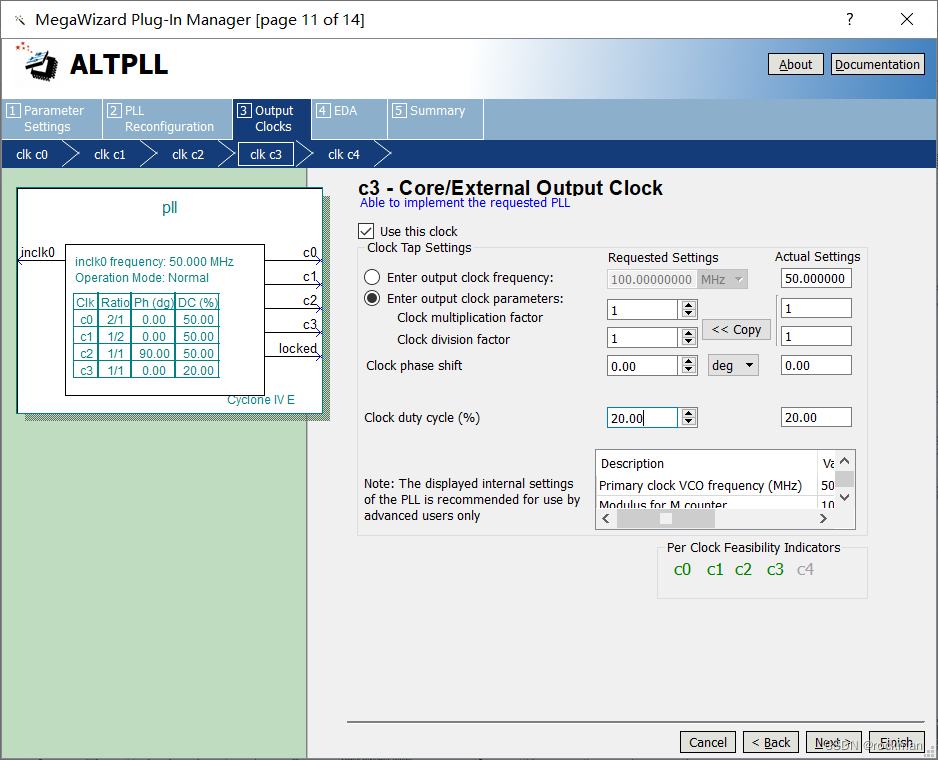

四

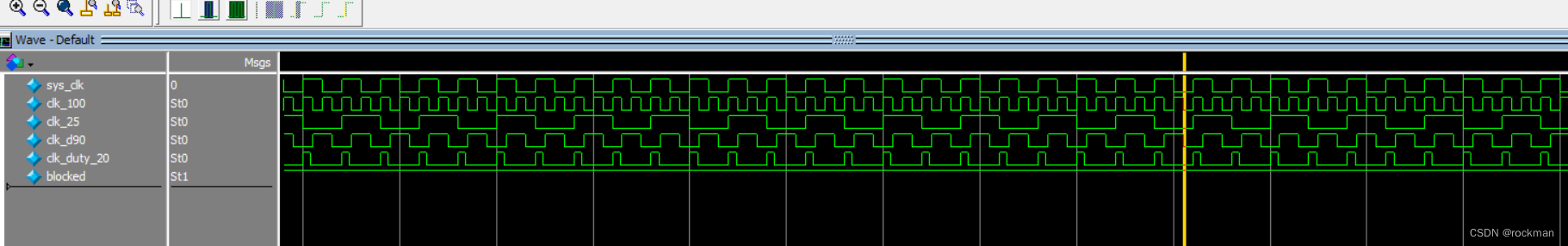

这里配置四个时钟,一个倍频100M,一个分频25M,一个相移90度,一个占空比20

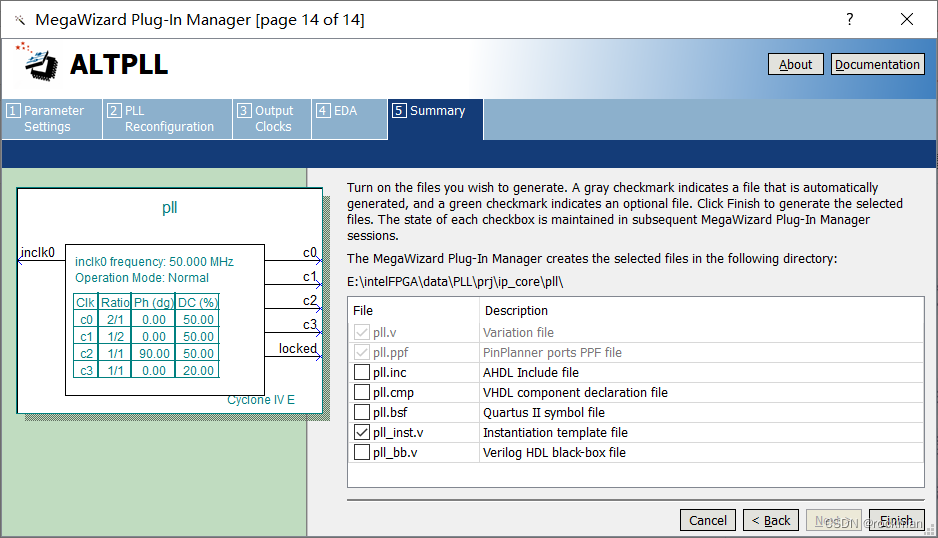

五

生成例化文件。

RTL代码

module PLL

(

input wire sys_clk ,//50MHz

output wire clk_100 ,//倍频100MHz

output wire clk_25 ,//分频25MHz

output wire clk_d90 ,//相移90度

output wire clk_duty_20 ,//20占空比

output wire blocked //锁定信号,高电平时钟有效

);

pll pll_inst (

.inclk0 (sys_clk),

.c0 ( clk_100 ),

.c1 ( clk_25 ),

.c2 ( clk_d90 ),

.c3 ( clk_duty_20 ),

.locked ( blocked )

);

endmodule

testbench

`timescale 1ns/1ns

module tb_PLL();

reg sys_clk;

wire clk_100 ;

wire clk_25 ;

wire clk_d90 ;

wire clk_duty_20 ;

wire blocked ;

initial

begin

sys_clk = 1'b0;

end

always #10 sys_clk = ~sys_clk;

PLL PLL_inst

(

.sys_clk (sys_clk),//50MHz

.clk_100 (clk_100),//倍频100MHz

.clk_25 (clk_25),//分频25MHz

.clk_d90 (clk_d90),//相移90度

.clk_duty_20 (clk_duty_20),//20占空比

.blocked (blocked) //锁定信号,高电平时钟有效

);

endmodule

modelsim仿真结果

6196

6196

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?