一. 时钟是什么

时钟:时钟的作用非常重要。它不仅用于计算时间,还用于同步和调度各种操作。例如,时钟可以用于控制中央处理器(CPU)的执行速度,确保指令按照规定的时间间隔执行。时钟也用于同步输入和输出设备,使它们按照正确的时间顺序进行数据的传输和处理,在计算机系统中用于测量和同步时间的设备或信号。使计算机系统的各个组件和操作按照一定的时间间隔进行工作。

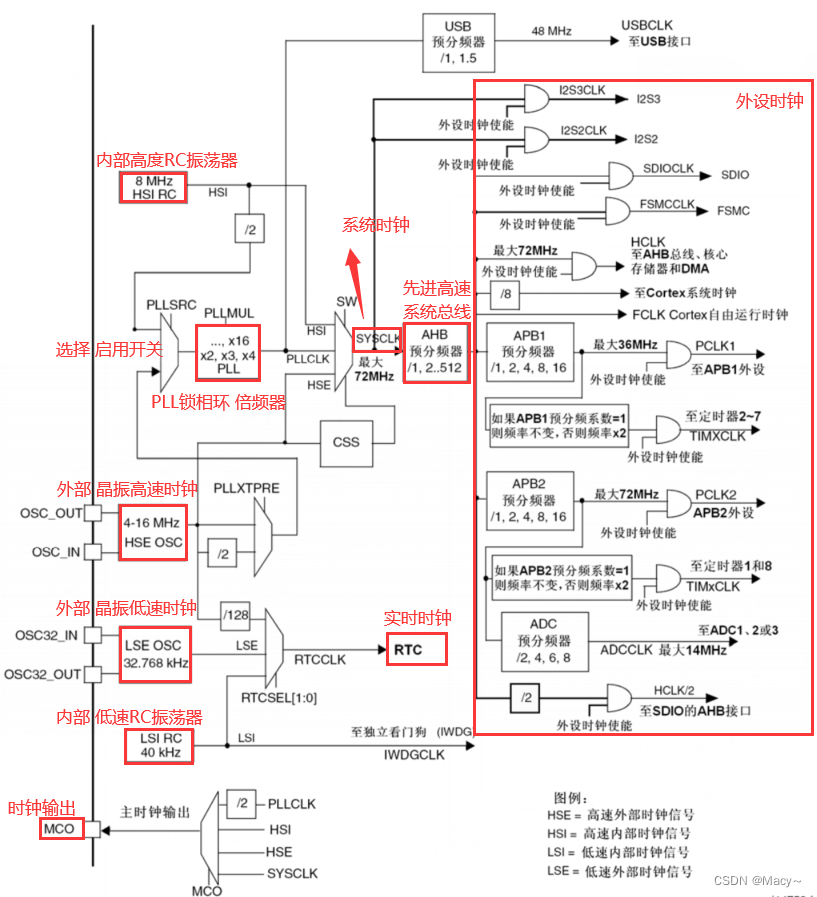

二. 时钟系统

时钟系统:时钟系统是由时钟、时钟源、时钟控制器组成的,也是计算机或电子设备中用于提供时钟信号的硬件和软件组件的集合。

时钟:为外部设备提供提供工作频率的方波信号,方波信号的来源是时钟源的分频或倍频。

时钟源:由系统时钟源和次级时钟源组成,通常包括内部高速振荡器(HSI),内部低速振荡器(LSI),外部低速振荡器(LSE),外部高速振荡器(HSE),PLL等。其中,HSI和LSI是内部时钟源,LSE和HSE是外部时钟源,PLL是用于提高时钟频率的模块。这些时钟源可以单独或组合使用来为STM32芯片提供稳定和准确的时钟信号。根据具体的应用场景,可以选择不同的时钟源。

时钟控制器:是一个专门的硬件模块,用于配置和控制各种时钟源以及时钟分频器。如:配置时钟控制寄存器(RCC_CR) 、时钟配置寄存器(RCC_CFGR)、时钟中断寄存器 (RCC_CIR)、APB2 外设复位寄存器 (RCC_APB2RSTR)等等组成的。具体RCC寄存器的描述可以查阅《STM32F10xxx参考手册》的第60页开始。

三. 时钟源

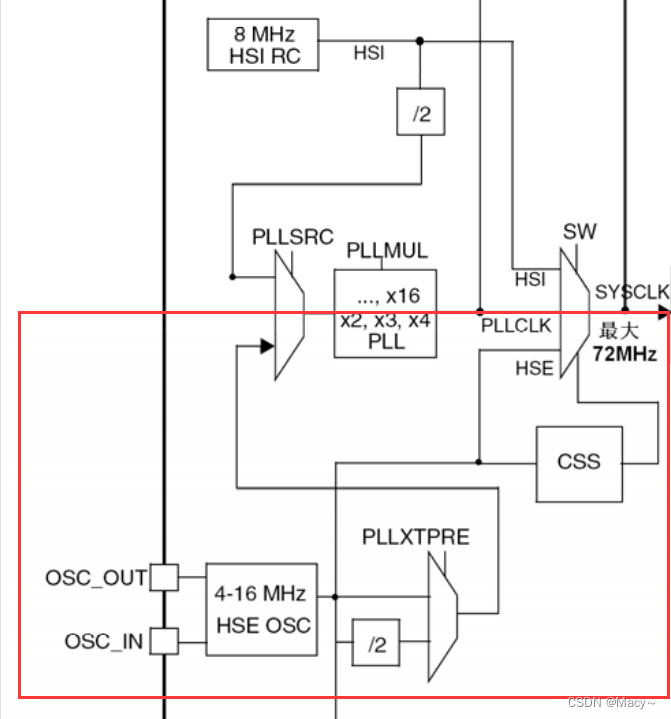

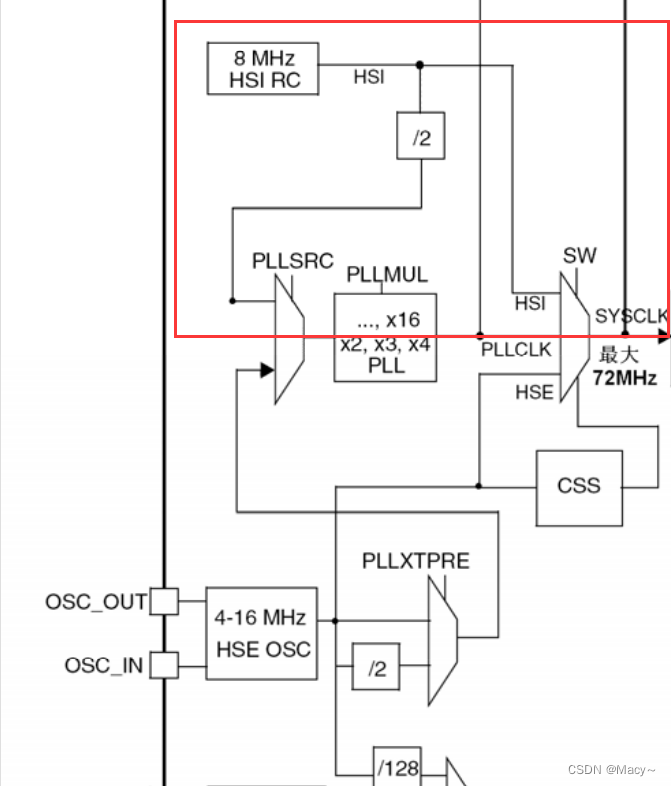

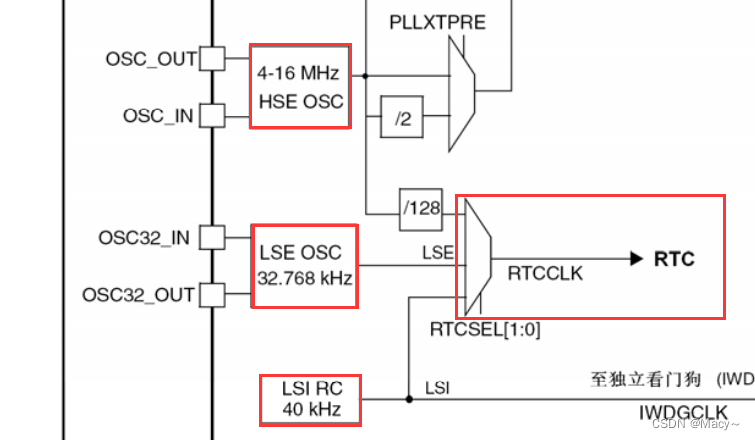

在STM32中,时钟源一般由HSE、HSI、LSI、LSE组成,而PLL则是由HSE,HSI提供的。

- HSE(外部高速时钟 - High Speed External clock signal):通常以外部晶振作为时钟源,晶振频率可取范围为4 - 16MHz,ST官方建议选用8MHz外接晶振作为STM32F103系列的微控制器的时钟源。

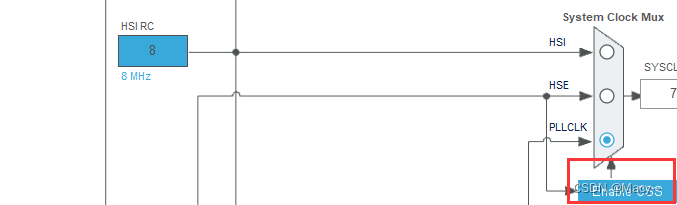

- HSI(内部高速时钟 - High Speed Internal clock signal):由片内RC振荡器产生,频率为8MHz,可直接作为系统时钟或在2分频后作为PLL输入,但是工作不稳定,即使是进行了校准它的时钟频率精度较差。

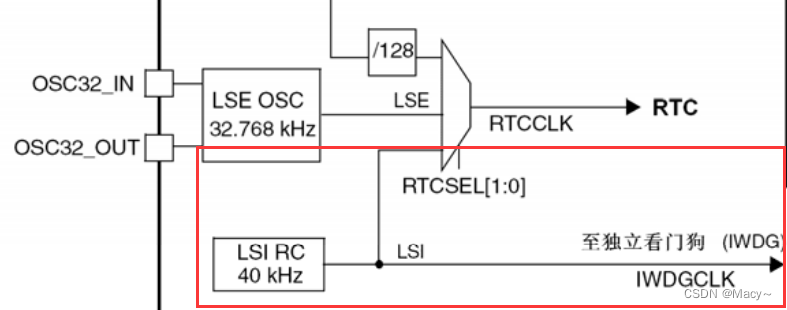

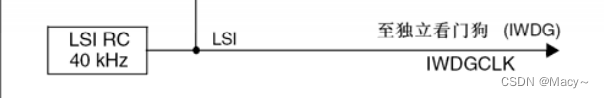

- LSI(内部低速时钟 - Low Speed Internal clock signal):由片内RC振荡器产生,可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟,频率为40KHz。

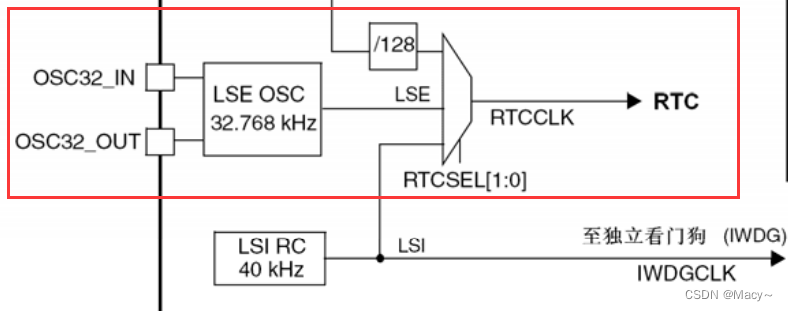

- LSE(外部低速时钟 - Low Speed External clock signal):通常以低速外部晶体或陶瓷谐振器作为时钟源,主要提供实时时钟模块或其他定时功能提供一个低功耗且精确的时钟源,一般采用32.768KHz。

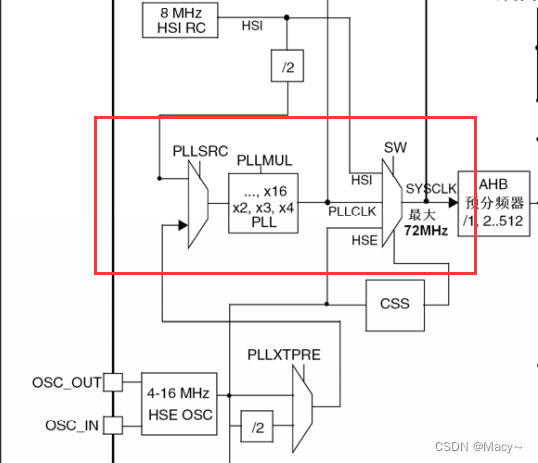

- PLL(锁相回路或锁相环 - Phase Locked Loop):内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟。但是PLL的输出频率不可以超过72MHz。

四. 系统时钟以及分频得到的外设时钟

系统时钟(SYSCLK)由多路选择器SW根据用户设置选择PLLCLK、HSE或HSI中的一路数得出得到的。它的最高频率为72MHz,是STM32F103系列微控制器外设时钟来源。

系统时钟(SYSCLK)经过AHB预分频输出得到STM32F103系列微控制器的各个部件

-

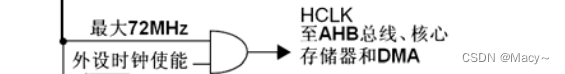

HCLK:先进高速系统总线AHB的时钟,由系统时钟SYSCLK经AHB预分频器后直接得到。通常将AHB预分频系数设置为1,HCLK即为72MHz。HCLK主要为Cortex-M3内核,存储器和DMA提供时钟信号。

-

FCLK:Cortex-M3内核的"自由运行"时钟,同样由系统时钟SYSCLK经AHB预分频器后直接得到,即使是在HCLK停止时FCLK仍能继续运行。

-

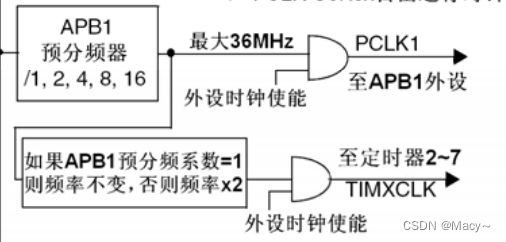

PCLK1:外设时钟,由系统时钟SYSCLK经AHB预分频器,再经过APB1预分频器后得到。将AHB的预分频器系数设置为1,将APB1的预分频器设置为2,PCLK1即为36MHz。PCLK1为挂载在APB1总线上的外设提供信号,像USART2、USART3、UART4、UART5、SPI2/I2S、SPI3/12S、I2C1、I2C3、USB、RTC、CAN、DAC、PWR、BKP、IWDG、WWDG等。

-

TIMXCLK:定时器2到定时器7的内部时钟源,由APB1总线上的时钟PCLK1经过倍频后得到的,需要使用定时器2-7中的任意一个或者是多个,必须先开启APB1总线上对应的定时器时钟。

-

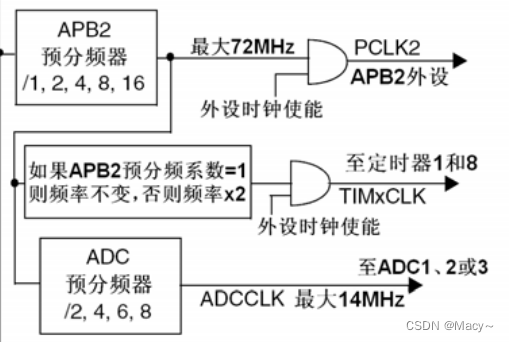

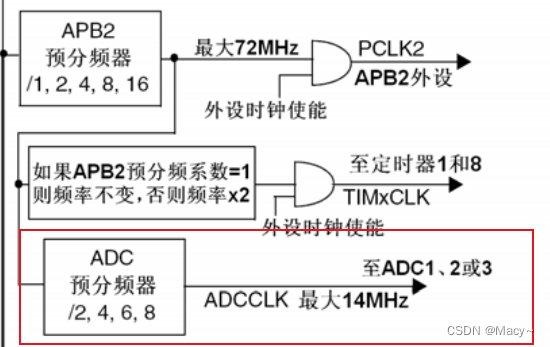

PCLK2:外设时钟,由系统时钟SYSCLK经AHB预分频器,再经APB2预分频器后得到。将AHB预分频系数和APB2的预分频系数都设置为1,PCLK2即为72MHz。PCLK2为挂载再APB2总线上的外设提供时钟信号,像GPIOx(A~G)、USART1、SPI1、EXTI、AFIO等。

-

TIMxCLK:定时器1和定时器8的内部时钟源,由APB2总线上的时钟PCLK2经过倍频后得到。需要使用定时器1或定时器8,必须先开启APB2总线上对应的定时器时钟。

-

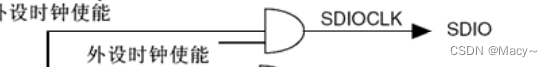

DIOCLK:SDIO外设的时钟,由系统时钟SYSCLK经AHB预分频器后直接得到。需要开启试着用SDIO外设,必须先开启SDIOCLK。

-

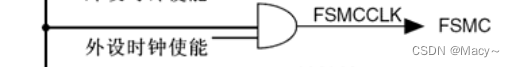

FSMCCLK:可变静态存储控制器的时钟,由系统时钟SYSCLK经AHB预分频器后直接得到。需要使用FSMC外接存储器,必须先开启FSMCCLK。

-

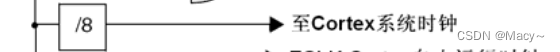

STCLK:系统定时器SYSCLK的外部时钟源,由系统时钟SYSCLK经AHB预分频器,再经过8分频后得到。除了外部时钟源STCLK,系统定时器SYSCLK还可以将FCLK作为内部时钟源。

-

ADCCLK:ADC1、ADC2、和ADC3的时钟,由APB2总线上的时钟PCLK2经过ADC预分频器得到。ADCCLK最大的频率为14MHz。

-

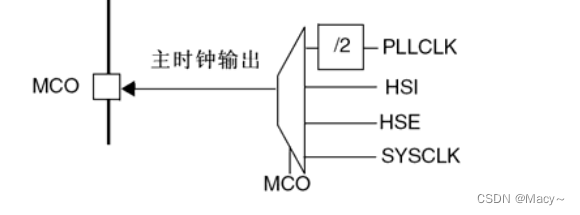

MCO 时钟输出:微控制器允许输出时钟信号到外部MCO引脚,相应的GPIO端口寄存器必须被配置为相应功能。

-

IWDGCLK 看门狗时钟:如果独立看门狗已经由硬件或软件启动,LSI振荡器将被强制再打开状态,并且不能被关闭。在LSI振荡器稳定后,时钟供应给IWDG。

-

CSS 时钟安全系统:时钟安全系统可以通过软件被激活。一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

-

**RTCCLK 实时时钟 **:RTCCLK 时钟源可以由HSE/128、LSE、或LSI时钟提供。

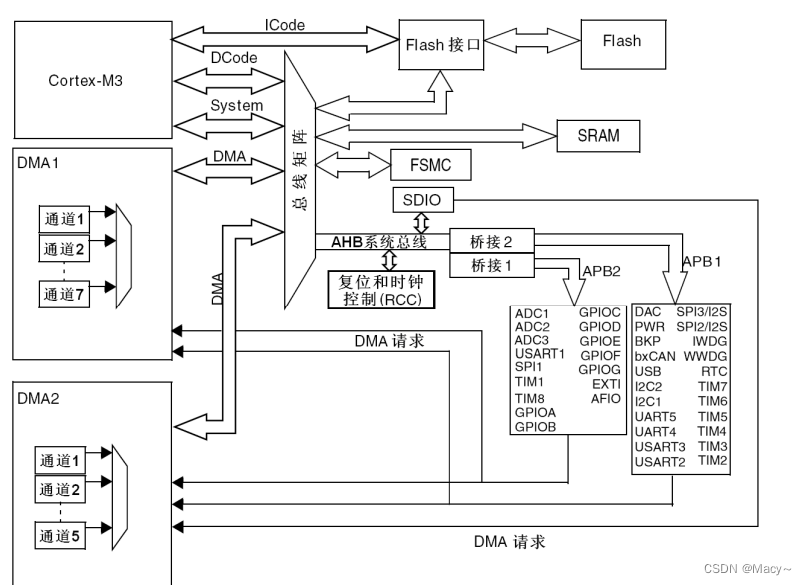

五. 关于总线架构

关于在第四节中涉及到的APB1,APB2,在STM32F10xxx参考手册中的第25页开始就有有关于总线架构的内容介绍。

- ICode总线:该总线将CortexTM-M3内核的指令与闪存(Flash)指令接口相连接。指令预取在此总线上完成。

- DCode总线:该总线将Cortex™-M3内核的DCode总线与闪存存储器的数据接口相连接(常量加载和调试访问)。

- 系统总线:此总线连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。

- DMA总线:此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到SRAM、闪存和外设的访问。

- 总线矩阵:总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。在互联型产品中,总线矩阵包含5个驱动部件(CPU的DCode、系统总线、以太网DMA、DMA1总线和DMA2总线)和3个从部件(闪存存储器接口(FLITF)、SRAM和AHB2APB桥)。在其它产品中总线矩阵包含4个驱动部件(CPU的DCode、系统总线、DMA1总线和DMA2总线)和4个被动部件(闪存存储器接口(FLITF)、SRAM、FSMC和AHB2APB桥)。

- AHB/APB桥(APB):两个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。

1373

1373

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?