-

全相联映射:主存物理地址 =标记+块内地址

-

组相联映射:主存物理地址 =标记+组号+块内地址

-

直接映射: 主存物理地址 =标记+cache+块内地址

主物理地址: 块号+块内地址

二.例题

【例1】有效容量为128KB的Cache,每块16字节,采用8路组相联,字节地址为1234567H的单元调入该Cache,则其Tag(标签)应为______

128KB的Cache,每块16B(默认字节编制,1B对应1个地址,可表示16个地址)

那么总共有128KB/16B=2^13块,采用8路组相联,于是可划分为 2^13/8=2^10组,需要10位来寻址;每块16B(24),字块内地址为4位。

再根据字节地址1234567H,16进制数用4个2进制表示,所以一共是28个二进制数(主存物理地址),对应二进制为 0001 0010 0011 0100 0101 0110 0111

除去低位的Cache字块组号和字块内地址,可知高14位为主存字块标记 0001 0010 0011 01,对应十 六进制为 048DH

组相联映射:主存物理地址(28位) =标记+组号(10组)+块内地址(4)

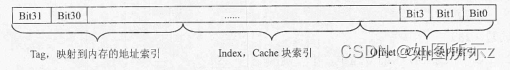

【例2】某32位总线处理器的Cache直接映射方式如下图所示,若Cache大小为16KB,每个Cache块为16字节,则Offset,Index和Tag所占的位数分别是

直接映射的方式为:主存储器中一块只能映像到Cache的一个特定的块中。主存与缓存分成相同大小的数据块。主存空间按缓存容量分成区,每一区的块数与缓存的总块数相等。

offset:块内偏移量,长度由cache块的大小决定

index: 块所在的组号,长度由Cache中组的数量决定;

tag:主存地址剩余部分,长度由主存地址的总长度减去offset与index决定

如果每个Cache块的字节数是16B,则Cache块内索引的位数为4位(2^4=16);如果Cache的大小为16KB,16KB/16B=1024块,所以需要Index索引的位数为10位(2^10=1024),映射到内存的地址位数为32-4-10=18。

这样块内地址占4位,块号10位。主存分区号:18位。

直接映射: 主存物理地址 =标记(TAG)+cache+块内地址

【例2】某32位计算机的Cache容量为16KB,Cache块的大小为16B,若主存与Cache地址映像采用直接映像方式,则主存地址为0x1234E8F8的单元装入Cache的地址是______。

主存地址共32位,主存一个数据块调入Cache时使用直接映像方式,把主存按Cache容量分为若干区,主存某一数据块只能放在与Cache块号相同的数据块中,这样地址转换比较方便。

由于Cache与主存的数据块大小是16B,块内地址需(2^4=16)4位

Cache容量为16KB,故Cache可分为(16KB/16B=1024)1024块,块地址需(2^10 =16)10位,除去这14位低位地址,主存地址高位共18位,即主存分区号,

作为字块标志也需要写入Cache数据块中。因此,装入Cache的地址编号为低14位数据即10100011111000B

文章详细介绍了Cache的三种映射方式——全相联映射、组相联映射和直接映射,以及在不同映射方式下如何计算和确定标记(Tag)、组号、块内地址的位数。通过两个示例具体展示了地址转换的过程,涉及Cache容量、块大小、组数和主存地址结构等概念。

文章详细介绍了Cache的三种映射方式——全相联映射、组相联映射和直接映射,以及在不同映射方式下如何计算和确定标记(Tag)、组号、块内地址的位数。通过两个示例具体展示了地址转换的过程,涉及Cache容量、块大小、组数和主存地址结构等概念。

1004

1004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?