- NSS:从设备使能信号,由主设备控制,低电平有效

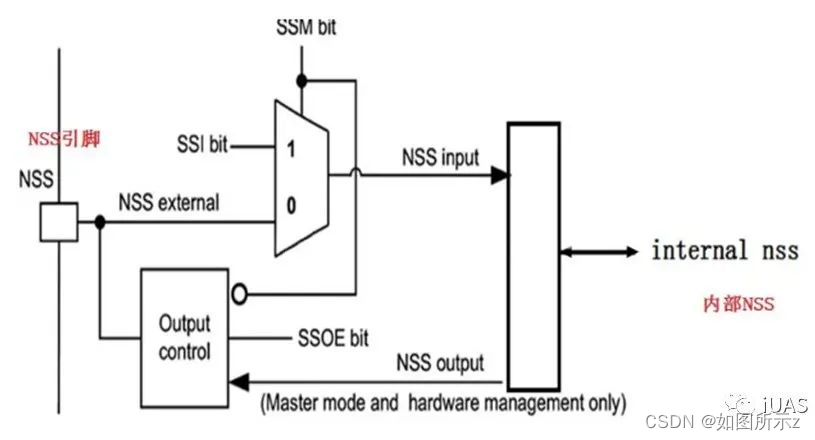

- 区分开内部NSS和NSS外部引脚的区别,内部NSS的电平状态决定了设备的主从模式,内部NSS状态可以由NSS外部引脚控制,也可以由控制寄存器的SSI位控制

STM32上SPI接口的NSS结构图如图所示,除了外部的NSS引脚,还有内部NSS,且内部NSS状态可以由寄存器独立控制,也正因此,NSS引脚既可作输入也可作输出。

主模式和从模式下均可以由软件或硬件进行NSS管理;将SPI_CR1寄存器的SSM位置为1时,NSS引脚将被释放出来用作GPIO口;

6669

6669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?