数模转换器(DAC)基础理论

文章目录

前言

提示:这里可以添加本文要记录的大概内容:

数模转换器(DAC):顾名思义,数字信号转换为模拟信号。本文将介绍数模转换器的相关基础知识,包括DAC的基本结构、性能参数和DAC的分类三部分。

一、DAC基本工作原理

DAC转换器基本结构如下所示,通过二进制开关、加权网络和基准电压即可实现数字信号到模拟信号的转换。且

实际应用的D/A转换器,其码字受到同步时钟控制,因此必须使用锁存器来保存转换器的码字,且其输出还需要一个采样保持电路。

二、 DAC的性能参数

2.1 静态性能参数

2.1.1 精度

代表模拟输出实际与理论值偏差的参数

表示方法:①用满量程范围的百分数表示(%FSR);②用最低位输出的模拟量为单位表示。

2.1.2 分辨率

分辨率表征模拟输出量分辨程度的参数,分为数字分辨率、模拟分辨率和相对分辨率三种表示方式。

| 类型 | 定义 |

|---|---|

| 数字分辨率 | 采用位数N代表数字分辨率 |

| 模拟分辨率 | DA能分辨的最小模拟量输出 |

| 相对分辨率 | 模拟分辨率与额定满度输出量程FSR之间的比值 |

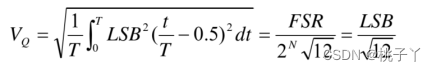

2.1.3 量化噪声

量化噪声代表实际输出值和理想输出值之间的差值,计算公式如下所示

2.1.4 失调误差 和增益误差

| 性能参数 | 定义 |

|---|---|

| 失调误差 | 又称偏移误差或者零点误差,即数字输入为0时,模拟输出和0之间的差值。 |

| 增益误差 | 实际转换斜率和理想转换斜率之间的误差,又称为比例因子误差。 |

失调误差和增益误差用输入输出图表表示更加直观,如下图所示。

2.1.5 积分非线性和微分非线性

这两个参数是用于表征DA转换器直流传输特性的非线性行为

| 性能参数 | 定义 |

|---|---|

| 积分非线性(INL) | 实际的有限精度特性和理想有限精度特性之间在垂直方向的最大差值。 |

| 微分非线性 (DNL) | 相邻两个输出值在垂直跨度之间的最大差值,可表示为一正DNL和一个负DNL。 |

如下图所示

2.动态性能参数

2.2.1 建立时间

数据手册中的建立时间一般是指从全“0”到全“1”变化的时间。低速转换器(满量程建立时间>100us),中速转换器(>1us,<100us),高速转换器(50ns~1us),超高速转换器(<50ns)。

2.2.2 毛刺(glitch)

D/A转换器输出模拟曲线中出现的尖峰成为毛刺(glitch)

毛刺一般有两种原因:①开关电路不匹配导致开关开启或关闭不同步而引发暂态乱码;②开关快速切换,开关控制信号端到模拟输出端寄生电容引发的时钟馈通效应产生

2.2.3 信噪比和信噪比失调

信噪比(简称SNR)是指信号功率和噪声功率的比值,计算公式如下所示。

信噪失调比:是指信号功率与噪声功率及其谐波功率的比值,计算公式如下所示。

2.2.4 无杂波动态范围

SFDR是指在感兴趣的输出频带范围内基波功率和最大谐波功率的比值。

2.2.5 谐波失真和总谐波失真

谐波失真(HDi)是指第i次谐波功率与基波功率的比值,计算公式如下所示。

总谐波失真(THD)是指在特定频率范围内总谐波功率与基波功率的比值。

三、DA转换器的分类

3.1 按加权网络实现形式分类

根据DAC的加权网路的实现方式可以分为3大类,且三大类的实现形式不同。

| 类别 | 实现方式 |

|---|---|

| 电流型DAC | 实现方式分为二进制电阻网络DAC和R-2R电阻网络DAC |

| 电压型DAC | 由电阻分压实现 |

| 电荷型DAC | 使用电容和运放实现电荷再分布 |

比如MAX5382是一款8位的DAC,该DAC的内部结构如下所示,其内部的加权网络是电流型DAC。

3.2 按照转换速率分类

按照转换速率可以分为以下4类别

| 类别 | DA转换速度 |

|---|---|

| 低速DAC | 建立时间>100us |

| 中速DAC | 建立时间:1us~100us |

| 高速DAC | 建立时间:50ns~1us |

| 超高速DAC | 建立时间:<50ns |

3.3 其他分类方式

| 分类方式 | 类别 |

|---|---|

| 按分辨率分 | 分为6位、8位、10位、12位、14位和24位等 |

| 采样速率分 | 奈奎斯特D/A转换器和过采样D/A转换器 |

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?