实验四 74LS160组成n进制计数器

一、实验内容

1.掌握集成计数器的功能测试及应用

2.用异步清零端设计6进制计数器,显示选用数码管完成。

3.用同步置零设计7进制计数器,显示选用数码管完成。

二、演示电路

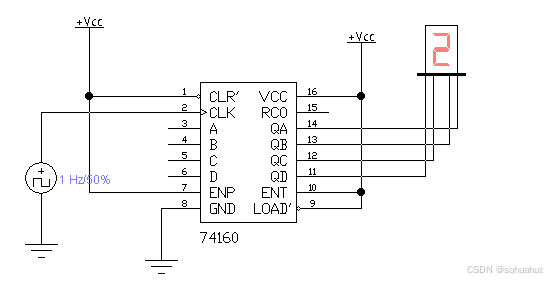

74LS160十进制计数器连线图如图1所示。

图1 74LS160十进制计数器连线图

CLR:异步清零端

CLK:时钟输入端(上升沿有效)

- D:数据输入端

ENP,ENT:计数控制端

LOAD:同步并行置入控制端

RCO:进位输出端

74160的功能表如表1所示。由表1可知,74160具有以下功能:

① 异步清零

当![]() (CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP ),计数器输出将被直接置零,称为异步清零。

(CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP ),计数器输出将被直接置零,称为异步清零。

② 同步并行预置数

在![]() =1的条件下,当

=1的条件下,当![]() (LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3 输入端的数据将分别被Q0~Q3所接收。由于这个置数操作要与CP 上升沿同步,且D0、D1、D2、D3的数据同时置入计数器,所以称为同步并行置数。

(LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3 输入端的数据将分别被Q0~Q3所接收。由于这个置数操作要与CP 上升沿同步,且D0、D1、D2、D3的数据同时置入计数器,所以称为同步并行置数。

③ 保持

在![]() =1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

=1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

④ 计数

当![]() ==ENP=ENT=1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,RCO端从高电平跳变至低电平。可以利用RCO端输出的高电平或下降沿作为进位输出信号。

==ENP=ENT=1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,RCO端从高电平跳变至低电平。可以利用RCO端输出的高电平或下降沿作为进位输出信号。

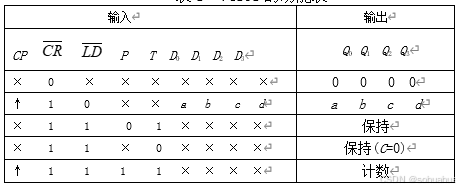

表1 74161的功能表

连上十进制加法计数器160,电路如图1所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

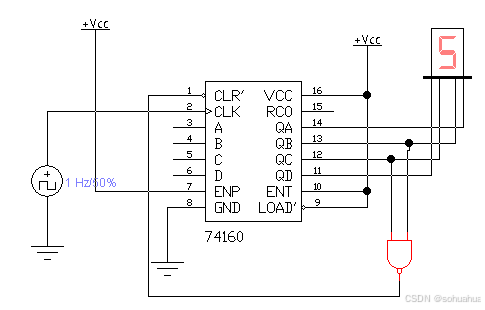

三、用160和与非门组成6进制加法计数器-用异步清零端设计

74160从0000状态开始计数,当输入第6个CP 脉冲(上升沿)时,输出Q3 Q2 Q1 Q0=0110,此时![]() =0,反馈给

=0,反馈给![]() 端一个清零信号,立即使Q3 Q2 Q1 Q0返回0000状态,接着,

端一个清零信号,立即使Q3 Q2 Q1 Q0返回0000状态,接着,![]()

端的清零信号也随之消失,74160重新从0000状态开始新的计数周期。

反馈归零逻辑为代码中为1的Q相与非。![]()

电路如图2所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

图2 用异步清零端设计

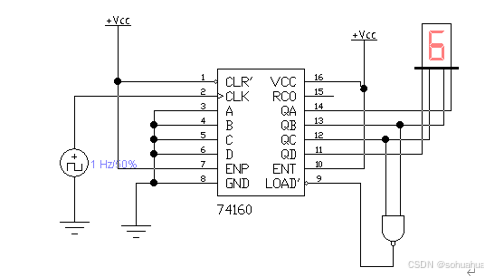

四、用160和与非门组成7进制加法计数器-用同步置零设计

计数器从Q3Q2Q1Q0=0000开始计数,当第6个CP到达后,计到0110,此时

![]() =0。并不能立即清零,而是要等第7个脉冲上沿到来后,计数器被置成0000。不会用异步清零端那样出现0110过渡状态,这是与用异步清零端的差别。用同步清零端设计计数器如图3所示,如

=0。并不能立即清零,而是要等第7个脉冲上沿到来后,计数器被置成0000。不会用异步清零端那样出现0110过渡状态,这是与用异步清零端的差别。用同步清零端设计计数器如图3所示,如![]() ,则为七进制计数器。

,则为七进制计数器。

图3 同步清零端设计计数器

五、实验报告

1. 实验名称、内容和实验电路。

2. 说明同步置零与异步清零的区别?

答:同步,异步是对于时钟而言的。

同步指的是,状态的变化需要等待时钟有效沿来触发,所有动作同时跟随这个时钟变化,而异步时,状态变化不依赖与时钟。

异步清零说的是,你需要对一个计数器在满足某种条件时想要他归零,但又不需要等下一个时钟过来,是一个条件满足就立即执行的过程;

同步置数,比如你想让计数器采用置数法实现任一模计数,你要设置一个条件,计数记到1001时实现置数,但是,当计数器记到1001的时候,不能立马置数,要等下一个时钟有效沿来,你的条件才能生效,才能完成置数!

异步清零,当输出的状态是1001时,不等下一个有效时钟到来,这一瞬间立马计数器被清零,表现在状态图里面就是,1001这个状态是一个过渡状态,他的出现只是短暂一瞬!

3.总结使用集成计数器的体会

所谓集成计数器,就是将整个计数器的电路集成在一个芯片上,为了增强集成计数器的适应能力,一般集成计数器设有更多的附加功能,如预置数、清除、保持、计数等多种功能。因此,它具有通用性强、便于功能扩展、使用方便等优点,应用十分普遍。

当今集成计数器的品种有很多,按其功能可分为:同步和异步两类。

2140

2140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?