一、实验目的

1. 掌握组合逻辑电路的功能测试。

2. 验证半加器和全加器的逻辑功能。

3. 学会二进制数的运算规律。

二、实验准备

芯片:74LS00、74LS86

三、实验原理

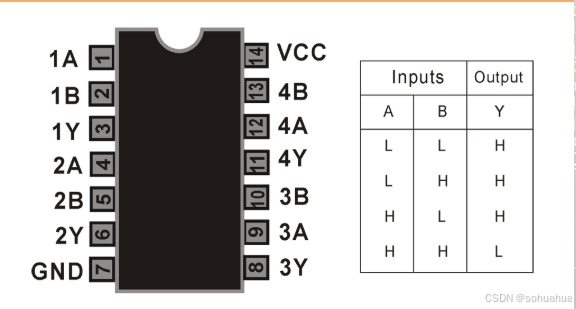

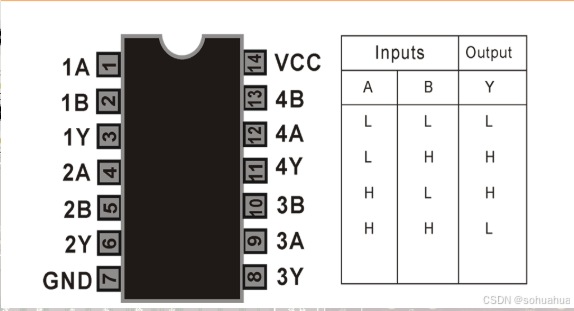

芯片引脚图及真值表:

74LS00 二输入端四与非门

74LS86 二输入端四异或门

四、实验内容及步骤

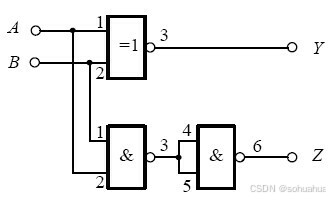

1. 组合逻辑电路功能测试

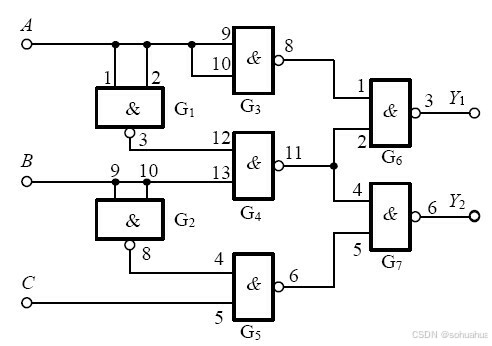

(1)用2片74LS00组成图3.1所示逻辑电路。为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

图3.1

图3.1(b)

(2)先按图3.1写出Y2的逻辑表达式并化简。

表3.1

| 输入 | 输出 | |||

| A | B | C | Y1 | Y2 |

| 0 0 0 1 1 1 1 0 | 0 0 1 1 1 0 0 1 | 0 1 1 1 0 0 1 0 | 0 0 1 1 1 1 1 1 | 0 1 1 0 0 0 1 1 |

(3)图中A、B、C接逻辑开关,Y1,Y2接二极管电平显示。

(4)按表3.1要求,改变A、B、C输入的状态,填表写出Y1,Y2的输出状态。

(5)将运算结果与实验结果进行比较。

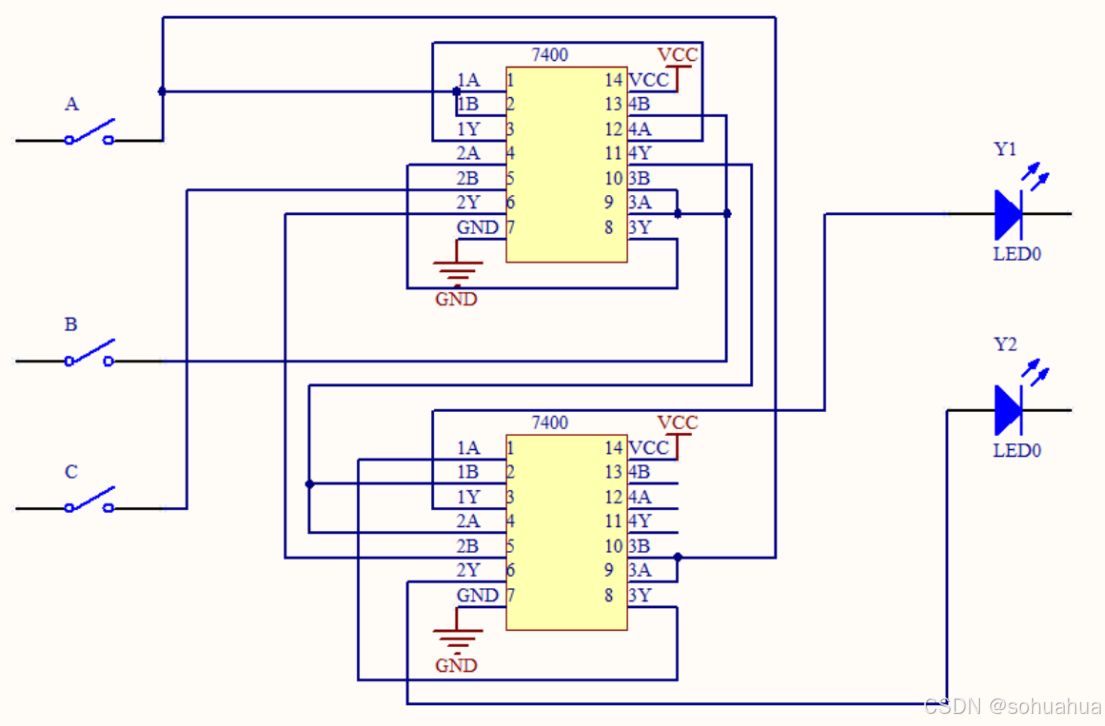

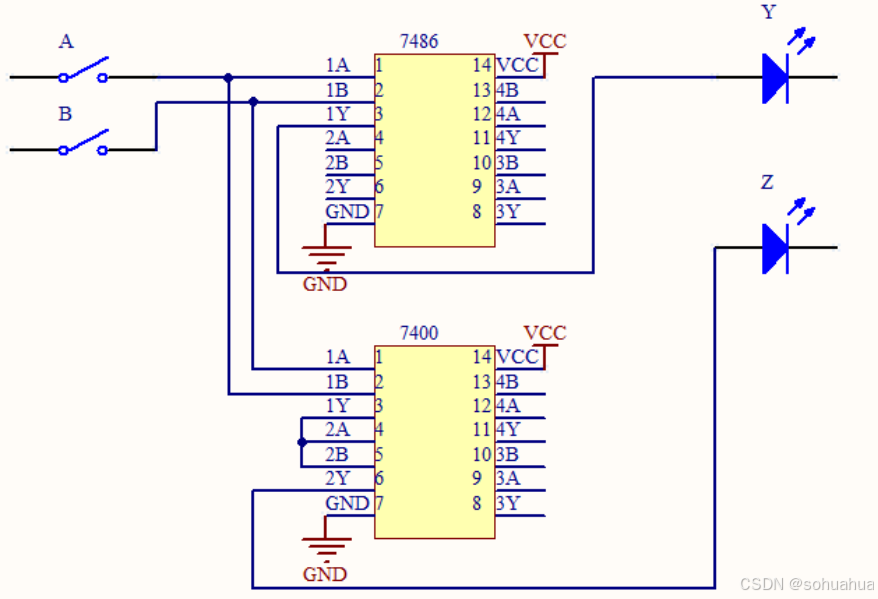

2.用异或门(74LS86)和与非门组成的半加器电路

根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,即半加器可用一个异或门和二个与非门组成一个电路。如图3.2。

图3.2

图3.2(b)

(1)在数字电路实验平台上插入异或门和与非门芯片。输入端A、B接逻辑开关k,Y,Z接发光管电平显示。

(2)按表3.2要求改变A、B状态,填表并写出y、z逻辑表达式。

表3.2

| 输入端 | A | 0 | 1 | 0 | 1 |

| B | 0 | 0 | 1 | 1 | |

| 输出端 | Y | 0 | 1 | 1 | 0 |

| Z | 0 | 0 | 0 | 1 |

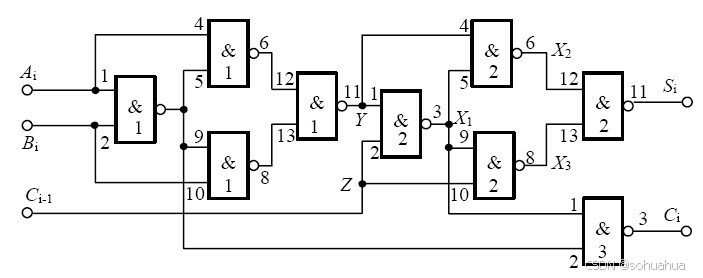

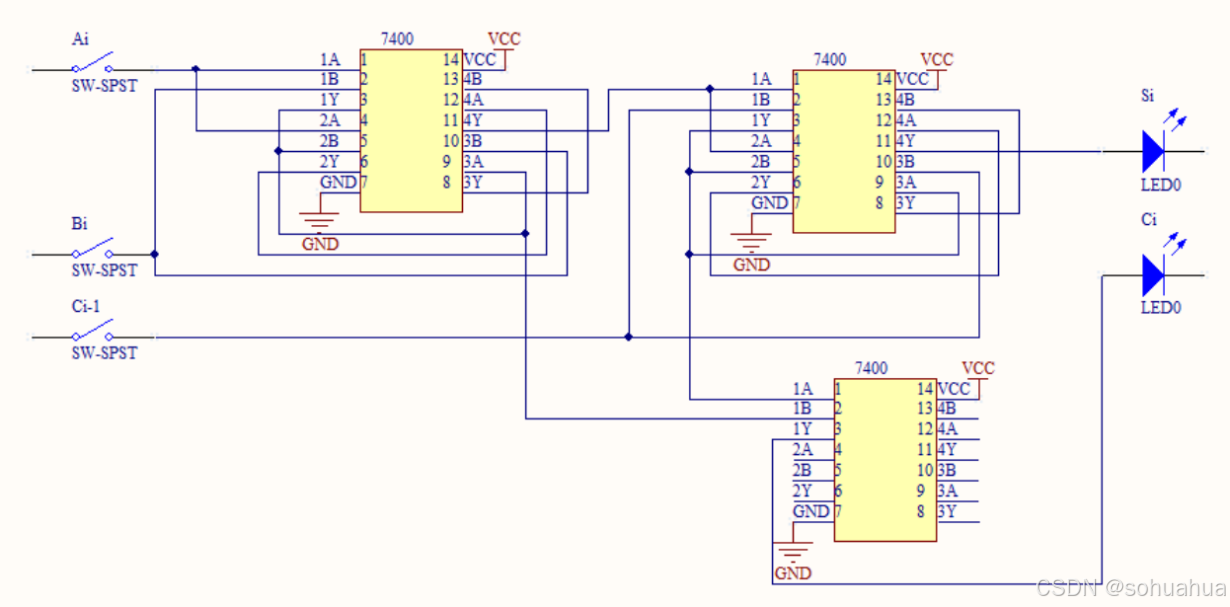

3.全加器组合电路的逻辑功能测试

(1)写出图3.3电路的Y、Z、X1.X2.X3的逻辑表达式。

(2)根据逻辑表达式列真值表。

(3)根据真值表画出逻辑函数Si、Ci的卡诺图。

图3.3

图3.3(b)

Si的卡诺图

| Bi、 Ci-1 Ai | 0 0 | 0 1 | 1 1 | 1 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

Ci的卡诺图

| Bi、 Ci-1 Ai | 0 0 | 0 1 | 1 1 | 1 0 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 |

(4)填写表3.3各点状态

表3.3

| A1 | B1 | C1-1 | Y | Z | X1 | X2 | X3 | S1 | C1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

(5)按原理图选择与非门并接线进行测试,并与上表进行比较看逻辑功能是否一致。

五、实验报告

1. 整理实验数据、图表并对实验结果进行分析讨论。

答:与非门是与门和非门的结合,先进行与运算,再进行非运算。与非门是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。

2. 总结全加器卡诺图的分析方法。

答:全加器的设计中,主要过程包括:首先由逻辑要求列出真值表,其次根据真值表写出逻辑函数,最后将逻辑函数化简,并根据化简结果画出逻辑电路图。该过程步步渐进,直接明了,其中主要难点在于写出逻辑函数后所进行的逻辑函数化简,这也是数字电路设计过程的基础。

3.总结实验中出现的问题和解决的办法。

答:

(1)实验中遇到的问题及解决办法。

对实验流程不够清晰,通过多加练习得到解决;

(2)实验的心得体会。

a.掌握了组合逻辑电路功能调试的基本方法。

b.验证了半加器和全加器的逻辑功能。

c.复习二进制数的运算规律。

4785

4785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?