嵌入式系统设计——复习概要(二)

硬件基础

一.基于arm技术的嵌入式系统硬件架构

1.1ARM公司特点

公司的业务是一个纯粹的知识产权的贩卖者,没有硬件,没有软件,只有图纸上的知识产权。

1.1ARM微处理器特点和技术指标:

特点

1.大量使用寄存器,RISC结构

2.功能强大的存储区保护功能

3.可扩展处理器结构

4.肖特基、低功耗、成本,高性能

技术指标

功能,字宽,处理速度、功耗、寻址能力、工作温度、工艺

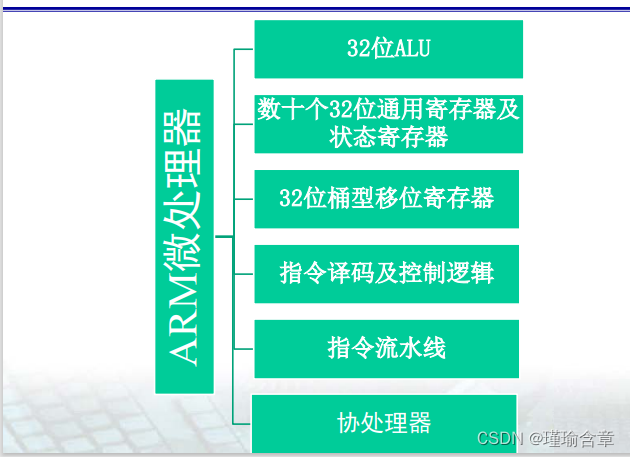

1.2基于ARM技术的嵌入式系统硬件架构

1.2.1 ALU

与常用的ALU逻辑结构基本相同,是由2个操作数锁存器、加法器、逻辑功能、结果及零检测逻辑构成

1.2.2 高速乘法器

采用两位乘法并带有加1移位的方法来实现乘法。内部高速乘法器采用32位的结构,这样可以降低集成度。

1.2.3 桶形移位寄存器

ARM采用32位的桶形移位寄存器,置于ALU的操作输入口前。这样使逻辑移位和算术移位等都可以在一个周期内完成。

1.2.4 协处理器

被附接在CPU上,并能实现部分指令

步骤

1.CPU收到协处理器操作指令时,CPU要激活该协处理器并将有关指令传给它。

2.协处理器的指令能够装入和存储在协处理器的寄存器中或者

执行内部操作。

3.CPU可以暂停执行以等待协处理器指令的结束

1.3 体系结构原理

冯·诺依曼结构

存储空间存储了全部的数据和程序指令,它们内部使用单一的地址总线和数据总线

哈佛结构

存储器分为数据和程序二个存储空间,有各自独立程序总线和数据总线,可以进行独立编址和独立访问。

特点:

数据和程序可以并行完成,这使得数据移动更加容易。数据的吞吐量比上以中提高了大约一倍。但这种结构的弱点是很难在哈佛机上编写出一个自修改的程序(即写入数据值后,使用这些值作为指令的程序)。

1.4 先进技术

1.4.1 流水线技术

3级流水:取值、译码,执行

5级流水:取值,译码,执行,缓冲数据,回写

数据相关冲突:分离式指令Cache和数据Cache

控制相关冲突:指令预测

1.4.2 超标量执行

通过重复设置多套指令执行部件,同时处理并完成多条指令,实现并行操作,来达到提高处理速度的目的。

超标量执行:超标量CPU利于采用多条流水线结构

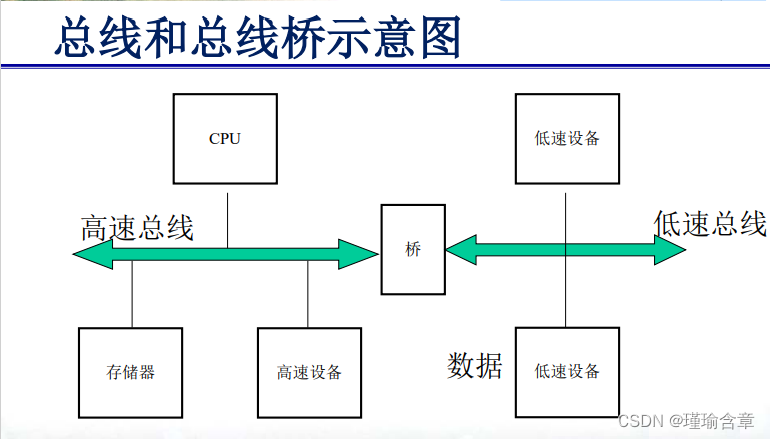

1.4.3 总线和总线桥

总线分类:片内总线/片外总线;数据总线,地址总线,控制总线。

总线参数:(总线宽度(位)/8)*总线频率 (HZ)=总线带宽(B/s)

高性能总线AHB(主单元,从单元,仲裁器,译码器):

两个阶段:地址传送、数据传送

桥:联接AHB和APB

外围设备总线APB。

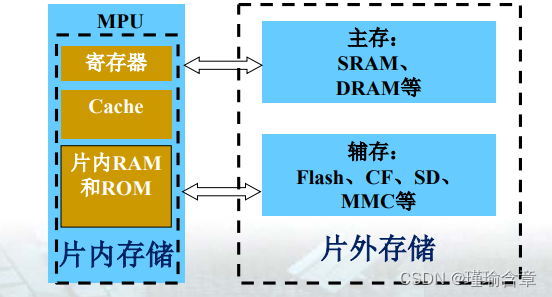

1.5 嵌入式系统存储器系统组成

1.5.1 寄存器

暂存指令,数据,位址

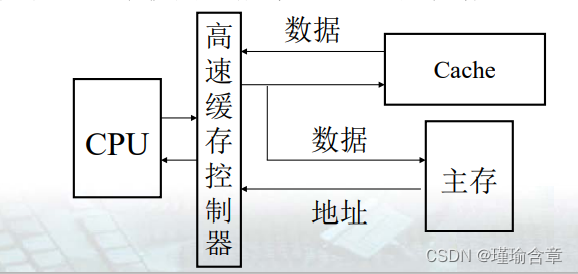

1.5.2 Cache

透明性

全相联映像:灵活、高成本

直接映像:简单,但是不灵活,命中率低

组相联映像:其组间是直接映像方式;组内的页执行的是全相连映像方式

替换算法:解决不命中

FIFO:简单,开销小

LRU:命中率高,局部性原理体现

Cache和主存的写策略:

写直达法(Write-through):

当要写Cache时,数据同时写回主存储器。

写回法(Write-back):

当处理器更新Cache的某一行后,相应数据并不立刻写回主存储单元,而当该行被从Cache淘汰时,才把数据写回主存储器中。

写一次法:

写命中与未命中的处理方法与写回法基本相同,只是第

一次写命中是要同时写入主存。

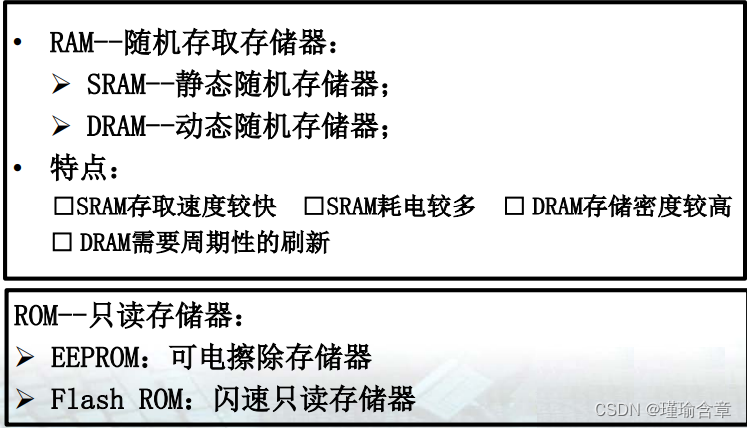

1.5.3外部存储

523

523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?