1.模块语句及表达方式

module 模块名(模块端口名表);

模块端口和功能描述

endmodule任何可综合的最基本模块都必须以关键词module开头;endmodule 是模块结束语句,旁边不加任何标点符号。

2.端口语句,端口信号,端口模式

Verilog的端口模式有如下三种,用于定义端口上数据的流动方向和方式。

(1)input:输入端口

定义的通道为单向只读模式,即规定数据只能通过此端口被读入模块实体中。

(2)output:输出端口

定义的通道为单向输出模式,即规定数据只通过此端口从模块实体向外流出,或者说可以将模块中的数据向此端口赋值。

(3)inout:双向端口

定义的通道确定为输入输出双向端口,即从端口的内部看,可以对此端口进行赋值,或通过此端口读入外部的数据信息;而从端口的外部看,信号可由此端口流出,也可向此端口输入信号,如RAM的数据口、单片机的I\O口等。

input 端口名1,端口名2...;

output 端口名1,端口名2...;

inout 端口名1,端口名2...;

input [msb:lsb] 端口名1,端口名2...;

//msb和lsb分别表示信号矢量的最高位和最低位

例如

output [3:0] C,D;

//表示定义了4个四位位宽的矢量或总线端口信号C[3:0],D[3:0]

3.Verilog的四种逻辑状态

- 0.含义有四个,即二进制数0,低电平,逻辑0,事件为伪的判断结果

- 1.含义有四个,即二进制数1,高电平,逻辑1,事件为真的判断结果

- z或Z。表示高阻态或者高阻值

- x或X。表示不确定或者未知的逻辑状态

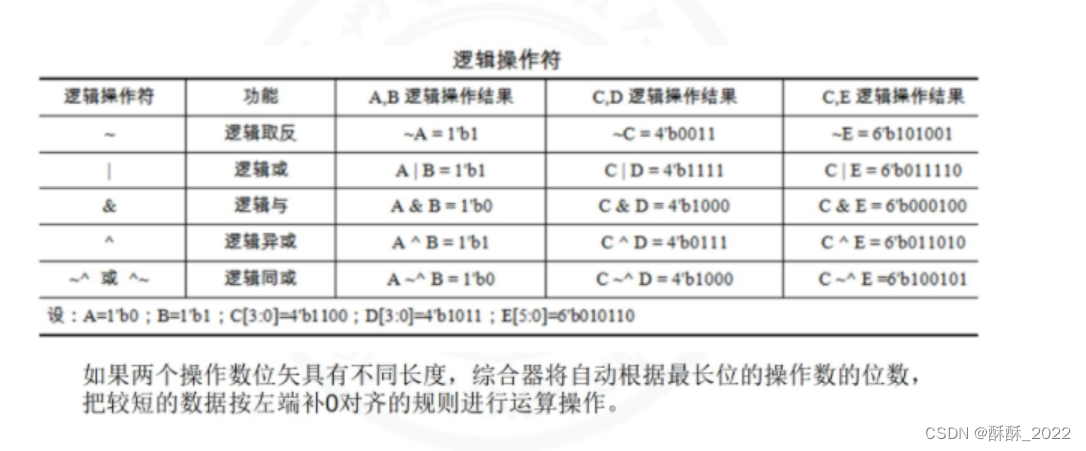

4.按位逻辑操作符

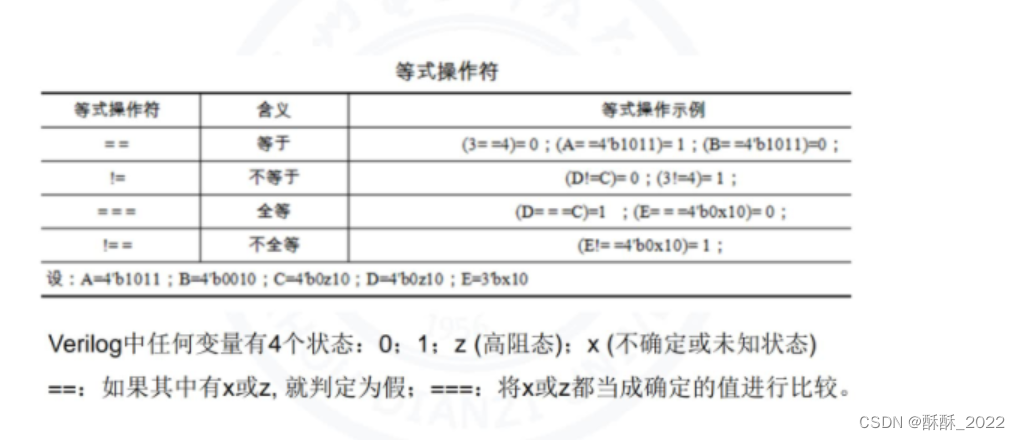

5.等式操作符

==:位数相等,逐位比较,位数不等,高位补0进行比较,这时当每一位都相等时,输出位1,否 则为0;此外,如果含未知值x和高阻态z,则都为假

===:把x和z都当成确定的值进行比较,当表述完全相同输出1,不同输出0.且对于位数不等的数 不会像==那样高位补0,而会直接判断两数据不等。

6.并位操作运算符

并位操作运算符用{ }表示,可以将两个或多个信号按照二进制位拼接起来,作为一个数据信号使用。如{s1,s2},s1,s2取0或1,合并后新信号的取值范围是两位二进制数:00,01,10,11.

同时也可以嵌套使用,简化某些重复的表述,例如

{a1,b1,4{a2,b2}}={a1.b1,{a2,b2},{a2,b2},{a2,b2},{a2,b2}}={a1,b1,a2,b2,a2,b2,a2,b2,a2,b2}7.Verilog的数字表达形式

Verilog中表示一个二进制数格式一般如下

<位宽>'<进制><数字>

B:二进制; O:八进制 ; D:十进制; H:十六进制

2'B10表示两位二进制数10;

4'B1011表示四位二进制数1011;

4'hA表示一位十六进制数A或者四位二进制数1010

3'D7表示3位二进制数111

再如:

S[3:0]=1的等号右侧1应该为0001,正式写法为4'B0001

S[5:0]=7中的7应该等于6'B000111

5'Bz=5B'zzzzz

verilog还可以定义有符号二进制数,如,8’b10000100和8'sb是不一样的,前者是无符号数,后者是有符号数,其最高位1是符号位 .sb是限定有符号二进制数的进制限定关键词。

2095

2095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?