《EDA技术实用教程(第六版)》学习笔记——第三章

第三章目录

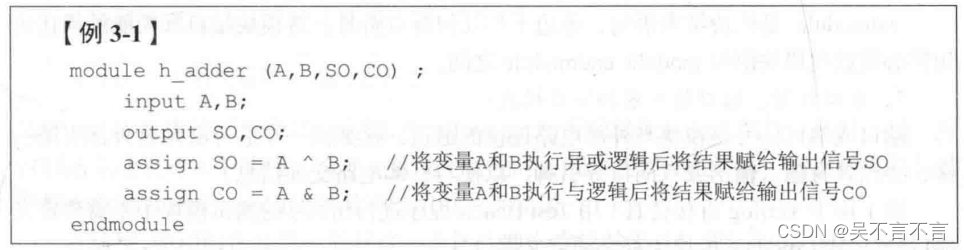

1、半加器的Verilog的描述

- 半加器的逻辑表述、半加器的电路结构、真值表、时序波形:

- 半加器的Verilog描述:

- h_adder是模块名,是设计者为其设计的模块所取的名字。

- h_adder旁的括号及其内容称为“端口表”,括号中的内容就是此模块的所有端口信号名。

- assign引导的赋值负责描述模块内部的逻辑功能和电路结构。

- assign引导的赋值语句属于并行赋值语句,无论有多少行语句,都是同时执行的,与语句的前后次序无关。

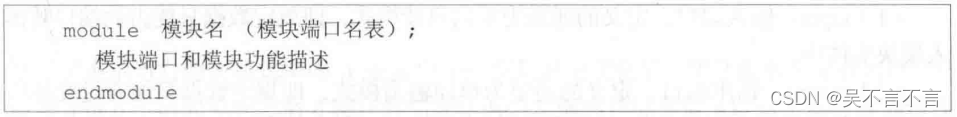

1、1模块语句及其表达方式

- 任一可综合的最基本的模块都必须以关键词module开头。

- 模块名最好根据相应电路的功能来确定。如4位二进制计数器用counter4b。

- 模块端口列表中须列出此模块的所有输入、输出或双向端口名,端口名间用逗号分开,括号外加 分号。

- endmodule是模块结束语句关键词,旁边不加任何标点符号。对模块端口及其功能的描述语句都

必须放在模块语句module_endmodule之间。

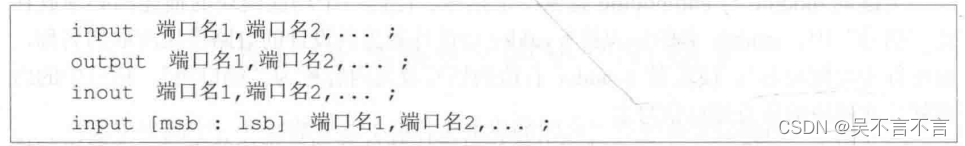

1、2端口语句、端口信号名和端口模式

- 输入端口:input

- 输出端口:output

- 双向端口:inout 使用比较复杂,后续有专门章节讲述,在未理解前,不要轻易使用

- 最后一种端口描述方法是端口信号的逻辑矢量位表达方式,其中的msb和lsb分别是信号量的最高和最低位数。output [3:0] C,D; // C、D均为4位输出端口。

1、3逻辑操作符

Verilog的逻辑操作符大部分与C语言一致,比如:

- 逻辑按位与: &

- 逻辑按位或: |

- 逻辑按位异或:^

- 逻辑按位取非:~

但Verilog也有自己的扩展,比如

- 逻辑按位 与非 ~&

- 逻辑按位 或非 ~|

- 逻辑按位 同或 ~^

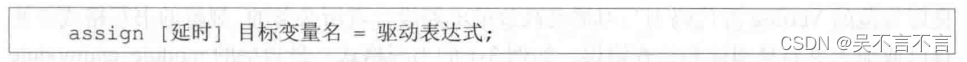

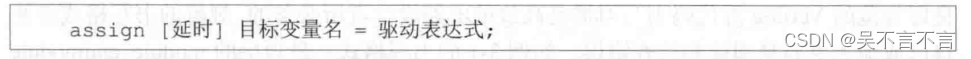

1、4连续赋值语句

- 当等式右端的驱动表达式(赋值源)中任一信号发生变化时,此表达式即被重新计算一遍。

- assign语句是Verilog的并行语句,模块中所有的assign语句同时执行,语句的前后顺序无关;

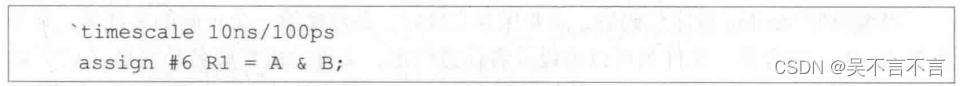

- -加入[延时],表示经过指定延时后再赋值,

- 但这个延时值在综合器中是被忽略的,不参与综合。

- 只对仿真器有效

- 此句表示,仿真的基本时间单元是 10ns,仿真时间的精度是 100ps。在这个时间划分单元下,语句assign #6 R1=A&B”在执行后,一旦计算出A&B的值还要再等待6个时间单元也就是60ns后才将此值赋给 R1。

1、5关键字

- 指verilog语言中预定义的有特殊含义的英文词语。input、output、module、assign、endmodule

关键词必须小写。

1、6标识符

- 设计者在verilog程序中自定义的,用于标识不同名称的词语。例如模块名、信号名、端口名等。Verilog中标识符区分大小写。

1、7书写规范

- Verilog标识符,以英文字符(大小写均可)、数字、下划线“_”组合而成但只能用英文字符或者下划线开头(下划线开头需要慎用,一般为软件自带库来使用),标识符用数字开头是不允许的。

- 最顶层的module_endmodule模块描述语句放在最左侧,比它低一层次的描述语句则向右靠一个Tab键距离。同一语句的关键词要对齐。

1、8Verilog模块文件取名和存盘

- 文件后缀名必须是“.v”。

- 文件取名的大小写也是敏感的。文件名与存储路径不能带有中文字符。

- 对于Quartus,程序名必须和该程序的模块名一致。

1、9注释符号

- //后的注释文字只能放在同一行

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3361

3361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?