在通信中,PLL应用于同步和解调电路。例如,在FM解调和频移键控中,他们是常用的。除此之外,当想要输入的比特流中恢复时钟时,使用锁相环是很有可能的。此外,在通信系统中,为了抖动和降噪,通常使用锁相环。

PLL的常见应用之一是频率合成器以及音调形成。因此使用锁相环可以生成输入频率的倍数的输出频率。而在微处理器中,它们被用于产生稳定的系统时钟。

是控制系统或者控制回路,在输入和输出信号之间保持相同的相位。

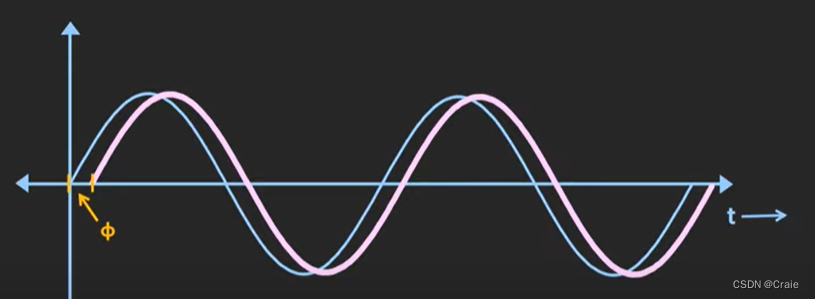

首先了解,什么是相位差?

如下图所示,两个信号具有相同的频率,但两个信号之间存在恒定的相位差

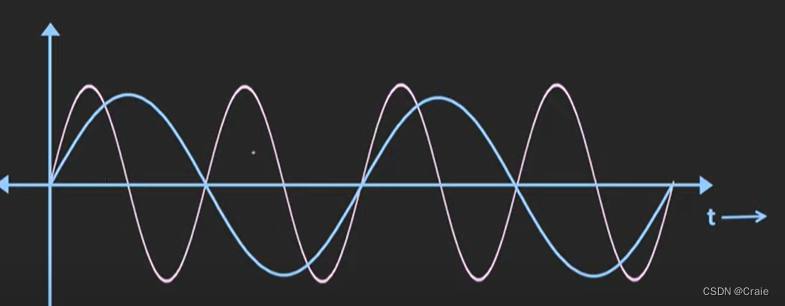

在下图中,两个信号之间的相位随时间不断变化。

因此锁相环系统使输出信号与输入信号在相位和频率上同步:

fo=fin 相位差=constant 环路处于锁定状态

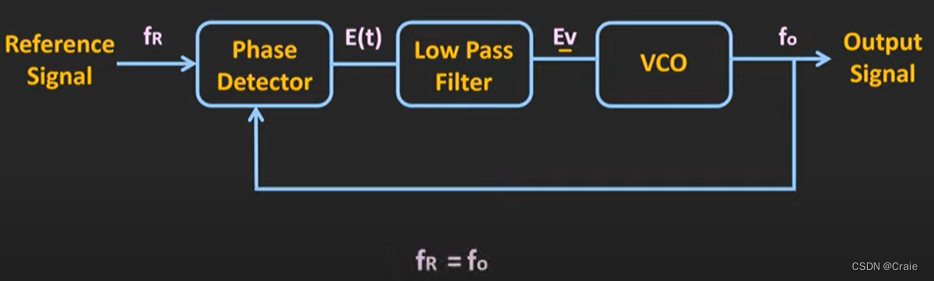

因此锁相环由三个基本模块组成:

当环路刚刚打开,VCO就会以中心频率运行,这个频率被称为自由运行频率。

现在相位检测器将输入或参考信号与振荡器频率进行比较,并在此基础上生成误差信号。这个误差信号通过低通滤波器,低通滤波器根据误差信号产生误差电压。根据这个误差电压,VCO要么减少要么增加振荡器频率,直到振荡器频率锁定在输入频率。

在锁定条件下,两个信号之间可能存在无相位差或恒定相位差。

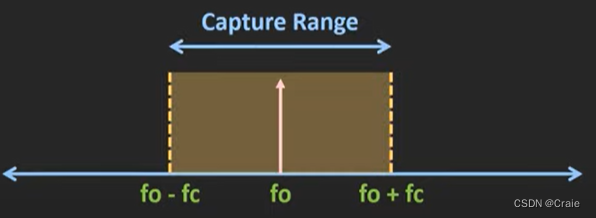

在无锁定条件下,只有当输入信号在PLL的捕获范围时,PLL才能获取锁定。这意味着,只要输入信号在捕获范围内,VCO就可以锁定输入信号。这意味着这捕获范围时VCO中心频率附近的输入频率范围

。只要从解锁条件开始,环路就可以锁定在该范围内。

因此PLL的另一个重要规格就是锁定范围。锁定范围定义了输入频率的范围,在该范围内,一旦捕获了输入信号,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7075

7075

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?