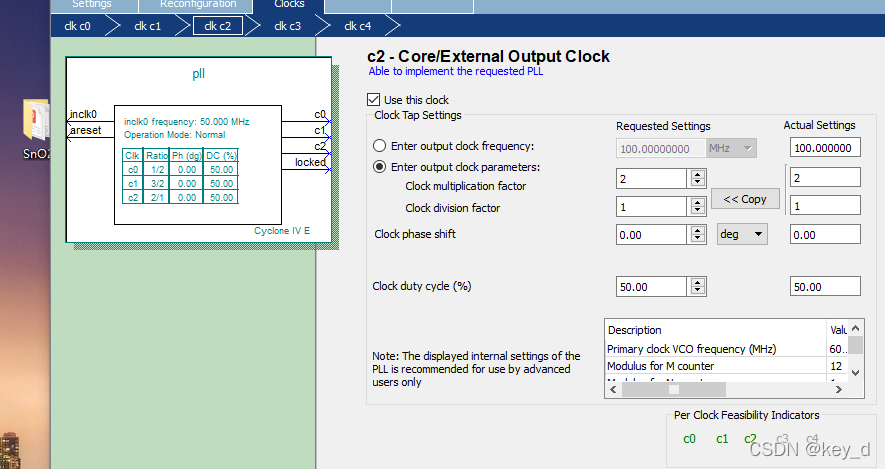

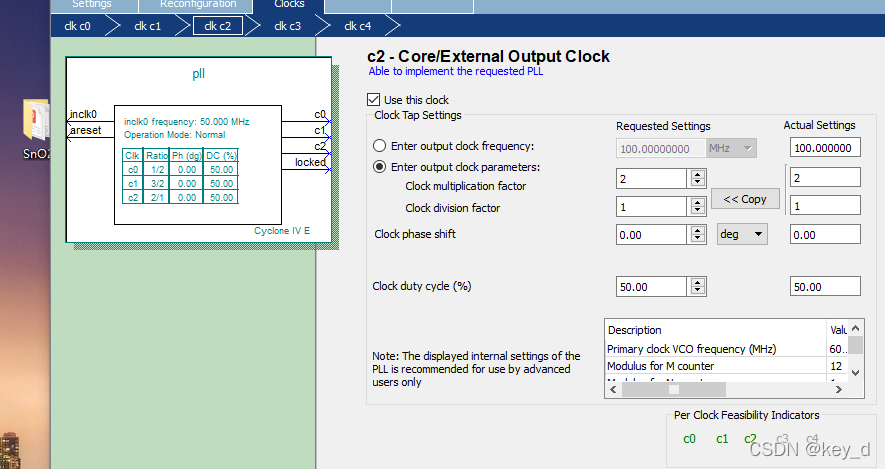

通过频率较低的片外晶振倍频得到频率较高的时钟信号。利用ip核pll产生3个不同频率的时钟(25MHZ,75MHZ,100MHZ)

以及原有系统时钟50MHZ连接到led灯上最后上板观察。

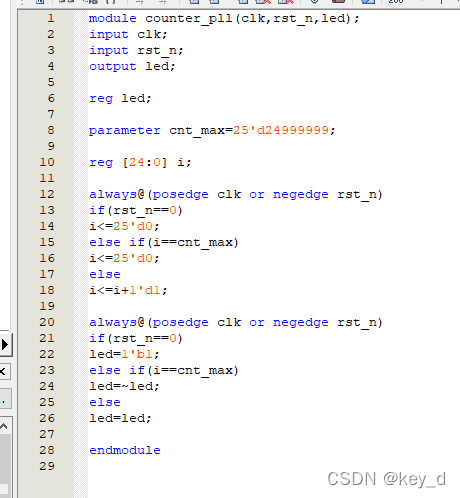

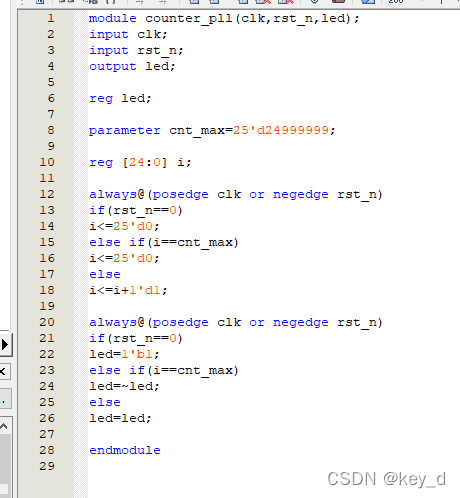

编写一个计数器控制led亮灭的模块

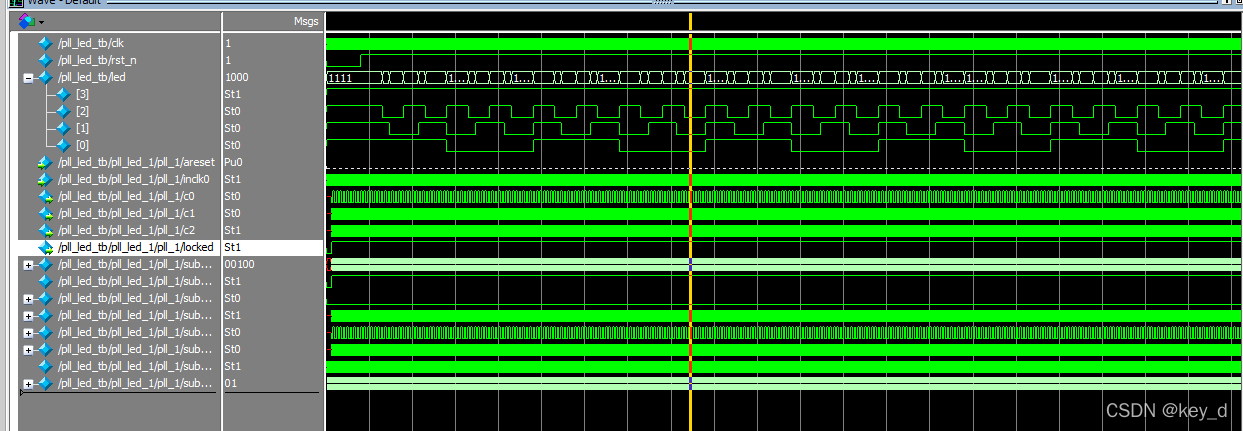

在顶层中将其与pll产生的3个时钟连线,

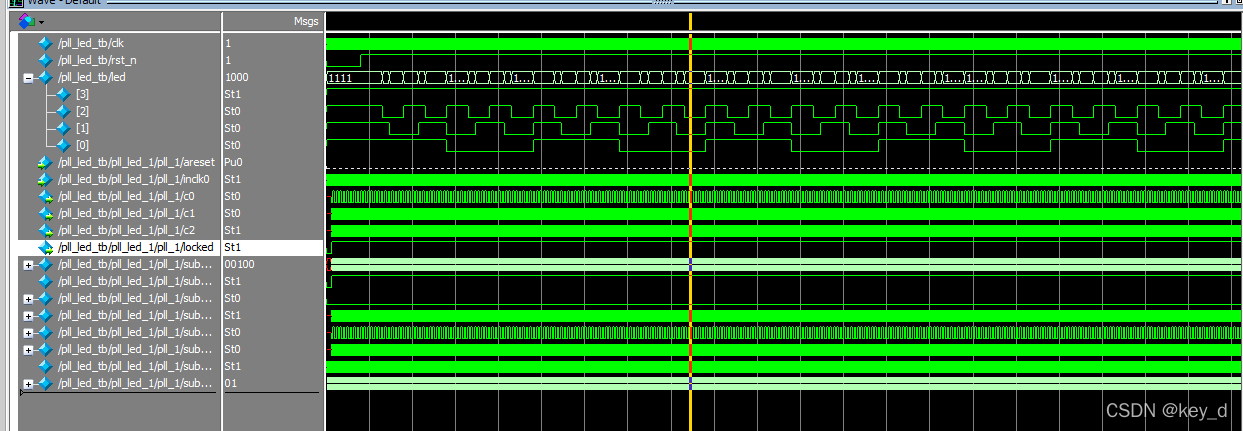

仿真中观察到想要的波形评率

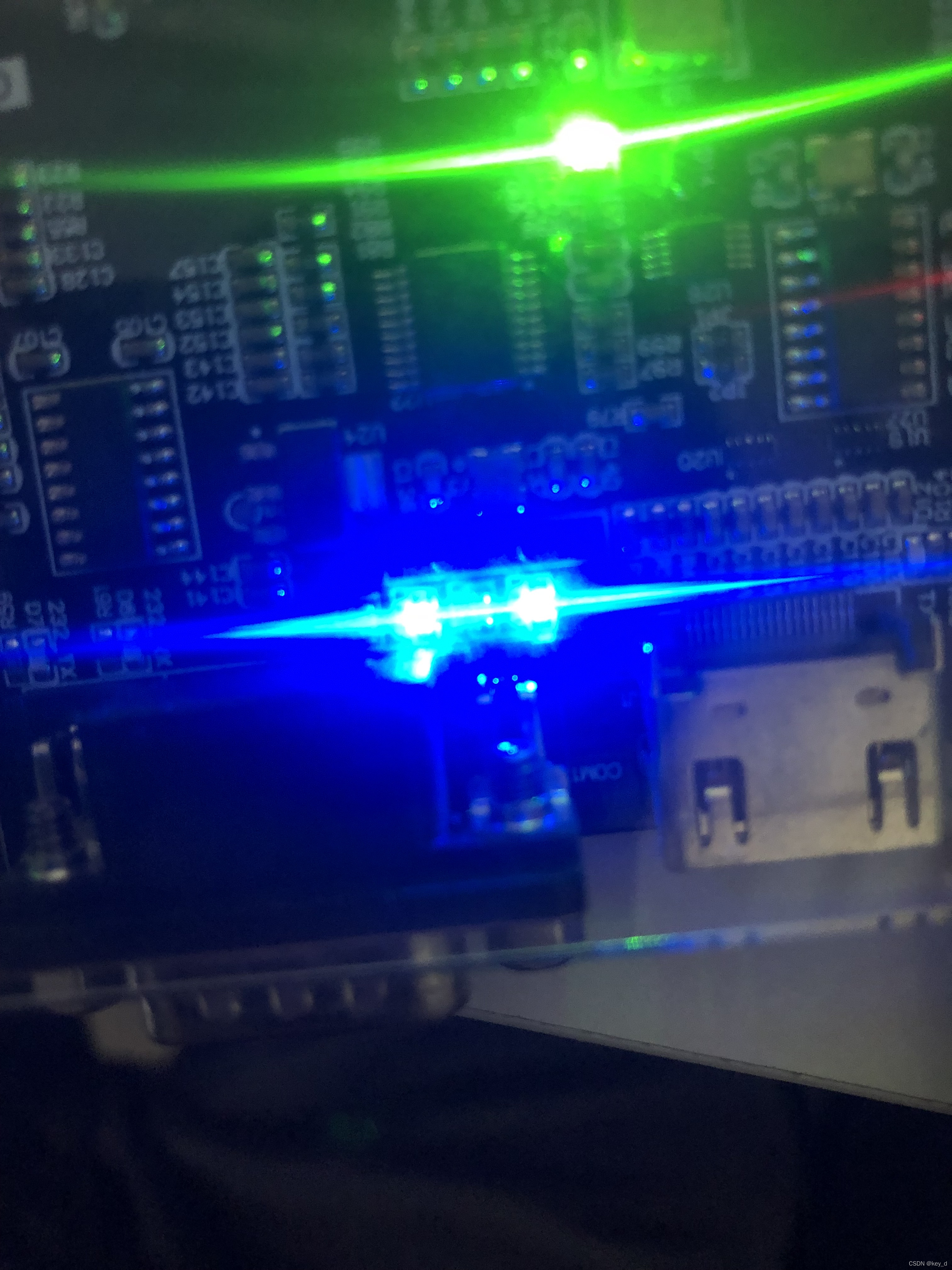

分配好引脚上板观察到4时钟以不同的频率闪烁。

通过频率较低的片外晶振倍频得到频率较高的时钟信号。利用ip核pll产生3个不同频率的时钟(25MHZ,75MHZ,100MHZ)

以及原有系统时钟50MHZ连接到led灯上最后上板观察。

编写一个计数器控制led亮灭的模块

在顶层中将其与pll产生的3个时钟连线,

仿真中观察到想要的波形评率

分配好引脚上板观察到4时钟以不同的频率闪烁。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?