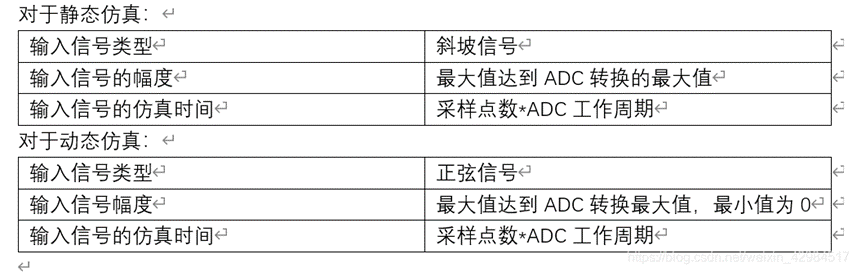

ADC电路主要存在静态仿真和动态仿真两类仿真,针对两种不同的仿真,我们存在不同的输入信号和不同的数据采样,因此静态仿真和动态仿真是完全不同的两个概念,所以设置的参数不同:

静态参数仿真:

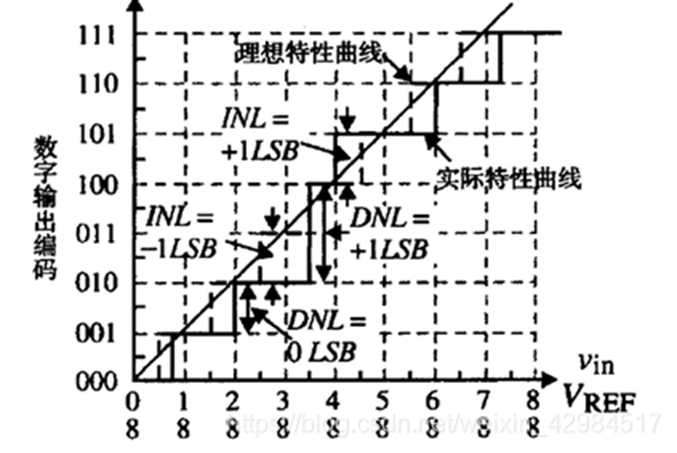

主要参数为INL DNL

输入斜坡信号作为激励

用WavevsWave 绘制出输入模拟量和数字编码之间的关系。利用calculator中的inl dnl函数进行计算。

动态参数仿真:

信噪比(SNR),信号噪声失真比(SINAD),有效位数(ENOB),总谐波失真(THD),无杂散动态范围(SFDR);

SNR:信噪比是输入信号和噪声(不包括任何谐波以及直流) 的功率比,衡量器件内部噪声大小的基本参数。

SINAD:SINAD是输入信号和所有输出信号失真功率(包括谐波成分,不包括直流)比,它测量的是输出信号所有传递函数非线性加上系统所有噪声(量化、抖动和假频)的累积效果。

ENOB: 表示ADC在转换过程中真正输出有效的位数。

THD: 总谐波失真是输入信号与系统所有谐波的总功率比,它可提供系统对称和非对称非线性产生的失真大小,用以表达其对信号的谐波含量的作用或者影响。

SFDR: 表示器件输入和输出之间的非线性

第一步:在ADC后面接一个理想的DAC(VerilogA实现)。根据需求修改所需要的位数。

可以在cadence得ahdLib库中找到dac_8bit_ideal元件参考

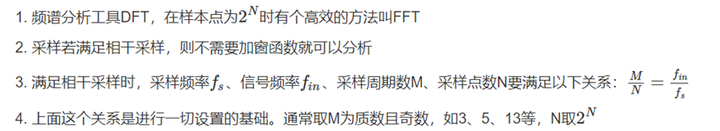

第二步:确定如何加激励(满足相干采样情况下,设定输入信号频率)。

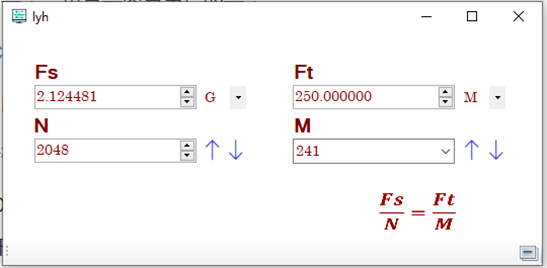

我这里使用编写得程序进行自动计算

下面说明手动计算具体如何实现:

1.确定采样率

设ADC CLK的周期为40ns,即频率为25MHz,设置采样周期为8CLK,转换周期是12CLK,因此采样时间间隔为20CLK,从而采样率为25M/20=1.25MSPS(1.25MHz)

采样率=CLK的频率除以(采样周期+转换周期)

(若采样周期为4CLK,采样率为25M/16=1.5625MSPS)

2.确定采样点N和周期数M

采样点取2^n,这样可以进行FFT分析。此处取M=3,N=128

3.确定AC分析的输入频率fin=fs*M/N

根据采样定理,输入频率要小于1.25M/2=0.625MHz=625KHz。若M=3,取N=128,则fin=1.25M*3/128=29.296875KHz

4.确定仿真时间

如果采样M个周期,每个周期时间1/fin,则:

T=M/fin=N/fs=128/1.25M=102.4us。仿真时,稍微多点时间,保证后面分析时,取数据取在非跳变处。比如仿真110us。由这个公式也可以看出,在采样率确定的情况下,N越大需要的仿真时间越长,而与输入信号频率无关。

接下来就是在电路图做好设置,就可以仿真啦。

如果仿真时间比较长,比如取4096个点,那仿真时间可能无法接受。可以考虑使用多核

在ADE窗口中:Setup>Environment,弹出如下窗口,加上:

+mt=20 +aps

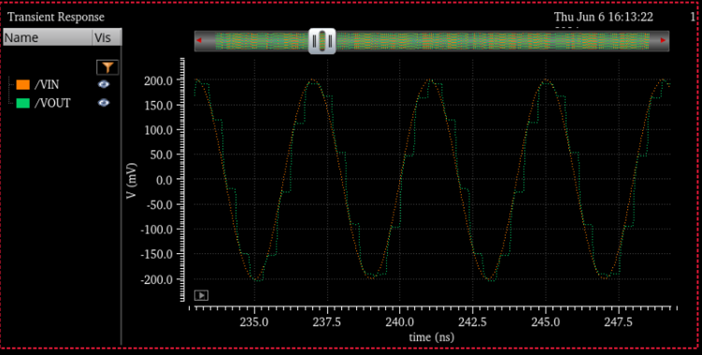

仿真完成后,波形大概如下:

从图中可以看出,正弦信号经过ADC转换,再经过理想DAC的转换,基本靠谱。

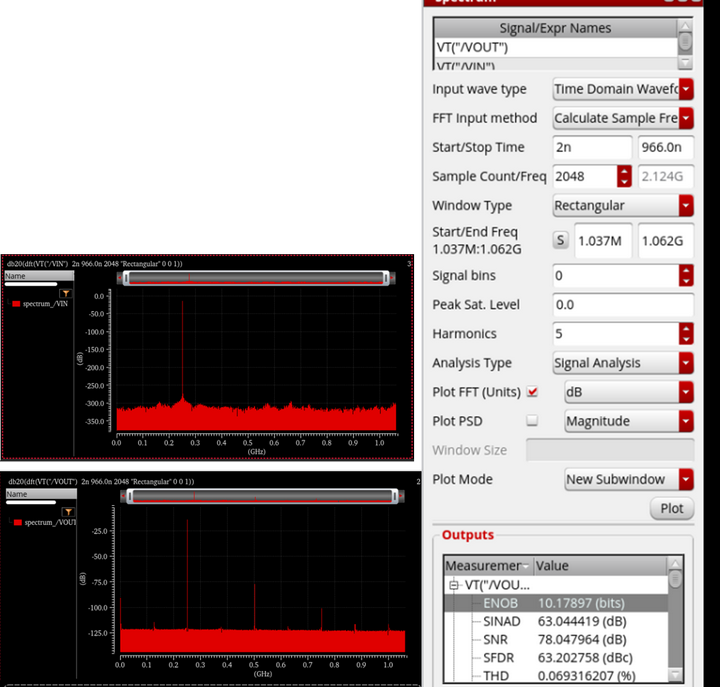

第三步:设置参数并查看结果

得到瞬态仿真波形后,接下来就是对信号进行频谱分析。

分析方法可以采用:

1. Cadence Spectrum工具2.MATLAB计算

下面说明在利用cadence的spectrum工具进行参数分析

开始时间:t0,结束时间:t0+M/ft

2.MATLAB计算

选中仿真出的输出信号波形-右键-send to-export,

选择格式为csv,start从一个稳定时刻开始,end默认就可以,step就是1/fs,比如50M,step就是20n,然后导出文件。

打开matlab代码main,修改读取的文件,运行得到ADC的输出频谱图及相关动态性能参数值。

3722

3722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?