基于Gm/id方法设计五管OTA

要求:

基于SMIC 0.18um工艺设计的五管OTA

拟定指标:CL=20pF,GBW=50MHz,VDD=3.3V

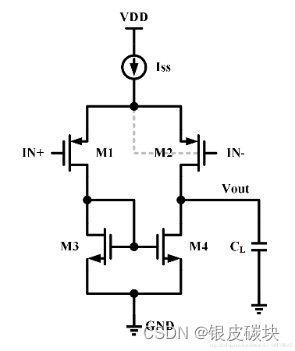

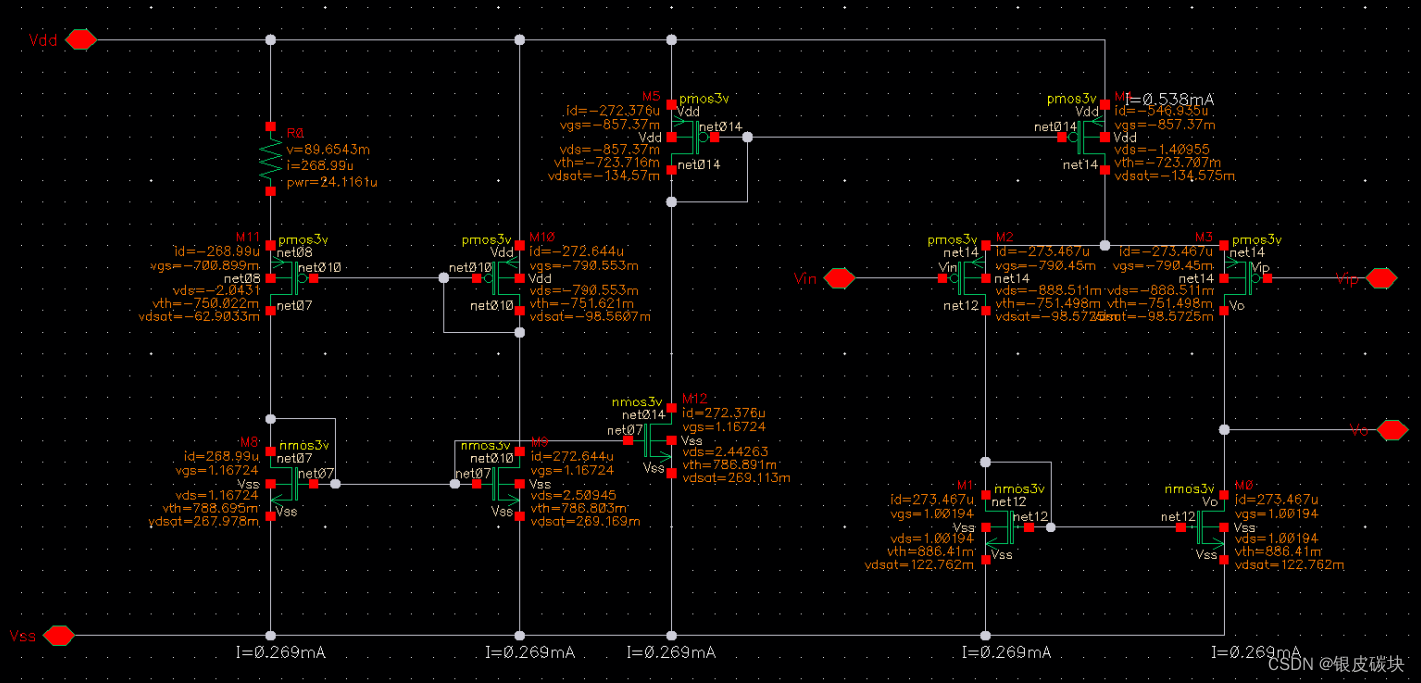

电路拓扑结构:

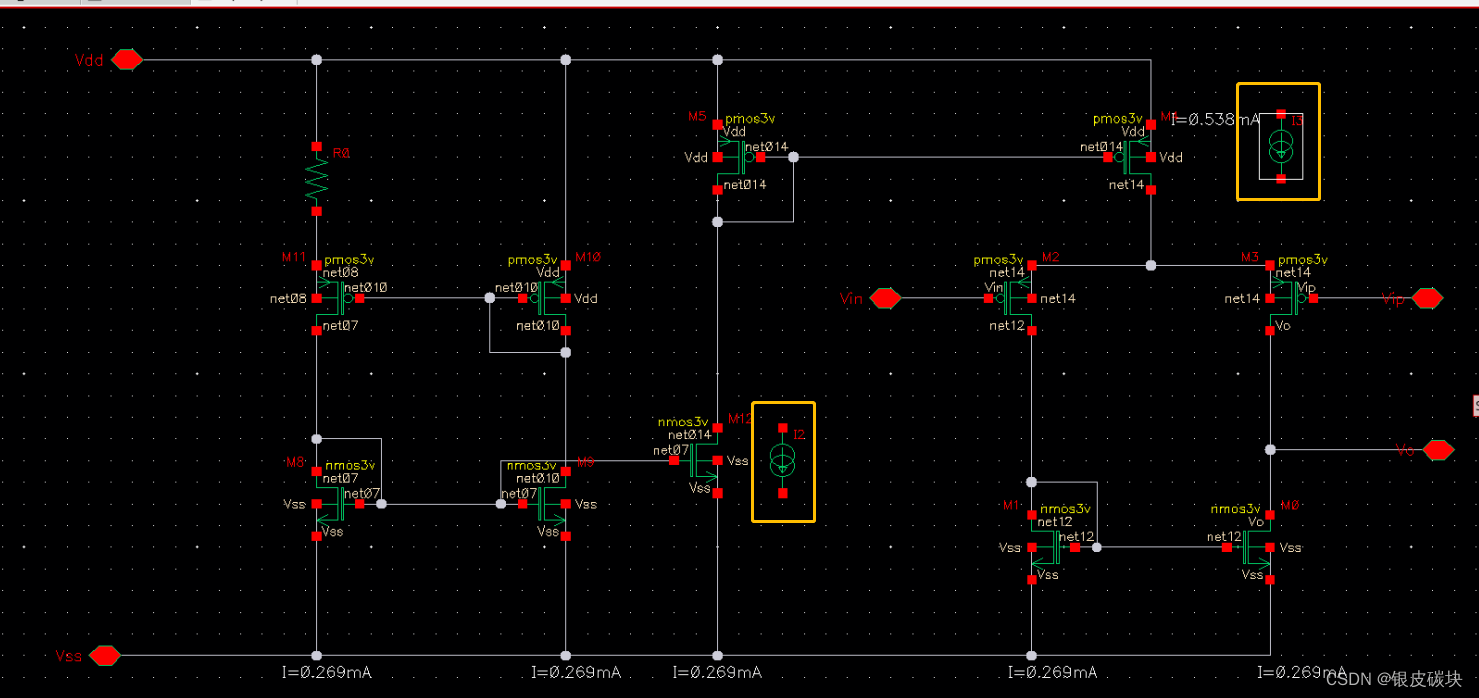

输入管采用PMOS,可以降低噪声。注意输入管的B端连接到S端。由于相同电流驱动能力下PMOS管的尺寸要更大,因此mul可以取大一些。

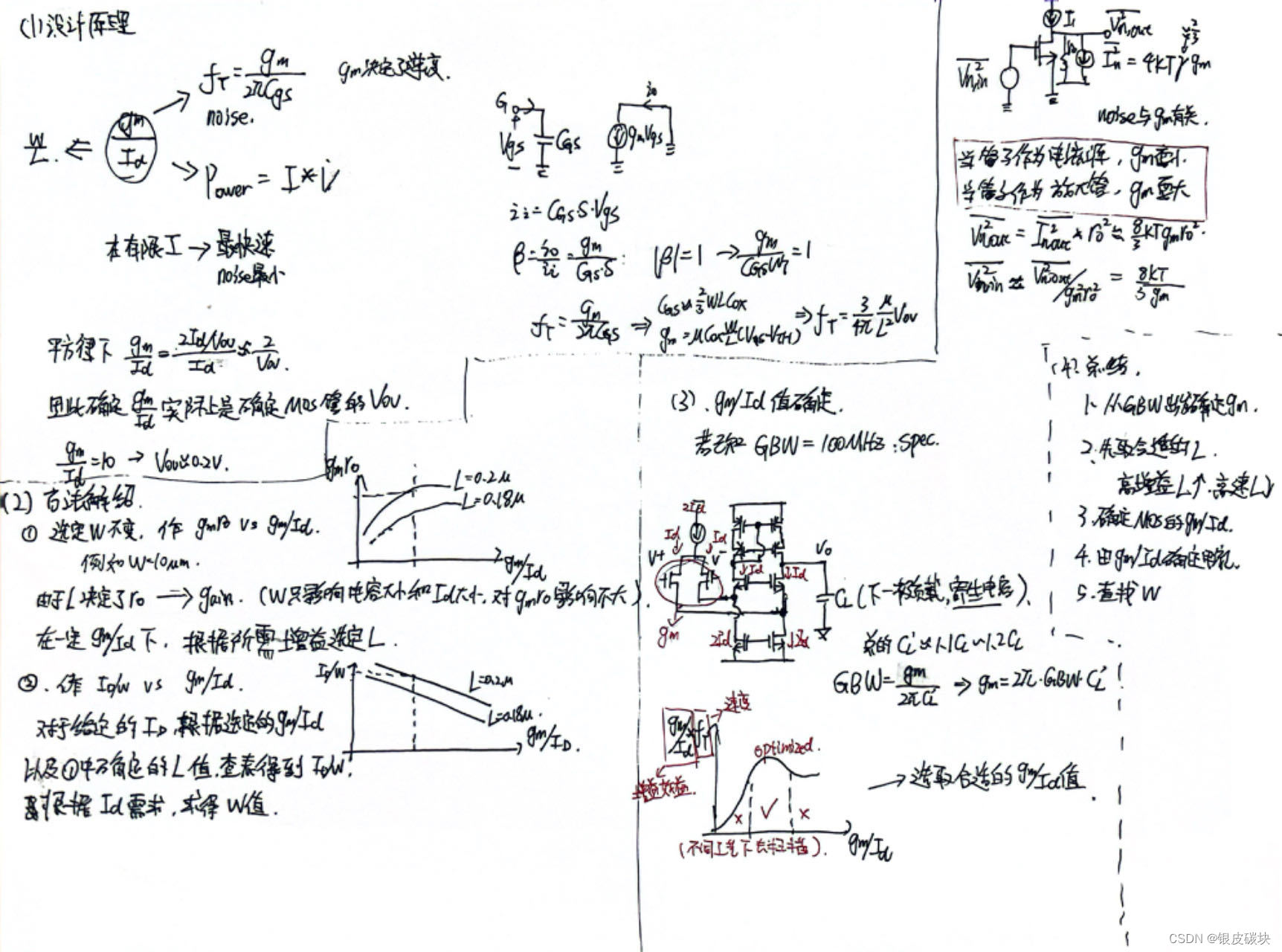

设计过程:

基于![]()

可以计算得到![]()

对于输入P管,取gm/id=14,得到id=0.269mA,Iss=2*id=0.538mA

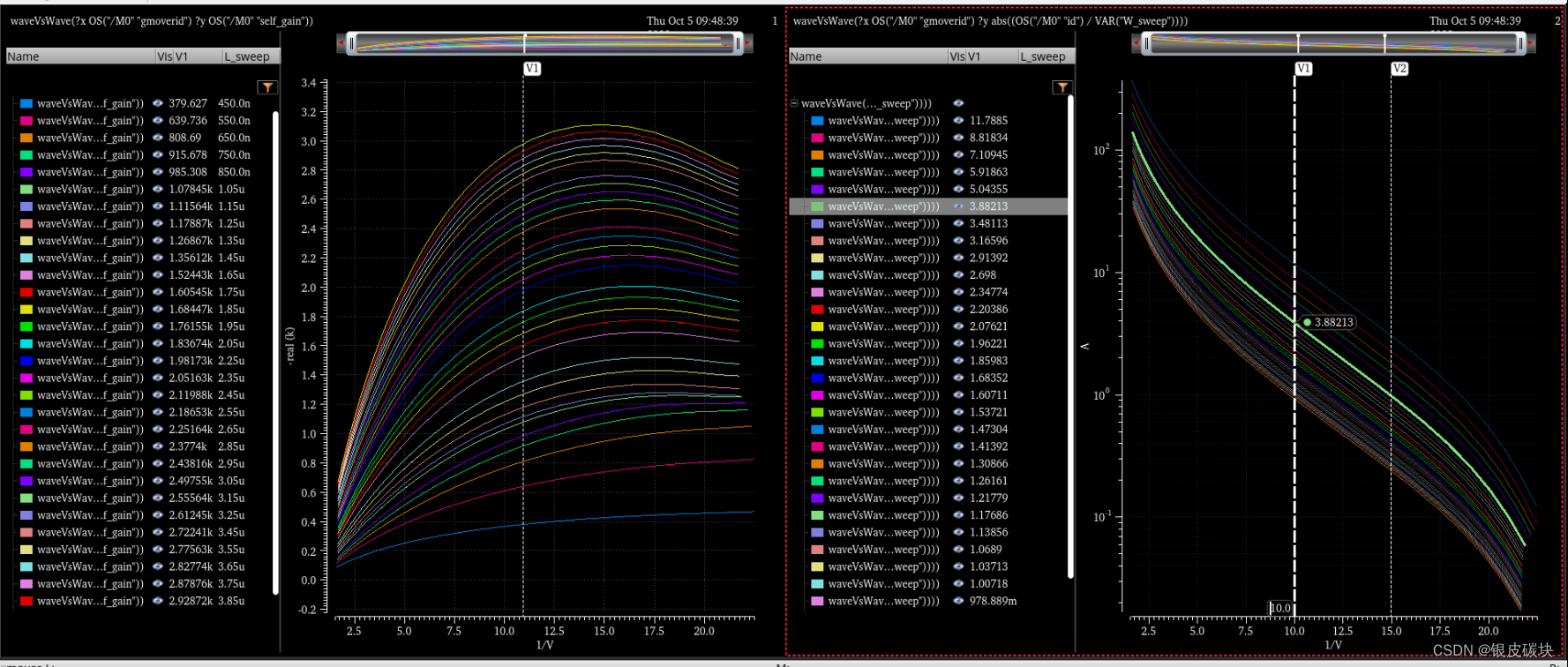

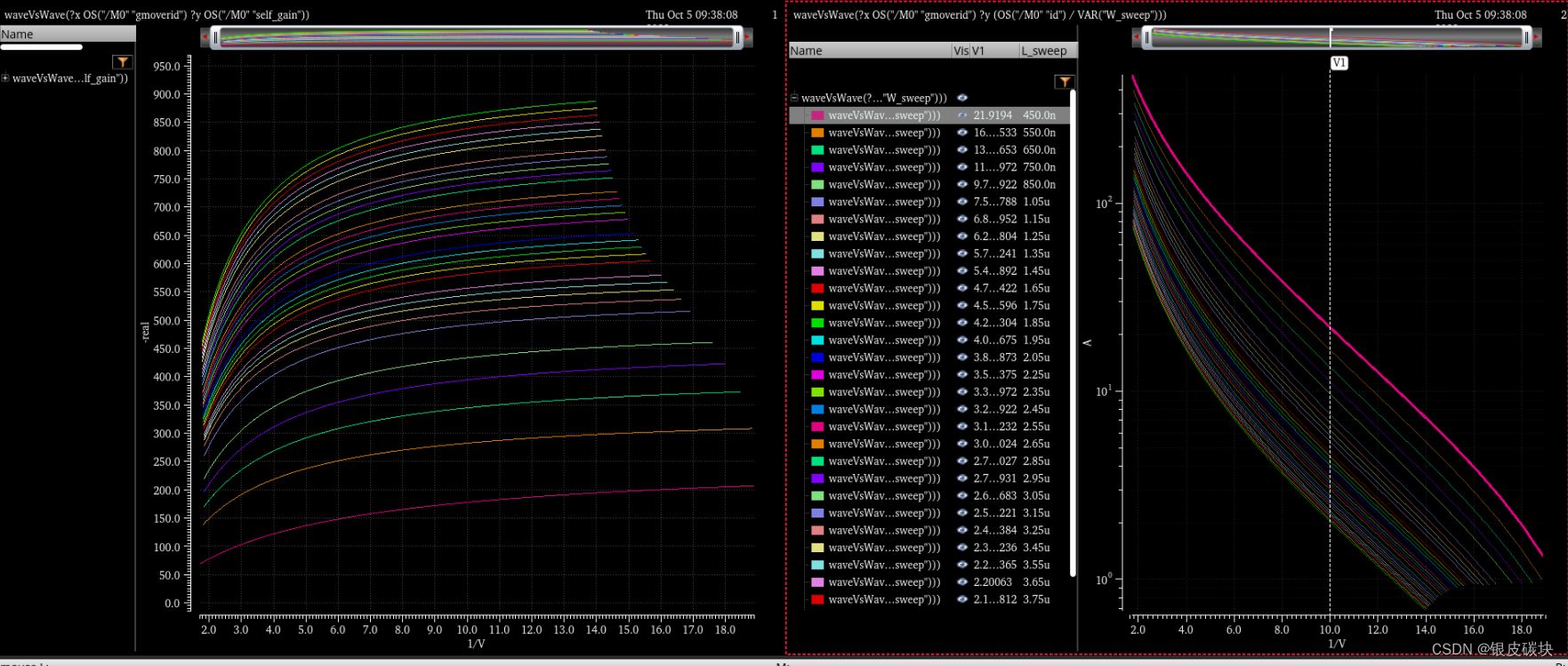

下面需分别测量PMOS和NMOS的本征增益 vs gmoverid和Id/W vs gmoverid

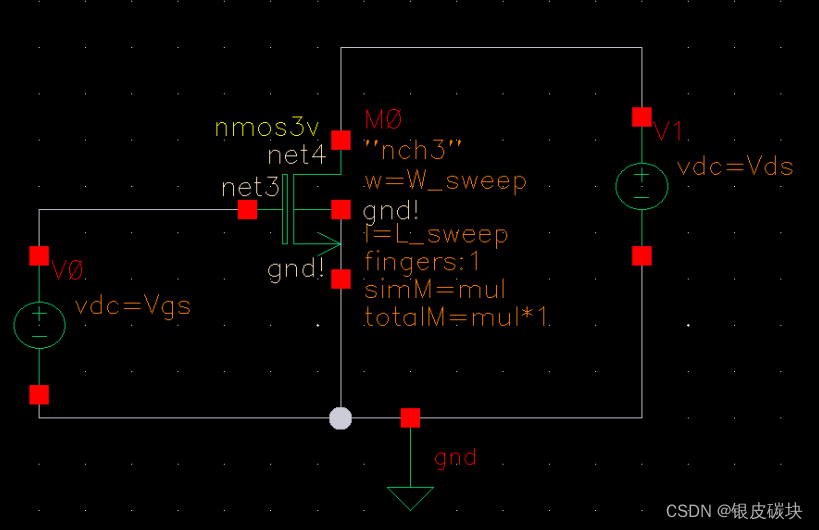

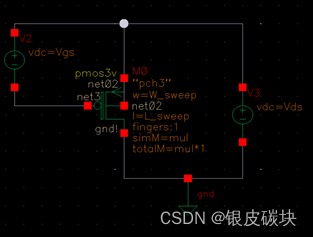

确保两个管子能工作在饱和区,对Vgs和L_sweep进行扫描

PMOS

NMOS

设置mul=8,取L=450nm(如果发现增益不够后面可以增大管子尺寸),得到id/w=4.02354A/m可计算出W=0.269*10^-3/4.02m=66.86um(此时selfgain=416,20lg(416)=52dB,增益肯定小于这个值,可以根据selfgain来选取更大的L)

对于N管,设置mul=4,可以取gm/id=10,得到id/W=21.9194A/m,计算得到W=0.269*10^-3/21.92m=12.27um

对于尾电流管,为了电流镜像的时候电流更准确,可以取较大的L值,选定L=2.05um,gm/id=10,同理可以计算得到得到W=289.27um

可以先使用电流源给一个Iref进行初步的验证,后面再做偏置电路。

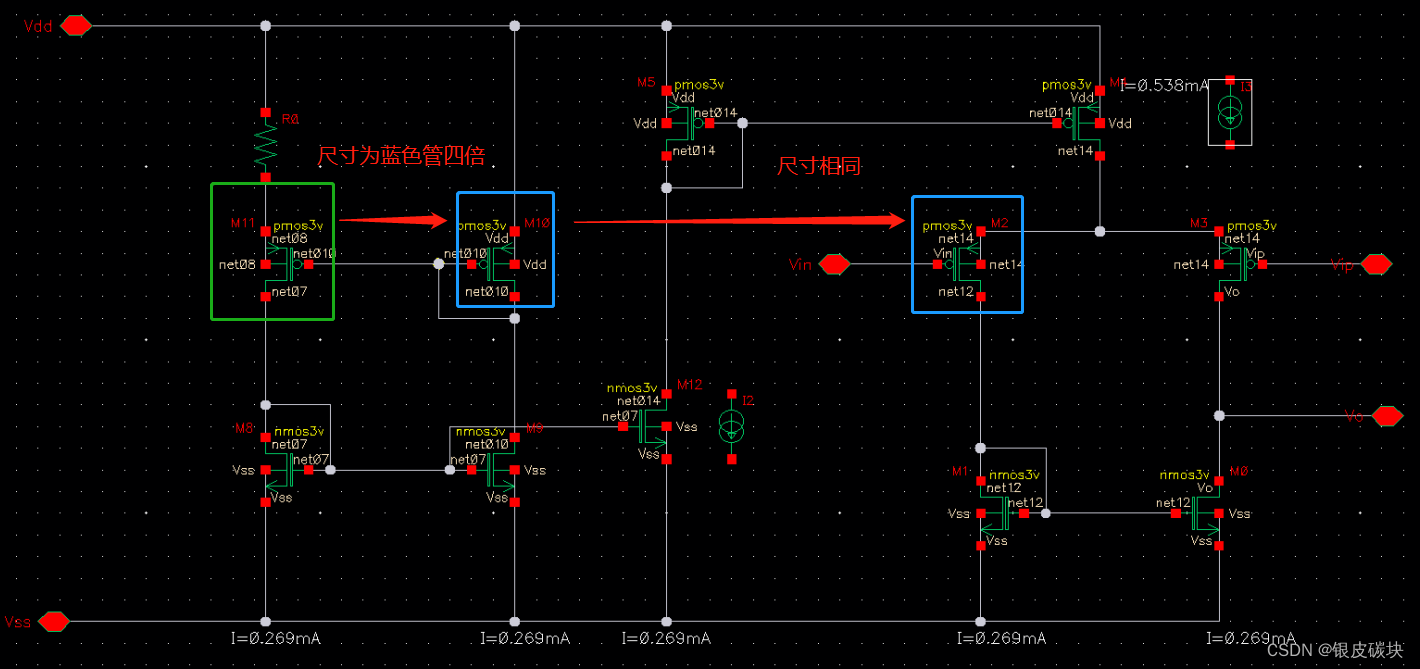

验证无误后,确定Iref的产生,常用的方式有使用bandgap来产生一个Vref,Vref/R得到Iref,还有一种方法就是constant gm bias 方式(也是本设计中采用的)。

近似有电阻R=1/gm=1/3.768=265Ω,通过设定R值,便能产生正确得Iref。电阻最后实际取值为333Ω,Iref与设计值相同。

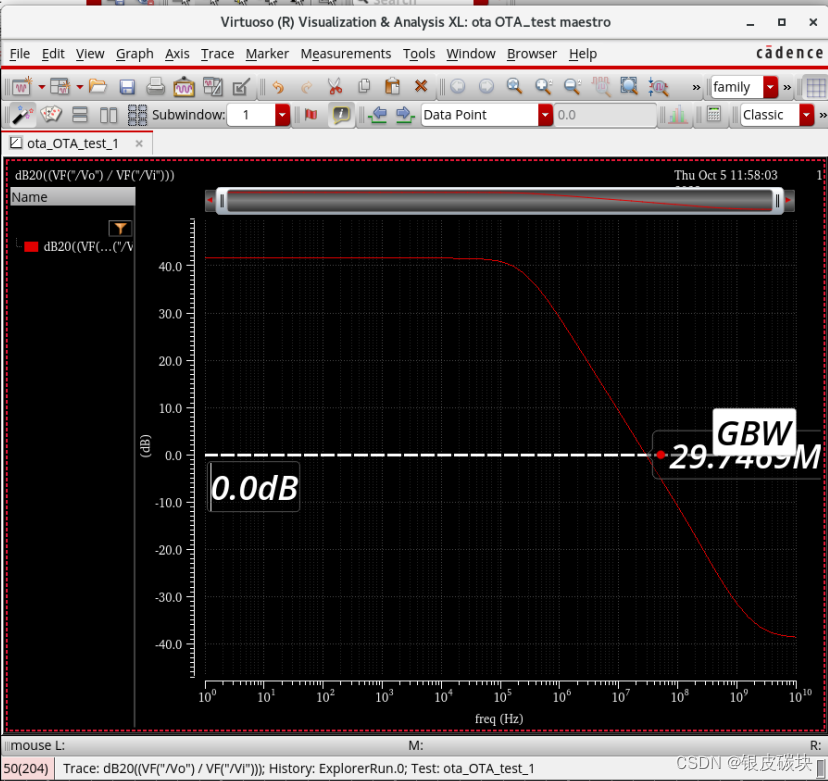

仿真结果:

最后仿真结果得到的GBW=29.7M,与设计指标有一定偏差,实际电路设计中,考虑到寄生电容的存在,一般取CL的1.2倍来计算。

参考资源:

1【高清】[part 7]How to design bias for your amplifier in gm_id methodology_哔哩哔哩_bilibili

2用Cadence Virtuoso IC617结合gm/id方法设计有源负载差动对(五管OTA)运放_菜鸡渣渣一个的博客-CSDN博客

3 用Cadence Virtuoso IC617和工艺参数设计有源负载差动对(五管OTA)运放_5管ota buffer_菜鸡渣渣一个的博客-CSDN博客

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?