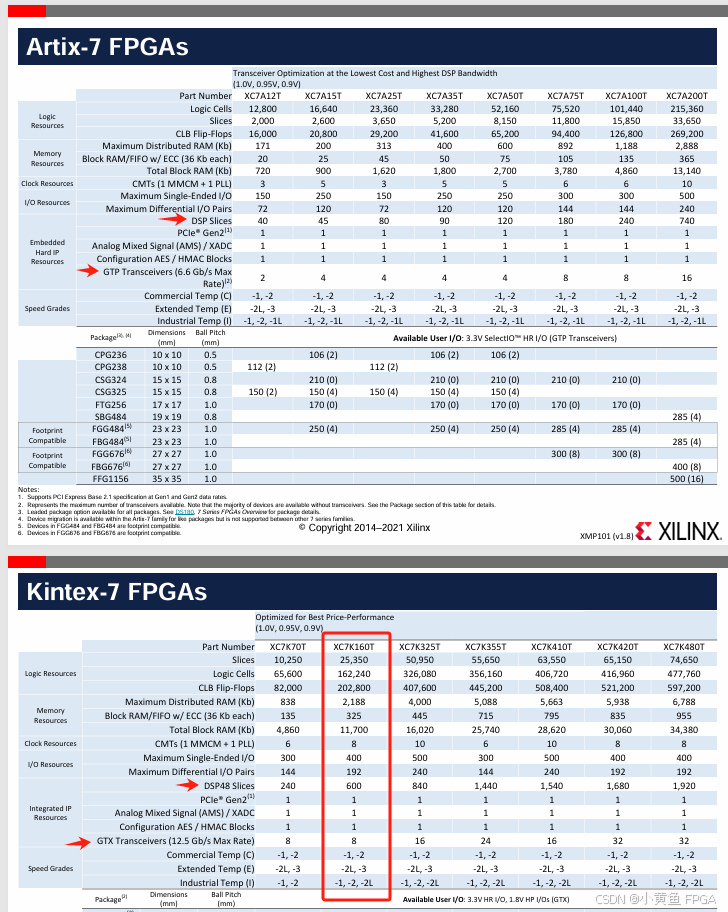

1. Kintex™ 7 与Artix 7系列

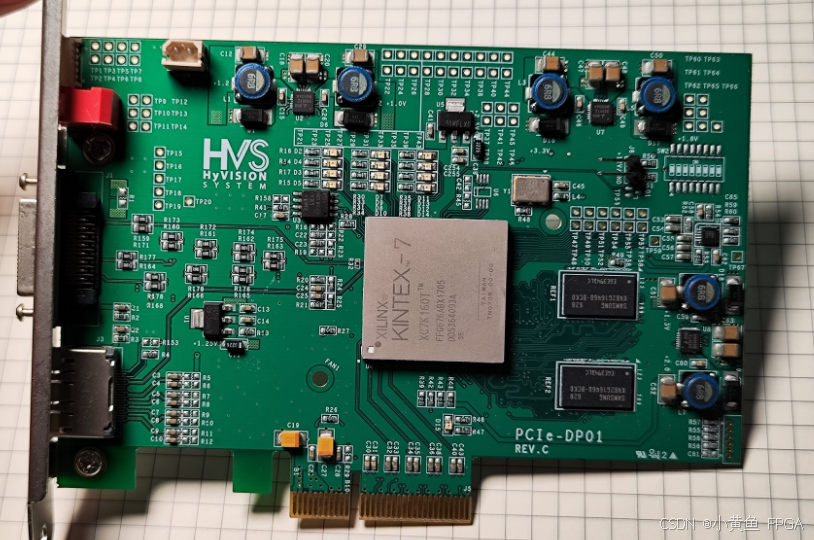

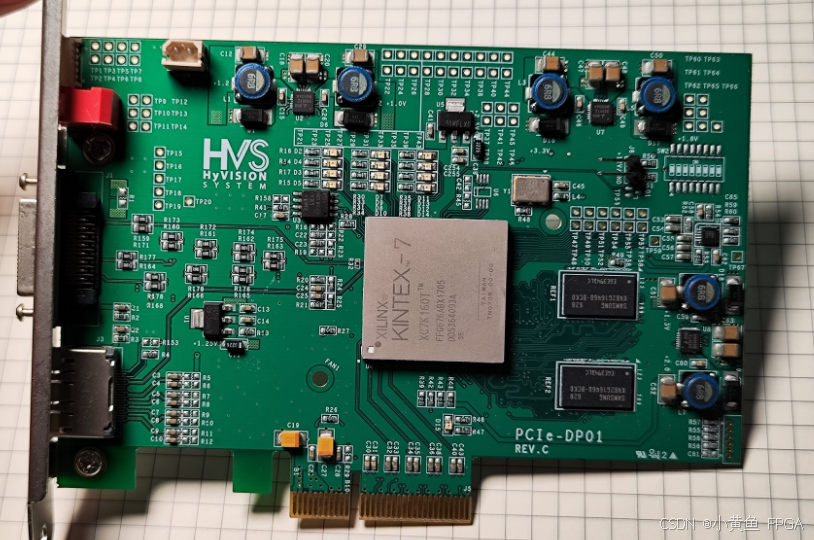

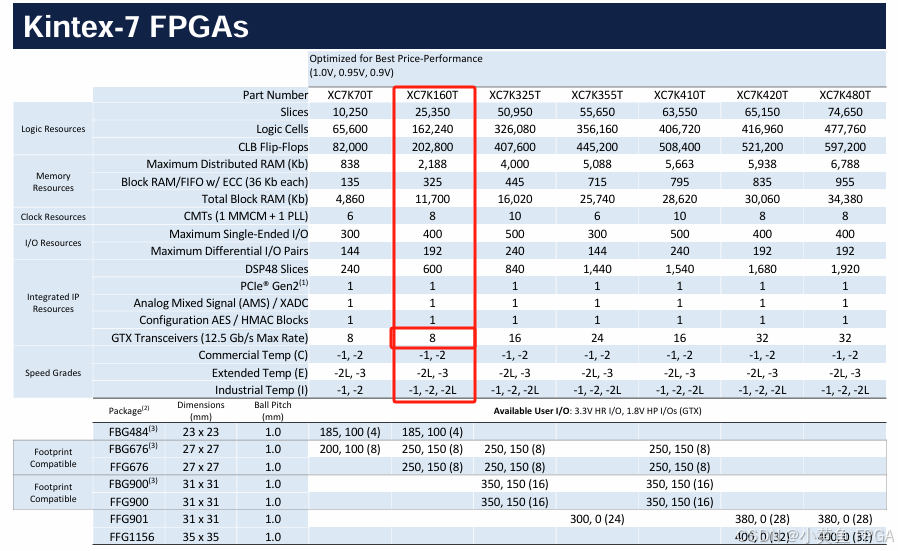

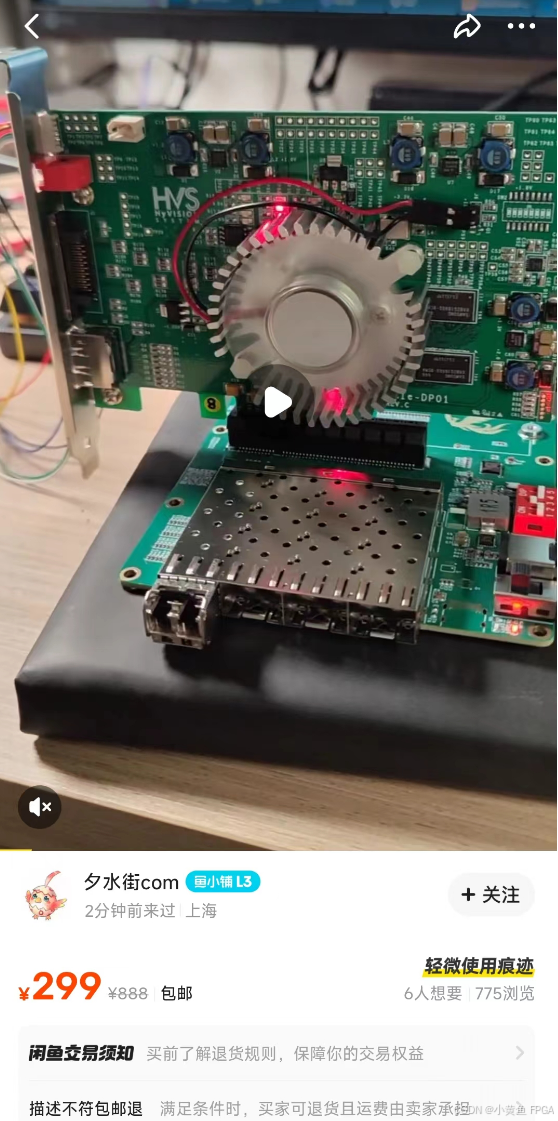

最近逛闲鱼发现一个好用的FPGA开发板,价格也是我能接受的XC7K160T的逻辑资源有162K

见下表。DSP资源有600个做些简单算法够了,Memory资源也多很多。相比于常见的A系列开发板而言,资源多了非常多。 并且高速收发器A系列是6.6Gb,而K系列是12.5Gb.文章末尾为小黄鱼出处

正点原子,黑金,等FPGA开发板通常是XC7A35T资源确实有点少。

2.板子 IO资源

资源列表

| U4 | FPGA : XC7K160T -FFG676 | 逻辑资源162K |

| U3 | SPI FLASH:W25Q64 | SPI FLASH 64M |

| U2/U7/U8 | 电源IC | |

| U1/U5 | 电源相关 稳压器等 | |

| Y1 | 200M CLK | DDR 时钟 |

| Y2 | 50M | |

| Y3 | 135M | |

| J1 | 36Pin 接口 | |

| J2 | JTAG接口 | |

| J3 | DP 接口(DIsplay Port) | 版本未知 |

| J5 | PCIE X4 | |

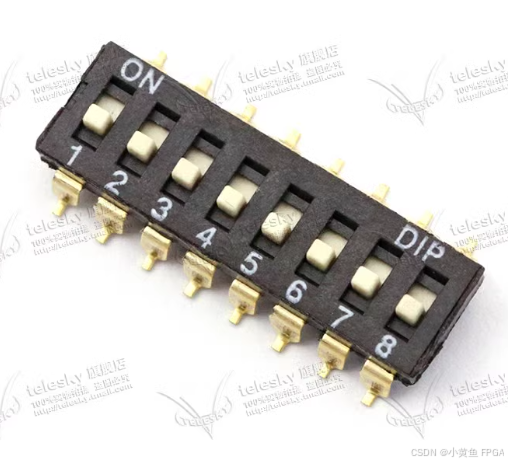

| SW2 | 8PIn 拨码开关 空焊接 |  |

| 内存 | K482G16460 | 三星DDR 颗粒 |

| D2~D14 | 14个 LED灯 |

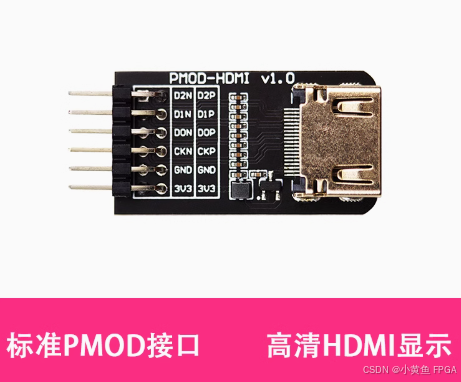

作为初学者或者需要低速扩展的人来说,最关心IO口的数量。如果有了IO可以轻易的买到一些小模块,用杜邦线搭建自己的接口。比如网口,USB,HDMI等。甚至正点原子,黑金的模块拿来用也非常方便

板子上大概拥有50+个IO口,也就是上图中原型的孔洞,自己焊接上排针,就拥有了非常多的IO资源。

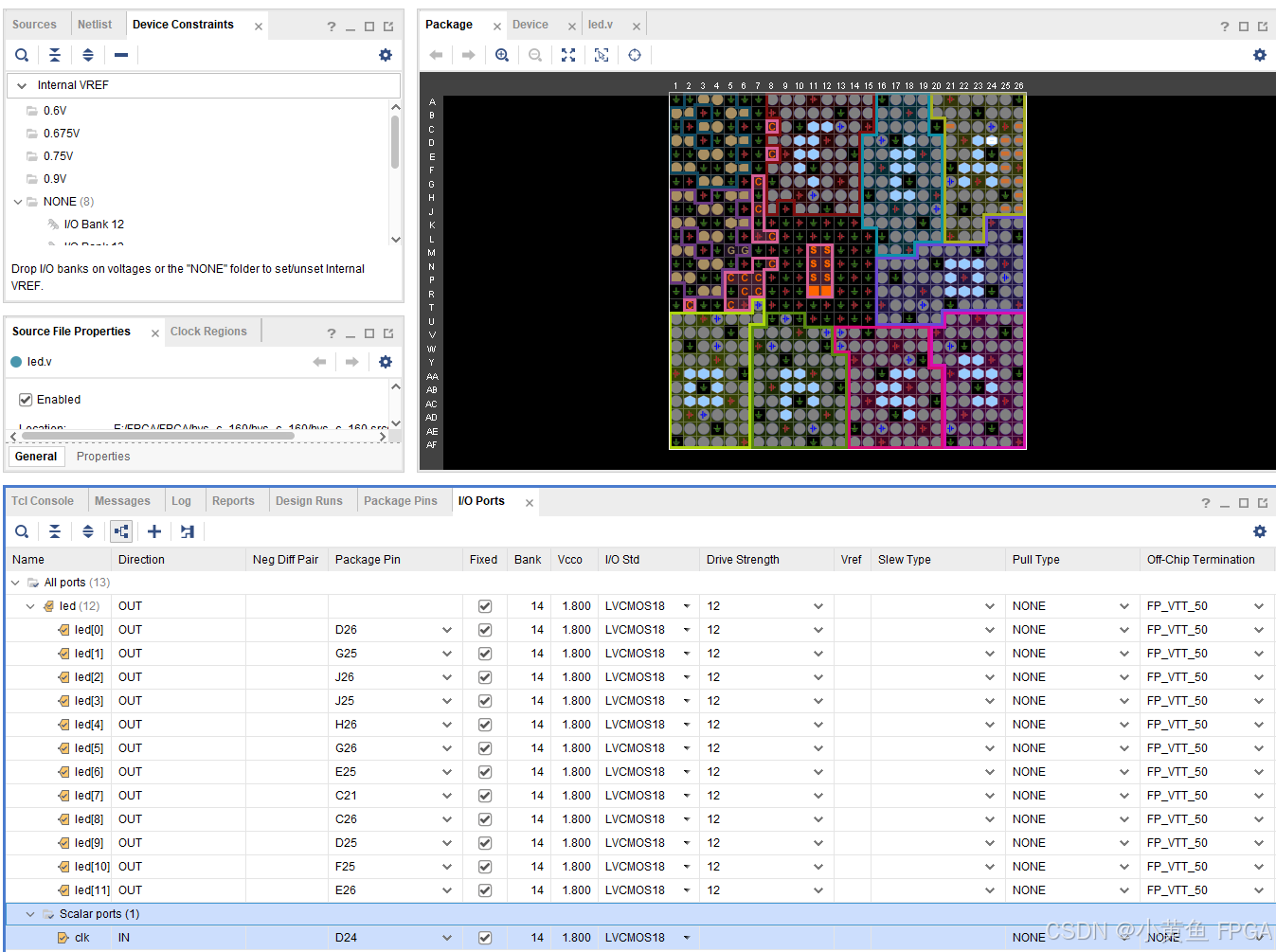

三:LED 点灯

module led(

input clk,

output reg [0:11] led

);

reg [0:31] cnt;

wire clk_1;

always@(posedge clk_1) begin

if(cnt> 5000000) begin

cnt <=0;

led<=led<<1;

end

else if(led==0)

led<=1;

else

begin

cnt<=cnt+1;

led<=led;

end

end

clk_wiz_0 instance_name1

(

// Clock out ports

.clk_out1(clk_1), // output clk_out1

// Clock in ports

.clk_in1(clk));

initial begin

cnt<=0;

led<=0;

end

endmodule 四:高速扩展口

四:高速扩展口

160T拥有高速口8个,看到板子用来PCIE X4 所以剩下 4个应该是用到了左方的J3 的DP接口上。

160T拥有高速口8个,看到板子用来PCIE X4 所以剩下 4个应该是用到了左方的J3 的DP接口上。

五:最后上图

1340

1340

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?