随着近年来人工智能的发展和大模型成果的涌现,人们正在逐渐探索AI的应用,将其用于各行各业之中,这一趋势也扩展到了大模型提供算力的芯片领域。2021年,谷歌在Nature发文《A graph placement methodology for fast chip design》,展示其AlphaChip模型在芯片设计领域的能力[1]。这项工作在谷歌内部被不断完善,已经应用于近年来谷歌的TPU、CPU设计中,证明了AI应用于芯片设计的可行性。

在传统芯片设计领域,受限于芯片设计周期,芯片,特别是专用芯片的更新迭代是要远落后算法的更新迭代的。这是因为芯片设计需要设计者基于算法进行硬件可行性优化,再布设硬件,随后进行流片,是一个长周期的过程。而应用AI于芯片设计,通过AI辅助芯片设计甚至通过AI自主设计芯片有望打破这一局限,缩短芯片和算法间的代际差距,在设计速度和成本管理上实现进一步提升。

下面我们将围绕“AI for Chip Design”列举事实案例,分析其智能程度、设计能力以及“AI for All Chip Design”的可能。

一.AI赋能传统芯片设计流程

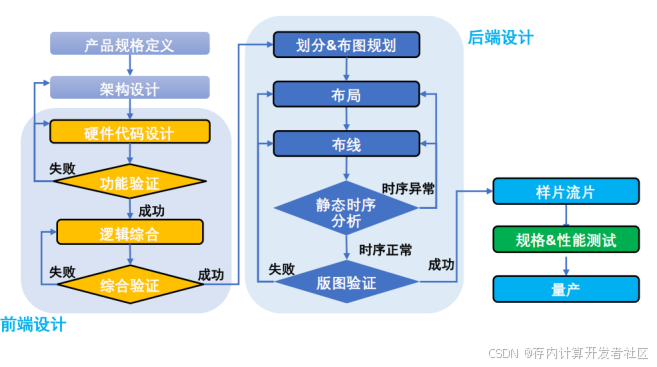

芯片设计是一个系统工程,其复杂程度不亚于构建一座大厦。整个流程可以概括为架构设计、前端设计、后端设计以及流片与验证四个阶段,如图1是数字芯片的设计流程。

(1)架构设计阶段,始于产品规格定义,明确芯片的具体需求。在此基础上,架构师需要制定出芯片的顶层架构,为后续的设计奠定基础。这一步至关重要,直接决定了芯片的功能、性能和功耗等关键指标。

(2)前端设计阶段,工程师根据架构设计,使用硬件描述语言进行硬件代码设计,将架构方案转化为具体的代码。为了确保代码的功能正确性,需要进行功能验证;若验证失败,则返回代码设计阶段进行修改。验证通过后,进入逻辑综合步骤,将代码转换为门级网表。最后,还需要进行综合验证,确保综合结果符合预期,否则将退回逻辑综合阶段进行调整。

(3)后端设计阶段,则专注于芯片的物理实现。首先进行划分和布图规划,确定各个模块的位置。然后是布局,将各个单元放置到芯片上。紧接着是布线,将各个单元用导线连接起来。为了确保时序性能,需要进行静态时序分析;若时序异常,则需返回布局或布线阶段进行优化。时序正常后,还需进行版图验证,确保版图符合制造要求。

(4)最后是流片与验证测试阶段,根据设计数据进行样片流片后,需要对样片进行规格和性能测试,验证其是否满足最初定义的产品规格。测试通过后,芯片才能最终进入量产阶段。

图1数字芯片设计传统流程

然而,传统的芯片设计方法高度依赖人工经验,效率较低且周期较长。近年来,AI的兴起为芯片设计领域带来了新的机遇,其强大的学习和优化能力使其在多个设计环节都能发挥重要作用。

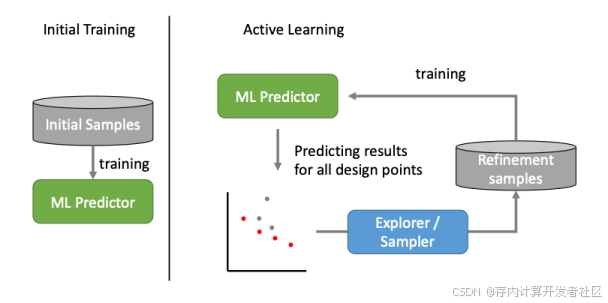

在架构设计阶段,AI可以辅助架构师进行更高效的设计空间探索(DSE)[2]。 传统的DSE严重依赖于工程师的经验和直觉,而AI可以通过机器学习算法,例如强化学习和遗传算法,来快速评估和优化不同架构方案的PPA(功耗、性能、面积)。这使得架构师能够在更短的时间内探索更广阔的设计空间,并找到更优的架构方案。

图2 AI辅助DSE过程[2]

在前端设计阶段,AI可以加速验证和逻辑综合的过程。对于功能验证,AI可以通过智能化的测试用例生成和覆盖率分析,提高验证的效率和完整性。例如,基于生成对抗网(GAN)的方法可以生成更具针对性的测试用例,从而更快地发现设计中的bug。在逻辑综合方面,AI 可以利用形式化方法和推理技术,例如,通过图神经网络(GNN)来优化电路的逻辑结构,提高综合的效率和质量。

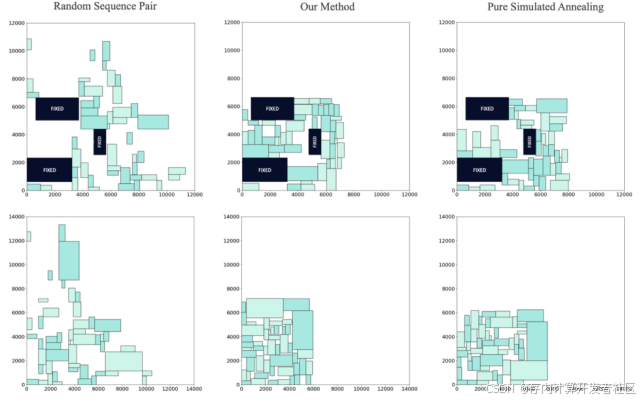

在后端设计阶段,AI可以赋能更高效的布局布线和版图验证。布局布线是后端设计中最为耗时的步骤之一,而AI可以通过强化学习等算法,学习到更优的布局布线策略,实现更优的布线路径和更低的拥塞。例如,谷歌的DeepMind团队就利用强化学习实现了芯片的自动布局,其结果在某些指标上超越了人类专家。此外,AI还可以利用图像识别技术,例如卷积神经网络(CNN),加速版图验证过程,更快地识别出版图中的违规问题。

图3 利用模拟退火算法实现布局优化(中)[3]

在流片与验证阶段,AI可以帮助自动化测试向量生成和失效分析。AI可以基于历史数据和机器学习模型,例如长短期记忆网络(LSTM)或者Transformer模型,自动学习并生成更有效的测试向量,提高测试的覆盖率和效率。同时,AI还可以对测试结果进行智能分析,例如通过聚类分析和关联规则挖掘,快速定位失效原因,加速芯片的调试和改进。

总而言之,AI技术在芯片设计的各个阶段都展现出了巨大的潜力,有望推动芯片设计流程的自动化和智能化,从而大幅提升效率并缩短研发周期。将 AI 技术与传统的EDA工具相结合,将是未来芯片设计领域的重要发展方向。

二.现有AI自动化芯片设计研究

AI辅助芯片设计的巨大潜力吸引了学术界和工业界的众多科研人员投入其中,已经取得了显著成果,比如英伟达的ChipNeMo等。本小节将简单概括现有AI自动化芯片设计研究和成果。

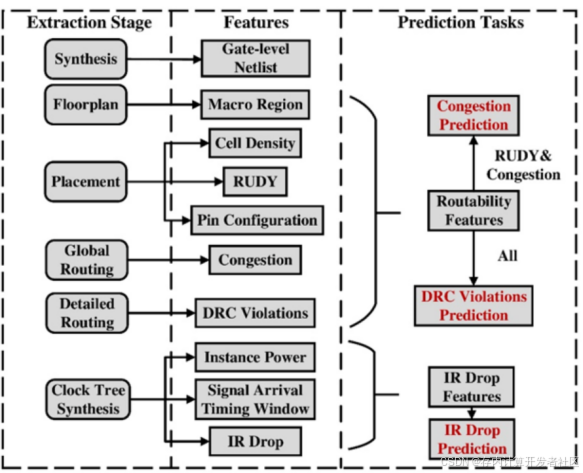

(1)北京大学CircuitNet[4]

2022年9月,北京大学黄如院士团队的林亦波研究员、王润声教授等创建了首个致力于芯片设计AI for EDA应用的开源数据集——CircuitNet,包含1万以上数据样本,涵盖从实际制造工艺PDK下数字设计流程不同阶段中提取到的各类特征。CircuitNet主要包含大规模、多样性、多任务、标准化等特性,数据主要来源于6个开源RISC-V芯片设计。整体流程和特征提取环节如下图4所示:

图4 整体流程和特征提取环节示意图[4]

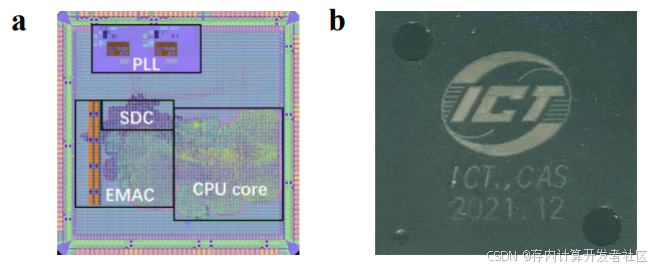

(2)中科院计算所启蒙1号[5]

2023年6月,中科院计算所的处理器芯片全国重点实验室及其合作单位,用AI技术设计出了世界上首个无人工干预、全自动生成的CPU芯片——启蒙1号。这颗完全由AI设计的32位RISC-V CPU,采用64nm工艺,频率可达300MHz,相比GPT-4目前所能设计的电路规模大4000倍,并可运行Linux操作系统,且性能堪比Intel 486,有望颠覆传统的芯片设计流程,芯片如图5所示。研究人员采用AI技术直接从测试用例的输入-输出(IO)自动生成CPU设计,无需工程师提供任何代码或自然语言描述,仅用5小时就生成了400万逻辑门,同时在符号主义的框架下从理论上保证了功能正确性,颠覆了传统流程中的逻辑设计和功能验证环节。

图5 启蒙1号芯片版图及实物图[5]

(3)英伟达ChipNeMo[6]

2023年10月,英伟达发布了一个以自家内部数据为基础训练而成定制大语言模型——ChipNeMo,用于AI芯片设计,可以帮助工程师完成与芯片设计相关的任务,具体地,包括回答有关芯片设计的一般问题、总结bug文档,以及为EDA工具编写脚本等等。ChipNeMo采用多种领域自适应技术以使大语言模型适应芯片设计领域,同时采用检索增强生成以提高特定领域问题的答案质量。研究人员通过工程助手聊天机器人、EDA脚本生成以及故障总结和分析三个具体应用,对ChipNeMo进行了实测评估,均取得了显著成效。目前,ChipNeMo仅供内部使用,并且由于使用了英伟达内部数据进行训练,未来对外开源的可能性不大,但是ChipNeMo对于推动AI辅助芯片设计研究进展仍具有重大意义。

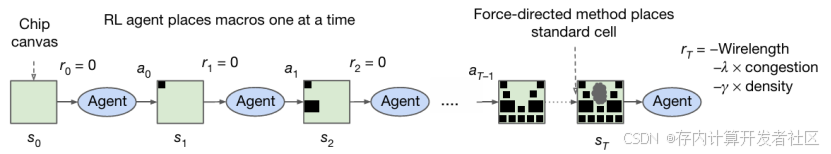

(4)谷歌AlphaChip

谷歌DeepMind团队早在2020年便开始探索人工智能在芯片设计领域的潜力,并率先发表预印本论文,介绍了其用于芯片布局设计的全新强化学习方法。 随后,该研究成果于2021年发表在《Nature》杂志上,题为《A graph placement methodology for fast chip design》[1],方法及训练方案概述如图6所示。 此后,谷歌团队持续对该方法进行改进。2024年9月,团队在《自然》杂志上发布附录《Addendum: A graph placement methodology for fast chip design》[7],详细阐述了该方法的具体细节及其对芯片设计领域的影响,并公开了模型权重,公布模型名称为AlphaChip。AlphaChip采用强化学习和一种新型的“基于边缘”的图神经网络,学习芯片组件之间的互连关系,并在不同芯片之间实现泛化,使其设计能力随着每次布局不断提升。与人工设计需耗时数月相比,AlphaChip仅需数小时即可完成芯片布局设计,显著提高了效率。更重要的是,其设计方案在功耗和性能方面往往优于人工设计。 实际上,包括最新一代Trillium(第六代)在内的每一代TPU,AlphaChip都设计出了更优的芯片布局和更多总体布局图。尽管目前AlphaChip的应用仅限于有限的芯片模块,大部分设计工作仍需人工完成,但其在未来拥有巨大潜力,有望优化芯片设计周期的每一个阶段。

图6 方法及训练方案概述[1]

(5)Synopsys与Microsoft的Synopsys.ai Copilot[8]

2023年11月,Synopsys和Microsoft合作开发了Synopsys.ai Copilot,将Azure OpenAI生成式AI功能与Synopsys业界领先的芯片设计工具和IP结合在一起,以突破性的生成式人工智能性能加速芯片设计。Synopsys.ai Copilot是新思科技规划中的生成式AI系列的首款产品,其特色在于学习全新的技能并与团队的需求一起成长,让芯片设计与制造厂商可以更轻松地提升生产力,并达成芯片设计从架构的探索、设计到制造的所有阶段的设计目标。同时,Synopsys.ai Copilot可在任何本地或云环境中部署,将Microsoft Azure按需高性能计算基础设施与可用性、经济性和处理AI工作负载的能力相集成,以实现高级芯片设计和验证应用程序。目前Synopsys.ai Copilot被AMD和英特尔等一些全球领先的芯片公司采用,这些公司报告称其芯片设计成果得到了显着改进。

综上所述,AI在芯片设计领域展现出巨大的应用潜力,有望大幅提升设计效率、优化芯片性能并降低研发成本。目前,该领域已取得一系列令人瞩目的研究成果,例如:AI for EDA数据集的构建和完善;AI驱动的芯片自主设计;辅助芯片设计的大语言模型;集成生成式AI功能的EDA设计套件。我们有望看到AI能够承担更复杂的设计任务,实现更高程度的自动化,甚至催生全新的芯片设计范式。

三.展望AI for All Chip Design

本文汇总了现有的主流自动化芯片设计模型及其成果,其展现出的能力及芯片效果令人惊叹。

但我们必须同样认识到AI设计芯片在当前时代下在设计能力、设计时效性等方面局限。回到文章开头的例子,谷歌近年已将AI用于TPU、CPU设计,从实际效果来看,谷歌最新的使用三星4nm工艺的Tensor G4手机芯片,在CPU规格上远不及同期相同定位的苹果A18 Pro、骁龙8 Elite、联发科天玑9400,性能更是远远落后竞争对手,大概和麒麟9020打的有来有回。具体来说,Tensor G4的CPU在设计思路上更像是去年的旗舰处理器,而今年的旗舰处理器普遍采用了更高规格进行设计制造。不禁令人联想,是否谷歌的AI还在按照训练好的旧有思维设计芯片,在时间上来不及重新训练模型以顺应竞争对手的变化;又或者换一个角度,人没能及时地做出决策,进而依赖AI设计出了符合传统预期地芯片。这似乎是人或者说决策在芯片设计过程中重要性的一个证明。

不管怎样,AI已经证明了其在芯片设计辅助领域的强大能力,作为芯片领域的从业者,也许在不久的将来,我们就能见证AI for EDA,通过商业化AI软件辅助芯片设计,降低设计难度和成本,实现真正的“AI for All Chip Design”。

参考文献

- Mirhoseini A, Goldie A, Yazgan M, et al. A graph placement methodology for fast chip design[J]. Nature, 2021, 594(7862): 207-212.

- Huang G, Hu J, He Y, et al. Machine learning for electronic design automation: A survey[J]. ACM Transactions on Design Automation of Electronic Systems (TODAES), 2021, 26(5): 1-46.

- Vashisht D, Rampal H, Liao H, et al. Placement in integrated circuits using cyclic reinforcement learning and simulated annealing[J]. arXiv preprint arXiv:2011.07577, 2020.

- Chai zhuomin, Zhao Yuxiang, Lin Yibo, Liu Wei, Wang Runsheng, Huang Ru, CircuitNet: An Open-Source Dataset for Machine Learning Applications in Electronic Design Automation (EDA) , In Journal of SCIENCE CHINA Information Sciences , 2022.

- Cheng S, ** P, Guo Q, et al. Pushing the limits of machine design: Automated CPU design with AI[J]. arxiv preprint arxiv:2306.12456, 2023.

- Liu M, Ene T D, Kirby R, et al. Chipnemo: Domain-adapted llms for chip design[J]. arxiv preprint arxiv:2311.00176, 2023.

- Goldie A, Mirhoseini A, Yazgan M, et al. Addendum: A graph placement methodology for fast chip design[J]. Nature, 2024: 1-2.

- 新思科技推出Synopsys.ai Copilot以突破性的生成式AI效能加速晶片设计,https://www.synopsys.com.

3016

3016

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?