一、认识HLS

什么是HLS

高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时钟或时序的概念。相比之下,诸如Verilog、VHDL、SystemVerilog等低层次语言,通常用来描述时钟周期精确(cycle-accurate)的寄存器传输级电路模型,这也是当前ASIC或FPGA设计最为普遍使用的电路建模和描述方法。

HLS与Verilog编程技术的关系

VHDL和Verilog是传统的硬件描述语言,用于手动编写硬件逻辑。与HLS技术相比,它们需要更多的时间和精力来编写和调试代码,但也提供了更高的灵活性和控制力。HLS技术和VHDL/Verilog编程技术可以结合使用,以便在设计过程中兼顾效率和灵活性。

二、Vivado的安装下载

下载:

Vivado资源地址: Vivado2018.3

网盘提取码:sygh

安装:

解压Xilinx_Vivado_SDK_2018.3_1207_2324.tar文件

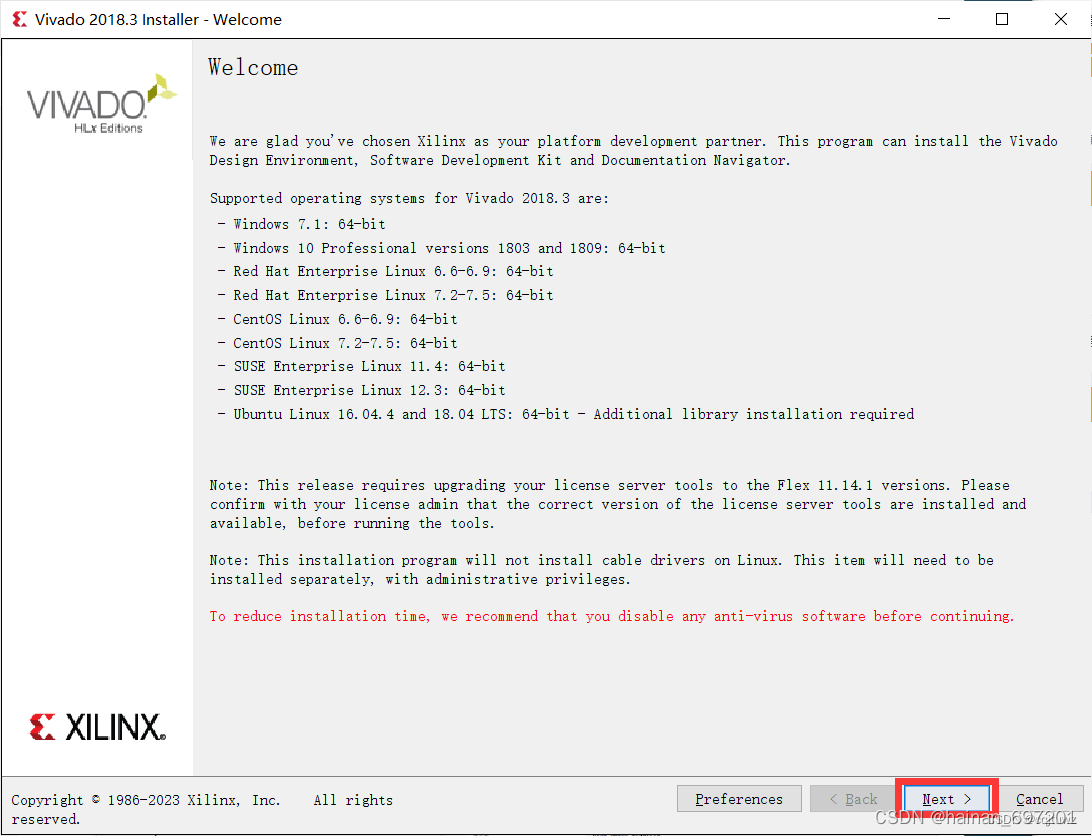

在解压得到的文件中选择运行setup.exe文件

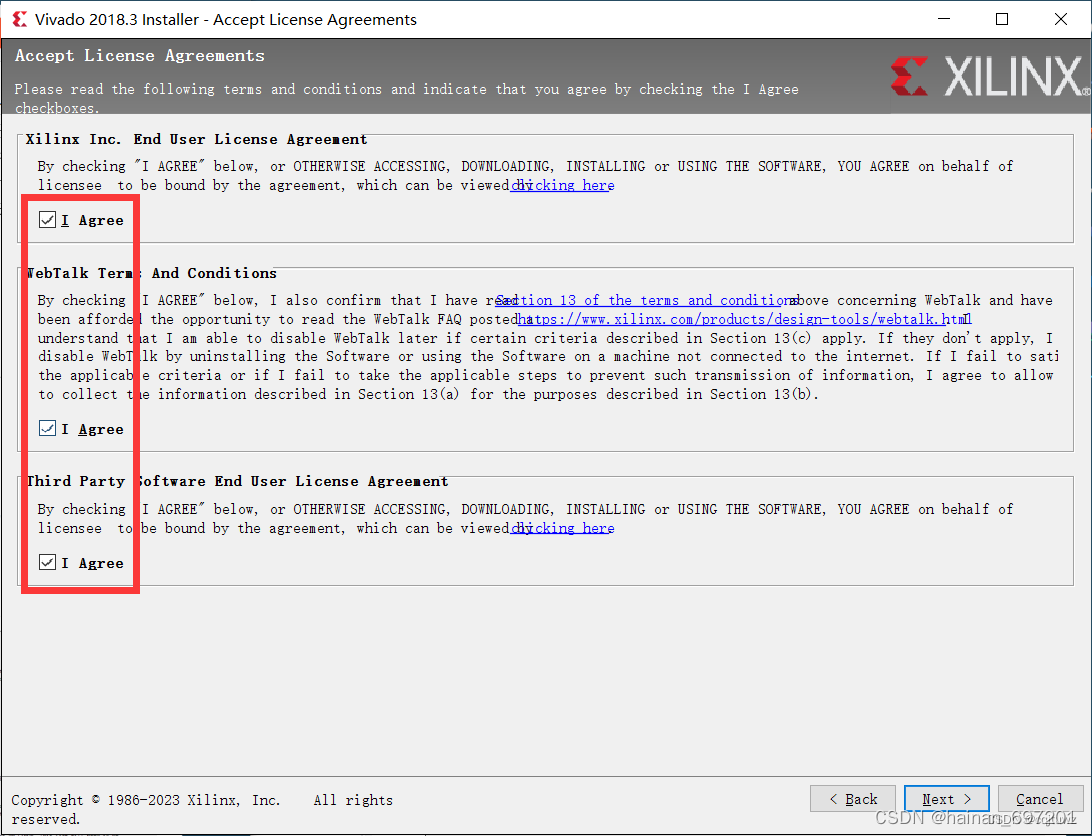

勾选同意所有协议并点击next:

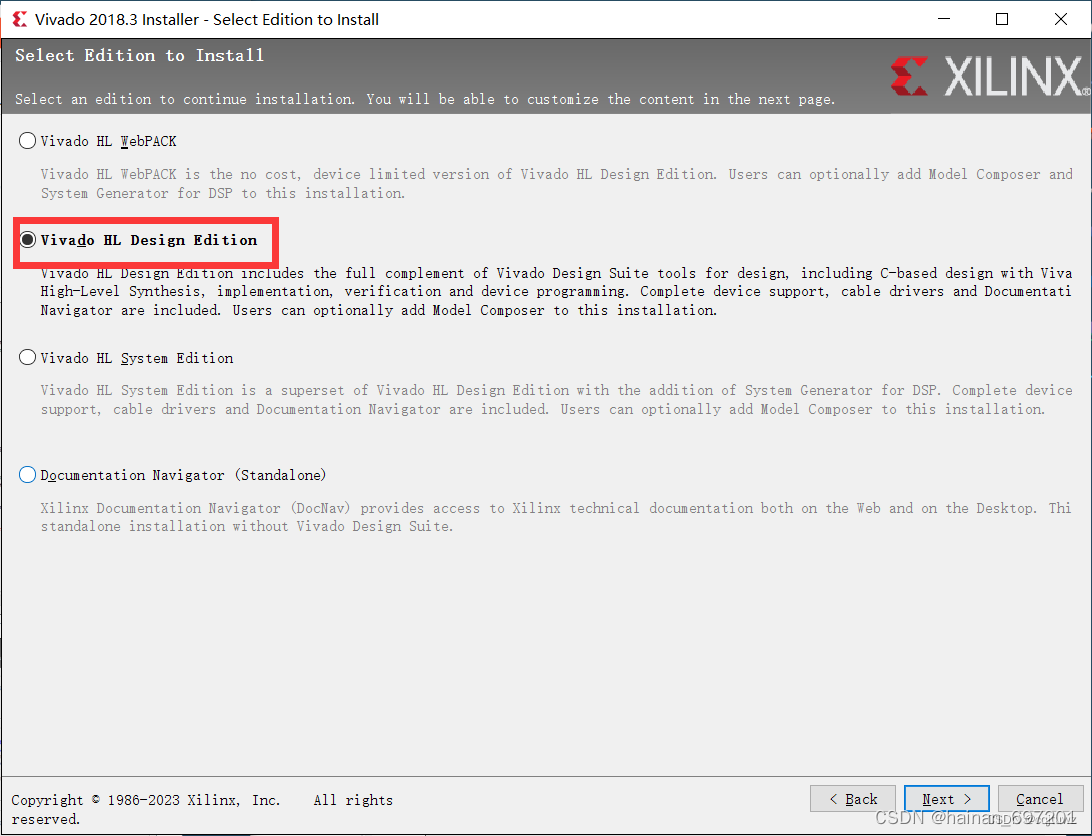

勾选Vivado HL Design Edition后点击next:

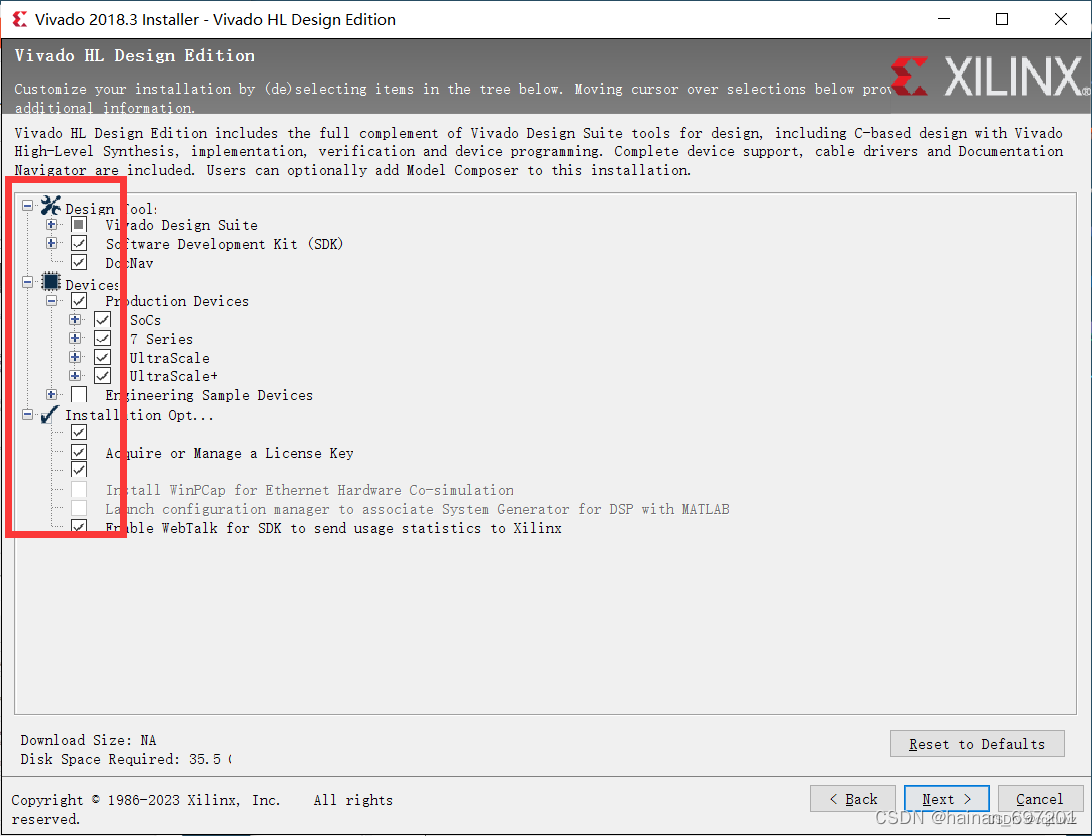

检查配置是否与下面相同,默认情况就是下图中所示。而后点击next:

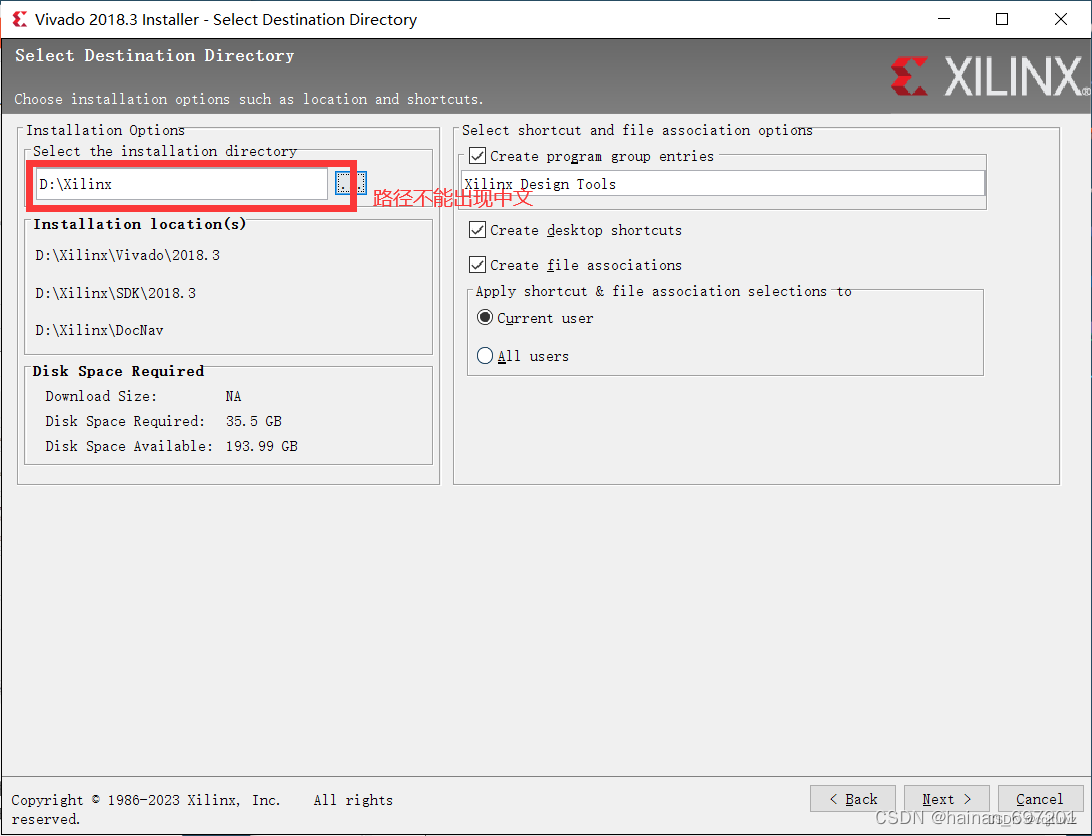

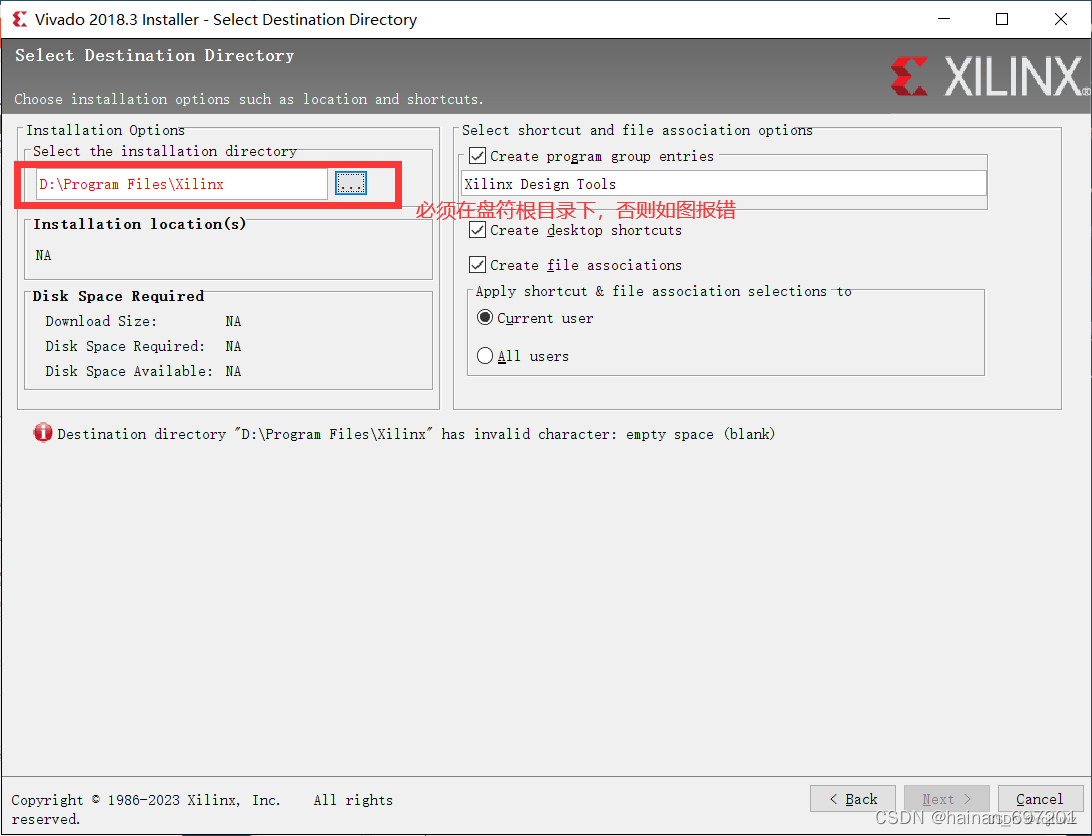

选择安装目录,注意安装目录路径不能包含中文且必须选择在根目录下的文件夹:

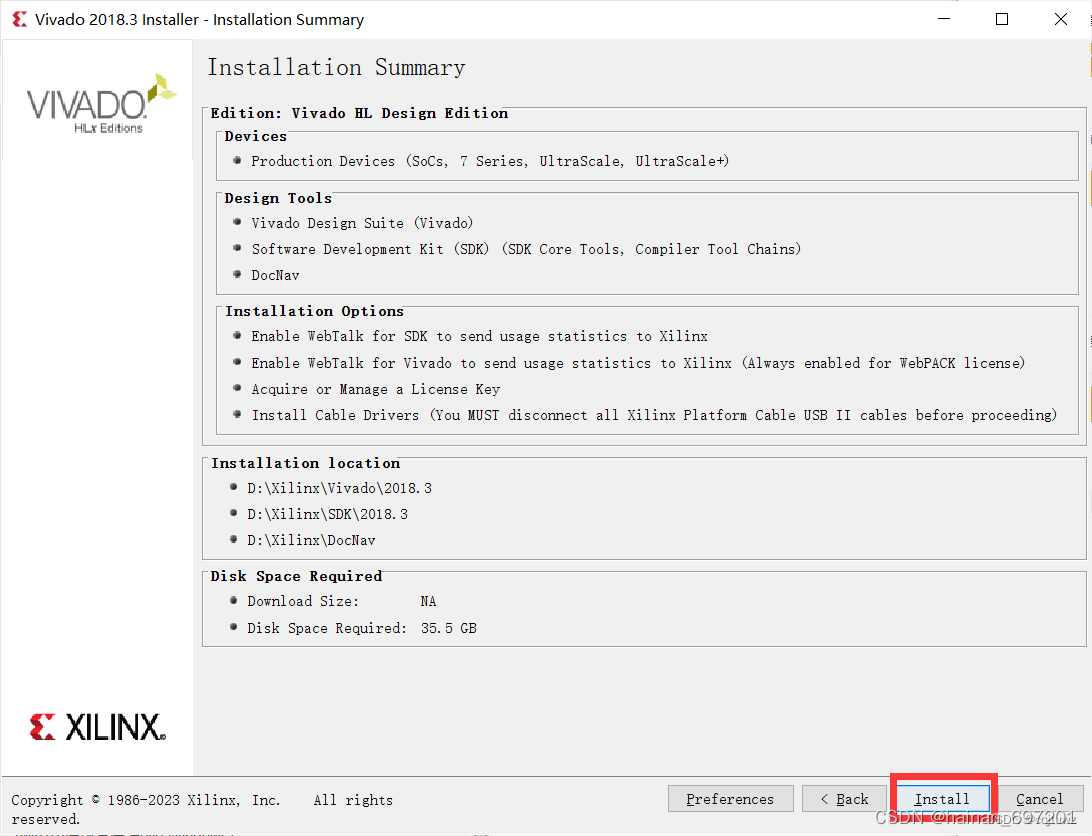

点击install开始安装:

安装完成图示如下:

许可证获取:

许可证资源下载: 许可证资源下载

网盘提取码:vh3h

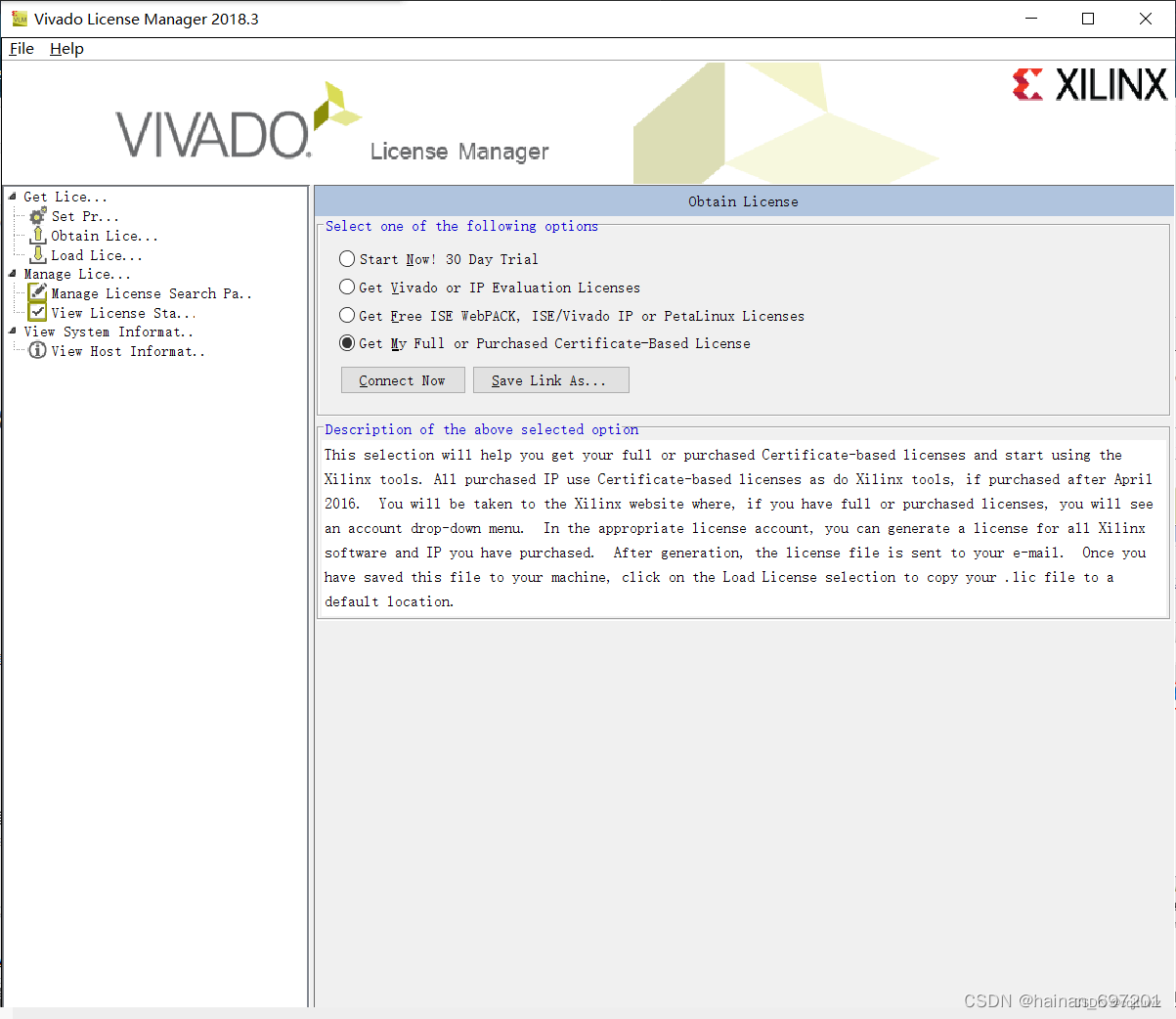

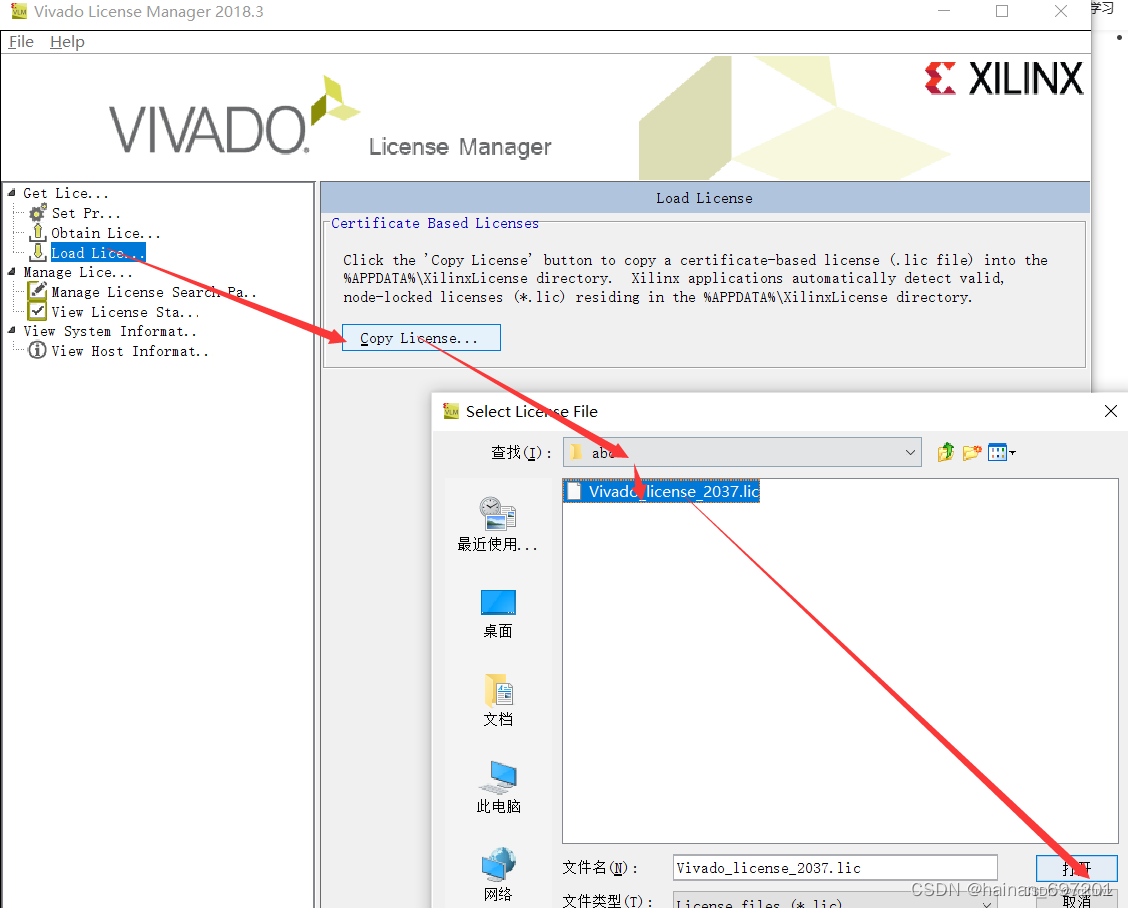

添加license:

出现以下提示说明添加lisence成功,点击确认,并关掉license Manager 窗口即可:

三、利用Vivado创建HLS——点亮LED灯

创建HLS工程:

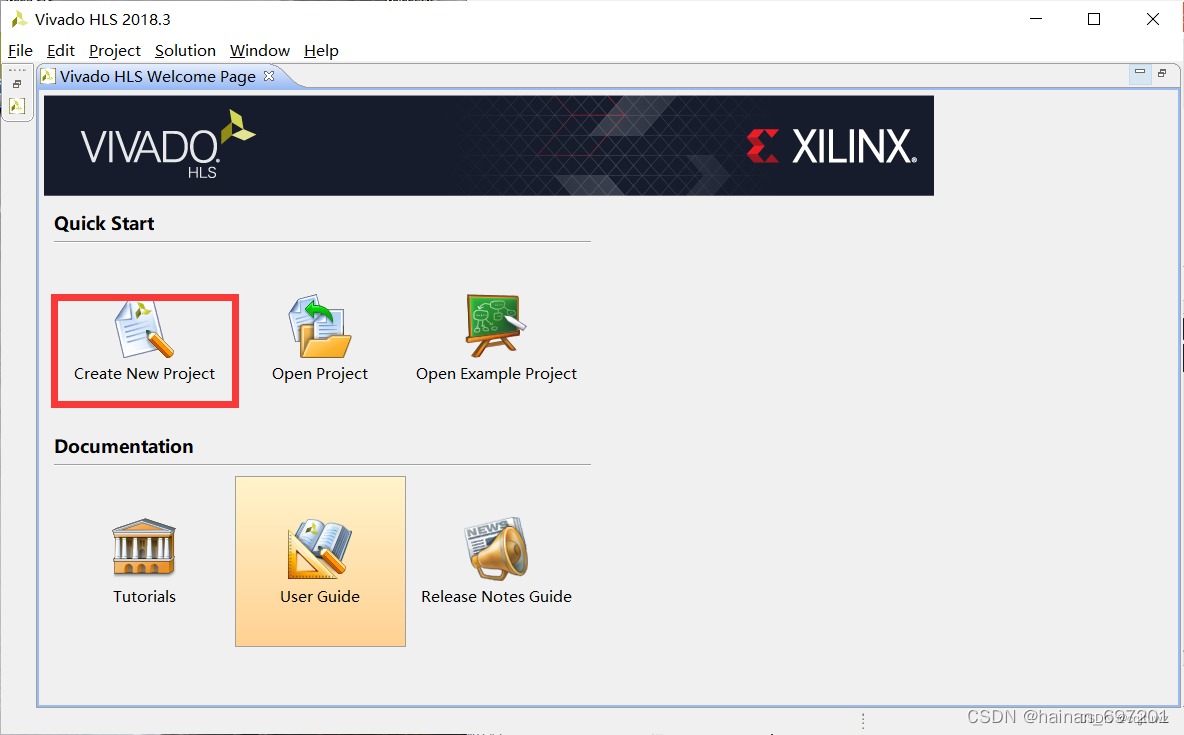

打开Vivado HLS 2018.3后,点击create new project进行新HLS工程的创建:

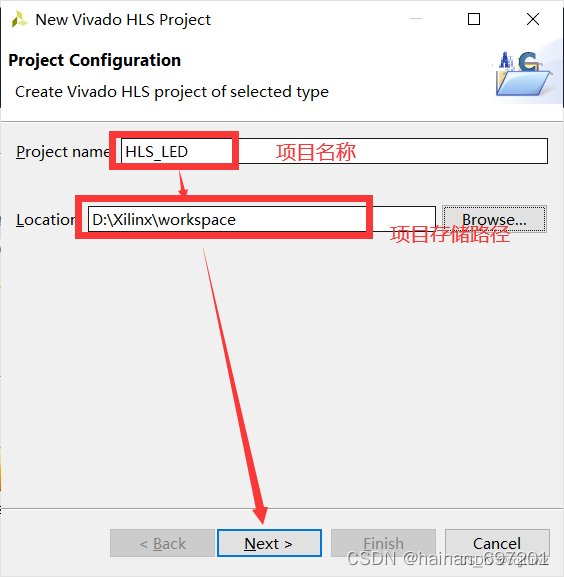

输入新工程的名称和工作空间:

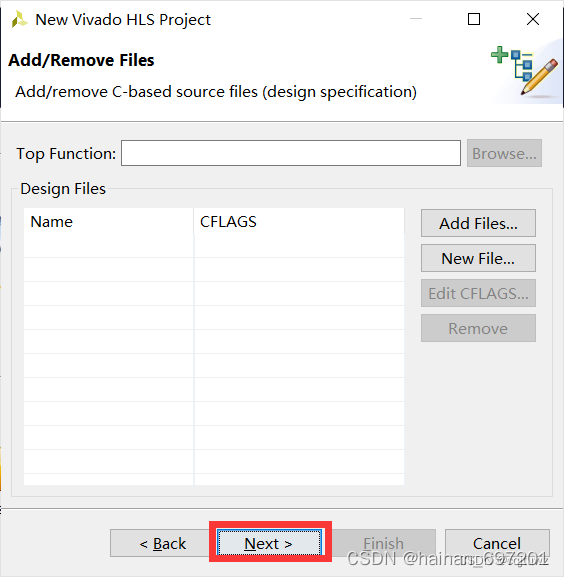

在之后出现的以下窗口点击next继续下一步即可:

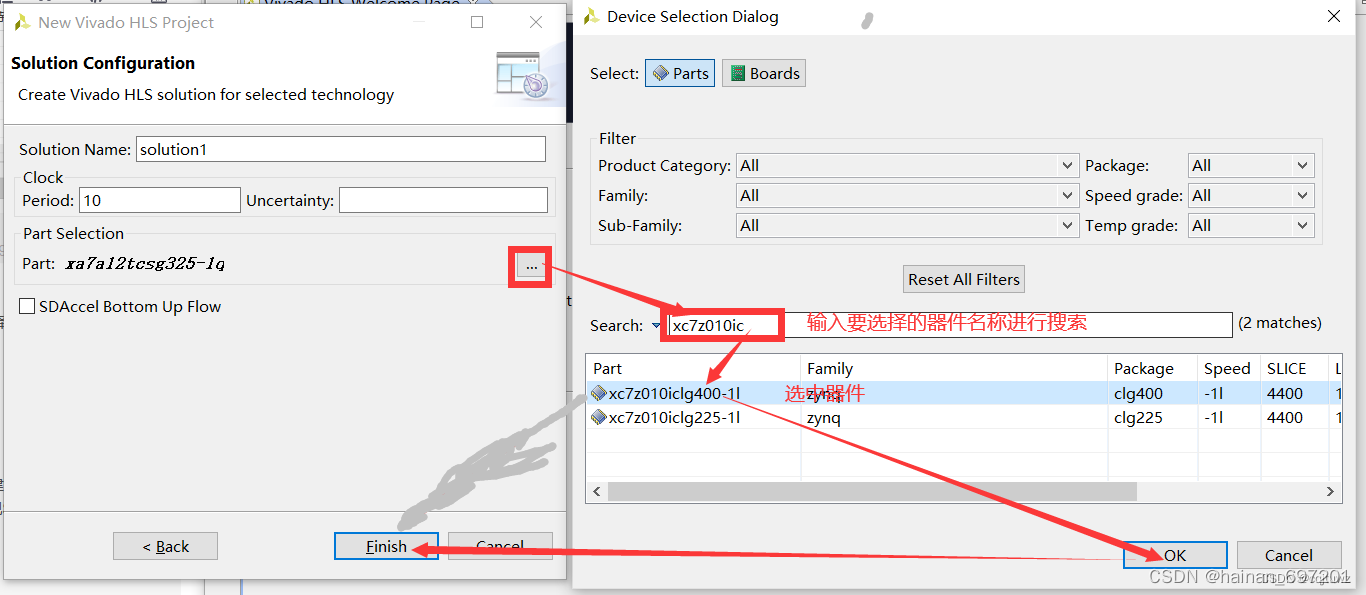

到下图所示界面时,需要进行器件的选择:

工程编写:

添加工程文件并编写代码

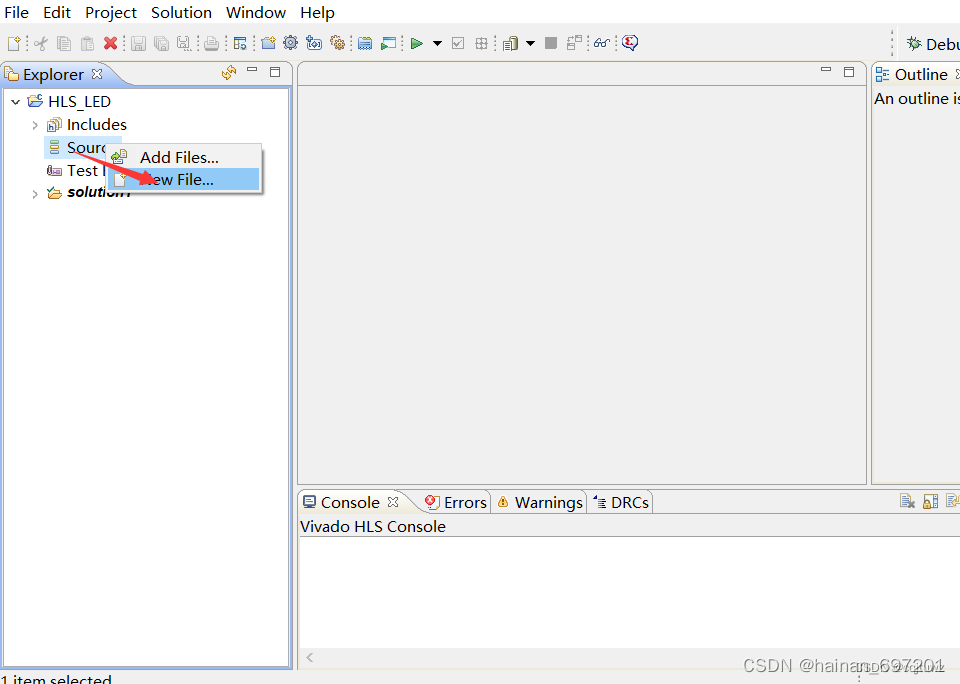

添加.h头文件:

编写.h头文件(led.h):

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

同样的方法添加led.cpp文件并编写以下内容:

#include

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4014

4014

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?