1:在Verilog中数据类型有variable和net两种,且都为四值逻辑。在SV中,它对经典的variable类型中的reg类型进行了改动,使得它除了作为一个变量以外,还可以被连续赋值、门单元和模块所驱动。这种改进的数据类型称为logic(logic可以看做是reg的增强,可以出现在initial、assign和always中,因此使用logic可不考虑是用reg还是wire,又节省时间,避免了出错的可能),但是要求不能有多个结构性的驱动。

2:在SV中定义了数据类型有两种属性,其一就是type:表明是variable(变量类型)类型或net(线网类型)类型,其二是data type 表明是四值逻辑还是二值逻辑。需要注意的是,variable可能是四值逻辑也可能是二值逻辑,而net类型只能是四值逻辑。

3:数据类型小总结

| 四值逻辑 | reg | integer | logic | net-type | |

| 二值逻辑 | byte(8bit) | shortint(16bit) | int(32bit) | longint(64bit) | bit |

| 有符号类型 | byte | shortint | int | longint | interger |

| 无符号类型 | bit | reg | logic | net-type |

思考:为什么在SV中要引入Verilog中没有的二值逻辑?

为了使验证激励只为0 or 1,二值逻辑可以节省内存空间,并且可以加快仿真速度。

-----------------------------------------------------------------------------------------------------------------------

练习:

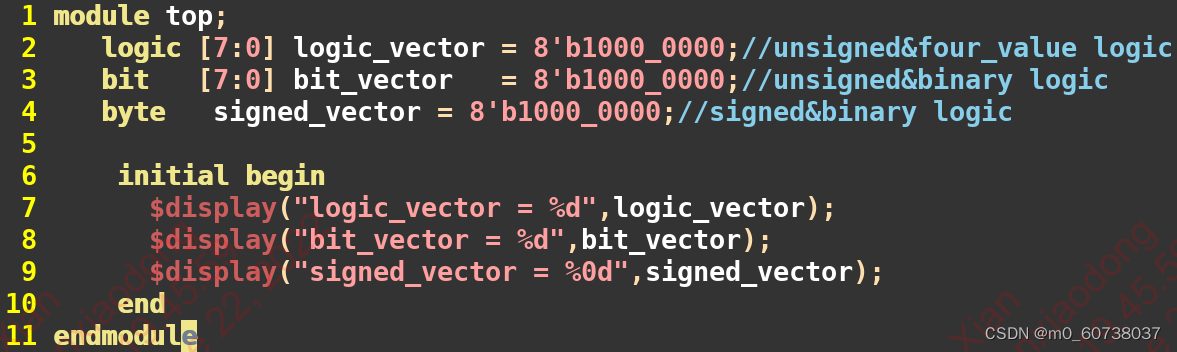

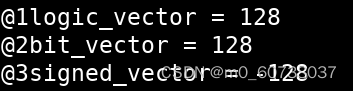

1、有符号&无符号变量的符号位问题

:

:

结论:无符号变量正常赋值,而有符号变量会根据最高位,若最高位为0则与无符号变量一致,若为高位为1则取反加一添负号。

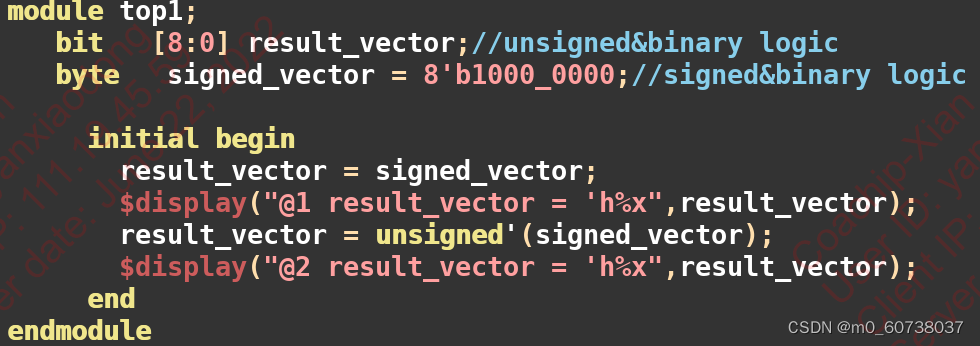

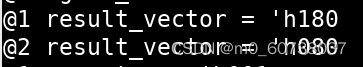

2、有符号变量与无符号变量混用(相互赋值操作)

结论:1、将有符号变量赋值为无符号变量时,打印时会将符号位体现出来‘h180 的1 即是符号位。

2、unsigned’ 函数可以将有符号变量转换为无符号变量。因此singned_vector此时为128.所以赋值后最高位的符号位为0.

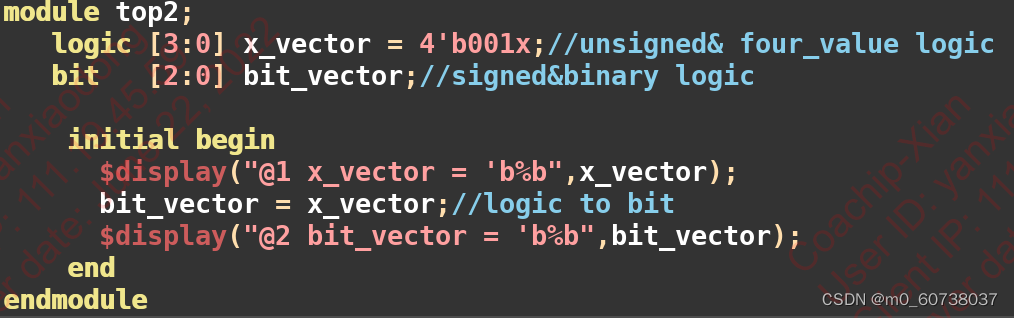

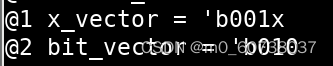

3、四值逻辑(logic)与二值逻辑(bit)进行运算时位宽不一致时

结论:当四值逻辑赋值给二值逻辑时,X,Z态会变成二值逻辑的默认态也就是0,而在当位宽不一致时会舍弃掉最高位。

因此:在不同数据类型进行操作时应该注意

逻辑数值类型 符号类型 变量位宽

tips 1、verilog赋值 reg[7:0] data; data = 8'b1111_1111; 给变量赋值全1

2、sv中 logic[7:0] data; data = '1 即可赋值全一,即所有bit都设置为1.(进制的省略默认为二进制)

3、四值逻辑默认值X,二值逻辑默认值0.

初学者,有不对的地方希望大家批评指正。

187

187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?