目录

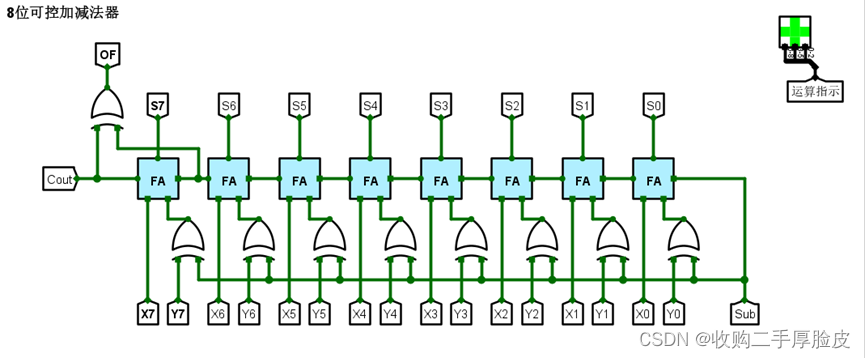

第一部分 实验分析与设计一、实验目的帮助学生掌握一位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑,熟悉 Logisim 平台基本功能,能在 logisim 中实现多位可控加减法电路。 帮助学生掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器,能分析对应电路的时间延迟。 帮助学生掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器,能分析对应电路的时间延迟。 二、实验原理逻辑电路 三、主要仪器设备及耗材PC,logisim平台 第二部分 实验调试与结果分析1.8位可控加减法电路设计

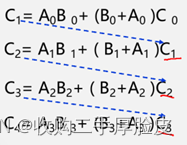

全加器实际上是三个数字进行相加,本该相加的两位与后一位向这一位的进位,输出有两位,本题目中的全加器上方是这一位的值,左侧的一位是它的进位。 数据与1异或的值是对其取反,与0异或是它原本的值 计算公式如下: [X+Y ]补=X补+Y补=X补+Y补⊕0+0 [X-Y]补= X补+[[Y]补]反+1 =X补+Y补⊕1+1 利用好Sub位,就可以根据公式把这个电路图连出来。 2.CLA182四位先行进位电路设计四位先行进位电路的原理如下:

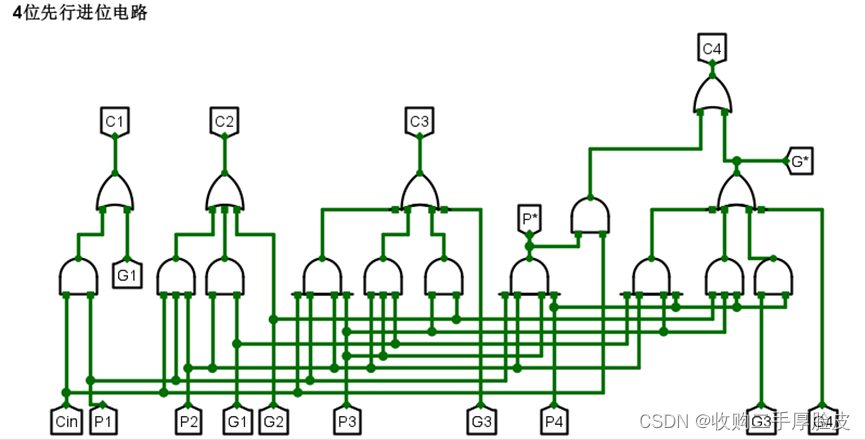

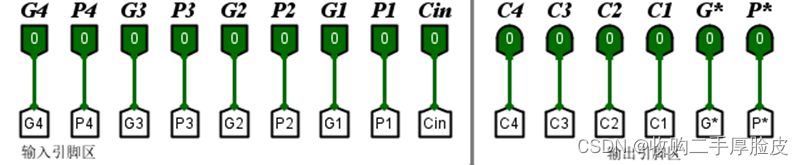

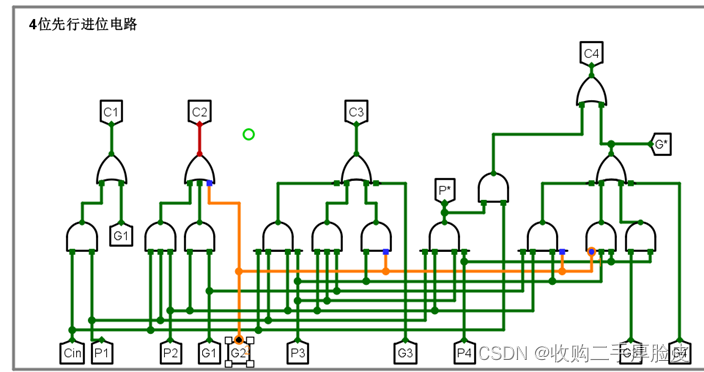

Ci+1 =AiBi +(Ai⊕Bi )Ci 其中:Gi+1 =AiBi 进位产生函数 Pi+1 =Ai⊕Bi 进位传递函数 ∴进位表达式Ci+1 =Gi+1 +Pi+1Ci C1 =G1 +P1C0 C2 =G2 +P2C1 =G2 +P2G1 +P2P1C0 C3 =G3 +P3C2 =G3 +P3G2 +P3P2G1 +P3P2P1C0 C4 =G4 +P4C3 =G4 +P4G3 +P4P3G2 +P4P3P2G1 +P4P3P2P1C0 根据上述公式连接电路即可,“+”使用“或门”,相连接的隧道用“与门”

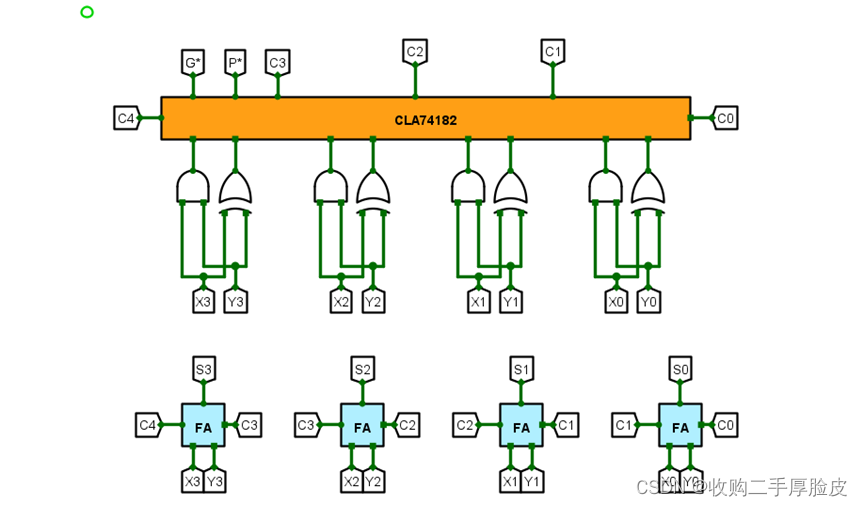

3.4位快速加法器设计4位快速加法器:“CLA部件”和“求和部件”构成。对上一实验中的电路进行封装,就是CLA块,负责进位,“求和部件”则由全加器进行计算,这里不需要如“8位可控加减法器”依靠低位向高位传递进位值,再进行计算,直接借助CLA模块进行求进位,在全加器中直接使用,这样可以节省去等待的时间,这也是它被称为“快速加法器”的原因。 对于CLA模块的使用要回到CLA的设计,输入参数有9位,P1-P4,G1-G4,以及Cin

其中:Gi+1 =AiBi 进位产生函数 Pi+1 =Ai⊕Bi 进位传递函数 将所需参数按上方公式进行连接即可

第三部分 实验小结、建议及体会本次第一个实验中,数据出错,线路中出现了红线,最终发现是短路的导线隐藏在使用的部件之后,删除部件重新连线即可。 在从同一引脚牵出的线路过多时,很容易连到其它地方的引脚,产生错误。这次第二个实验中,就是要反复地用一个隧道标签的值,很容易误连,在连接时,可以故意将部件的位宽设置成不一致,使其出现黄线,便于检错。在结束后,也可以将隧道标签地数据位宽设为其他值,出现“数据位宽”不一致的情况,使其报错,便于后续检查。

|

本文详细介绍了基于Logisim平台进行8位可控加减法电路、CLA182四位先行进位电路和4位快速加法器的设计过程。实验旨在让学生掌握全加器逻辑、先行进位原理,以及如何利用这些知识构建高效的加法器电路。在实验中,提到了一些常见的错误和解决方法,如线路短路和数据位宽的检查。

本文详细介绍了基于Logisim平台进行8位可控加减法电路、CLA182四位先行进位电路和4位快速加法器的设计过程。实验旨在让学生掌握全加器逻辑、先行进位原理,以及如何利用这些知识构建高效的加法器电路。在实验中,提到了一些常见的错误和解决方法,如线路短路和数据位宽的检查。

6002

6002

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?