实验目的

帮助学生掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器,能分析对应电路的时间延迟。

实验内容

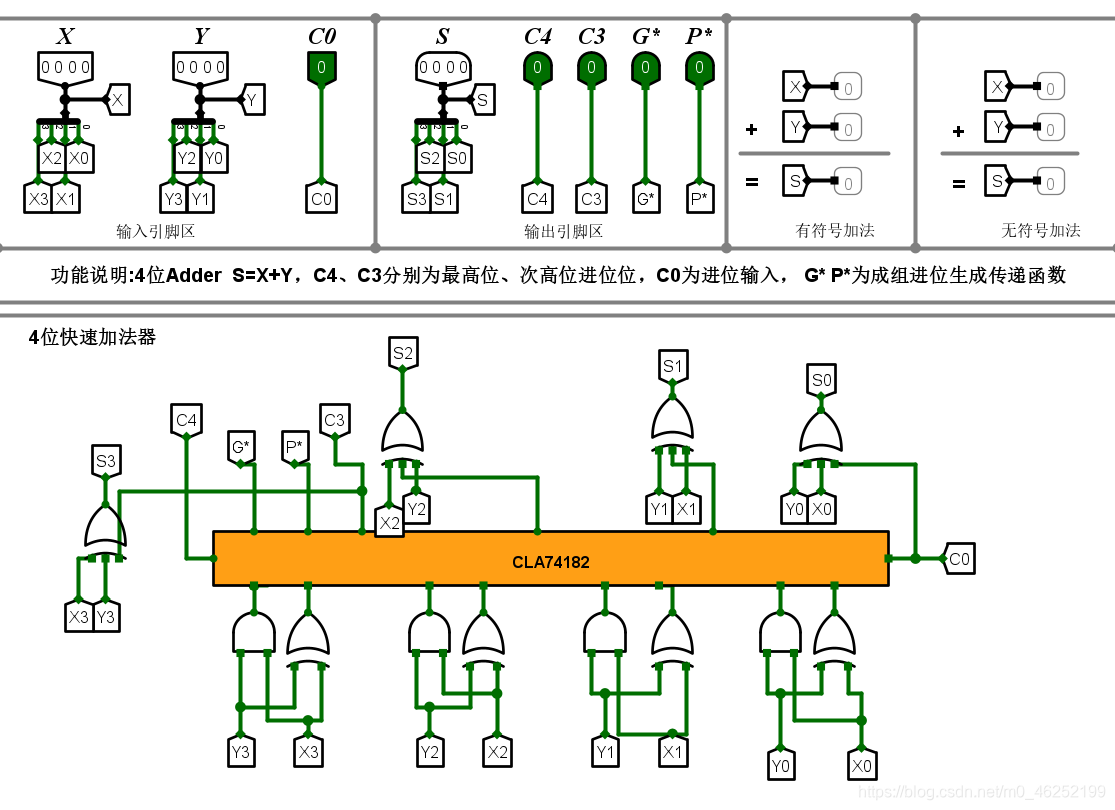

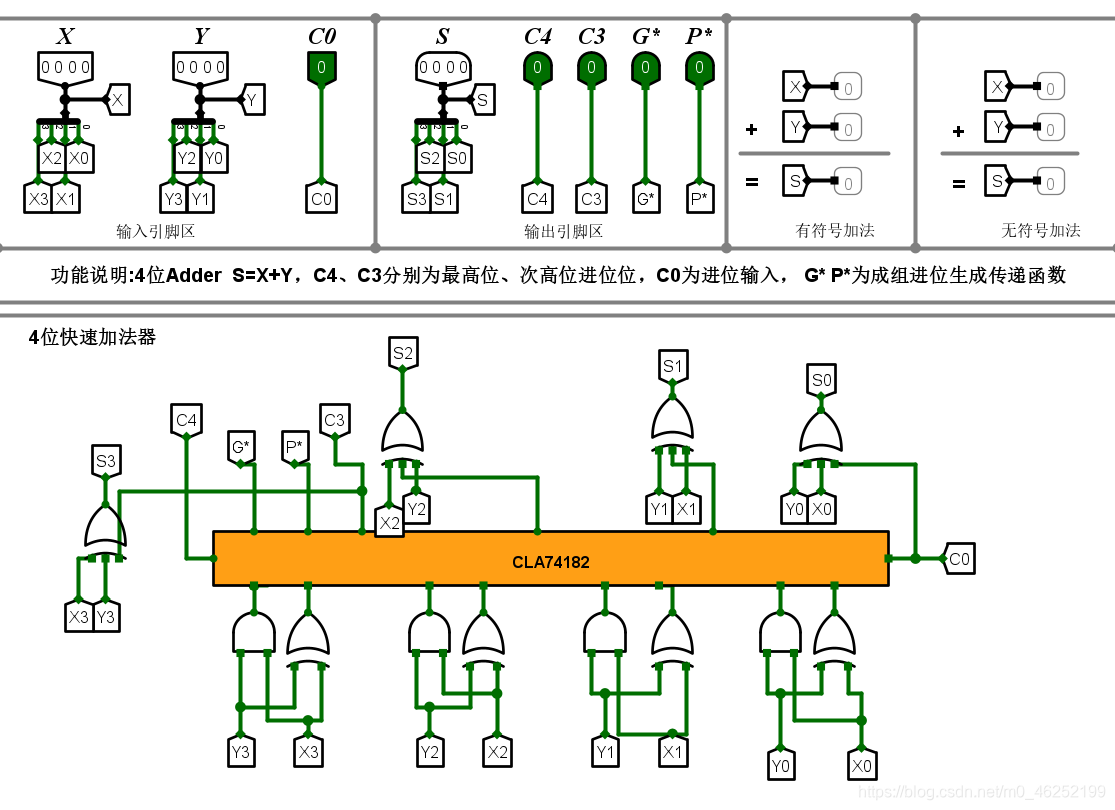

利用前一步设计好的四位先行进位电路构造四位快速加法器,其引脚定义如图所示,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

解答:

实验目的

帮助学生掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路,并利用设计的4位先行进位电路构造4位快速加法器,能分析对应电路的时间延迟。

实验内容

利用前一步设计好的四位先行进位电路构造四位快速加法器,其引脚定义如图所示,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

解答:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?