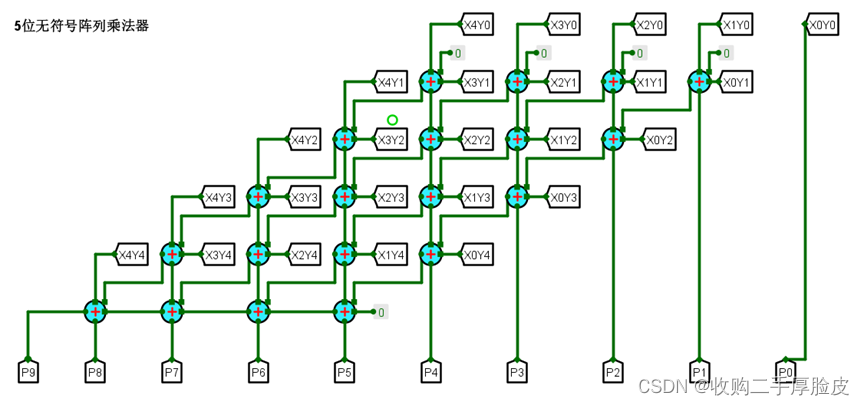

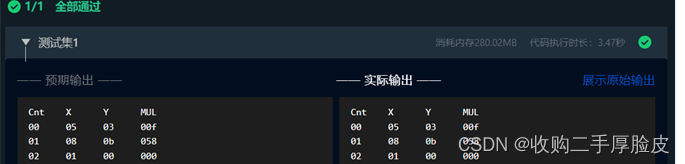

第一部分 实验分析与设计一、实验目的帮助学生掌握阵列乘法器的实现原理,能够分析阵列乘法器的性能,能在 Logisim 中绘制阵列乘法器电路。 学生掌握原码一位乘法运算的基本原理,熟练掌握 Logisim 寄存器电路的使用,能在 Logisim 平台中设计实现一个 8*8位的无符号数乘法器。 二、实验原理逻辑电路 三、主要仪器设备及耗材PC,logisim平台 第二部分 实验调试与结果分析1.5位阵列乘法器

这一个电路比较简单,就是比照平时列竖式计算乘法,将被乘数与乘数的每一位错位放置后,然后将位数进行相加,进位。因为这里运用了全加器,可以就三位数字进行相加,然后向后一位传递进位。 将所有数字用全加器连起来之后就可以计算出正确结果。

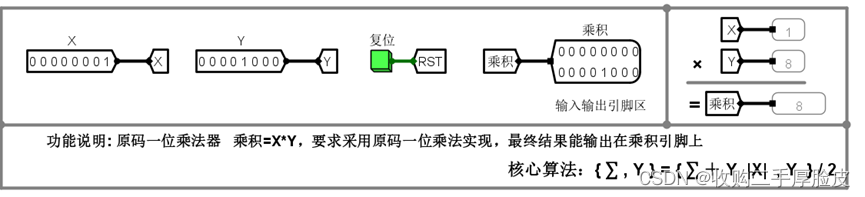

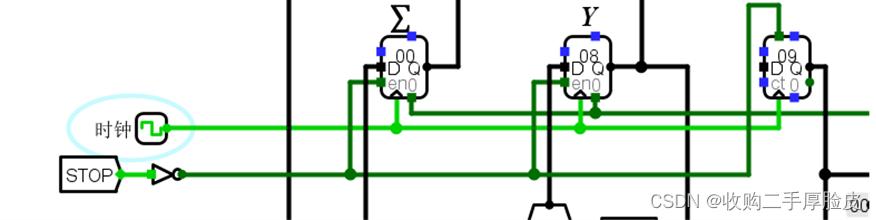

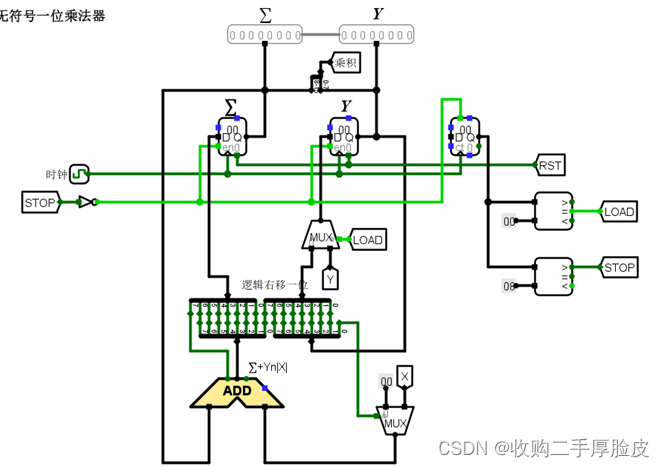

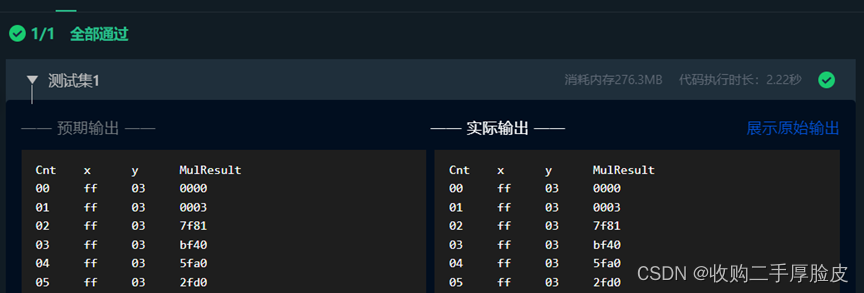

2.原码1位乘法器核心算法:{ ∑ , Y } = { ∑ + Y |X| , Y } / 2 这一实验模拟的过程是之前上计组理论课时所用到的计算乘法的方式,需要用到两个寄存器,将乘法拆解为加法与逻辑右移。每次将X与寄存器末尾值相乘,如果是0,则直接加0;如果是1,则加X,这一部分用多路选择器来完成。计算完当前位,将两个寄存器的值全向右移,这一部分用四个分线器来实现。 电路中需要用到寄存器与选择器,这两个器件的端口都比较多,将鼠标悬停在端口之上就可以查看该端口的作用,连接电路。 时钟对计算步数进行驱动,最初未计算时要将Y放入后一个寄存器中。用分线器读取最后一位,如果为0,全加器加0,如果为1,全加器加x,在4个分线器的区域,这里实现了数据右移,数据右移后,就是乘数的下一位与x进行计算,如此下去,知道全部计算完成就可以让寄存器和计数器不再接受时钟输入。

已经计算出了正确结果,此时时钟仍在连续,不过选择器根据做加法的次数判断出此时已完成计算,寄存器,寄存器与计数器的使能端为低电平不再接受时钟操作。

第三部分 实验小结、建议及体会原码1位乘法器采用时钟连续不断让乘法器进行相加、移位,再进行8次计算之后就可以停止时钟,不再运算,继续运算会得到错误结果,但是这里并没有对时钟本身进行操作,让时钟停止,这是因为对于时钟进行操作是一种比较危险的操作,所以用了一个计数器,对时钟进行计数,等到达到一定数字以后,使寄存器与计数器接受时钟的端口置为低电平,使其不再受时钟影响。 |

01-03

05-25

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?