努力是为了不平庸~

学习的最大理由是想摆脱平庸,早一天就多一份人生的精彩;迟一天就多一天平庸的困扰。

急的同学请直接点击目录跳到下方解答处!!

目录

实验目的

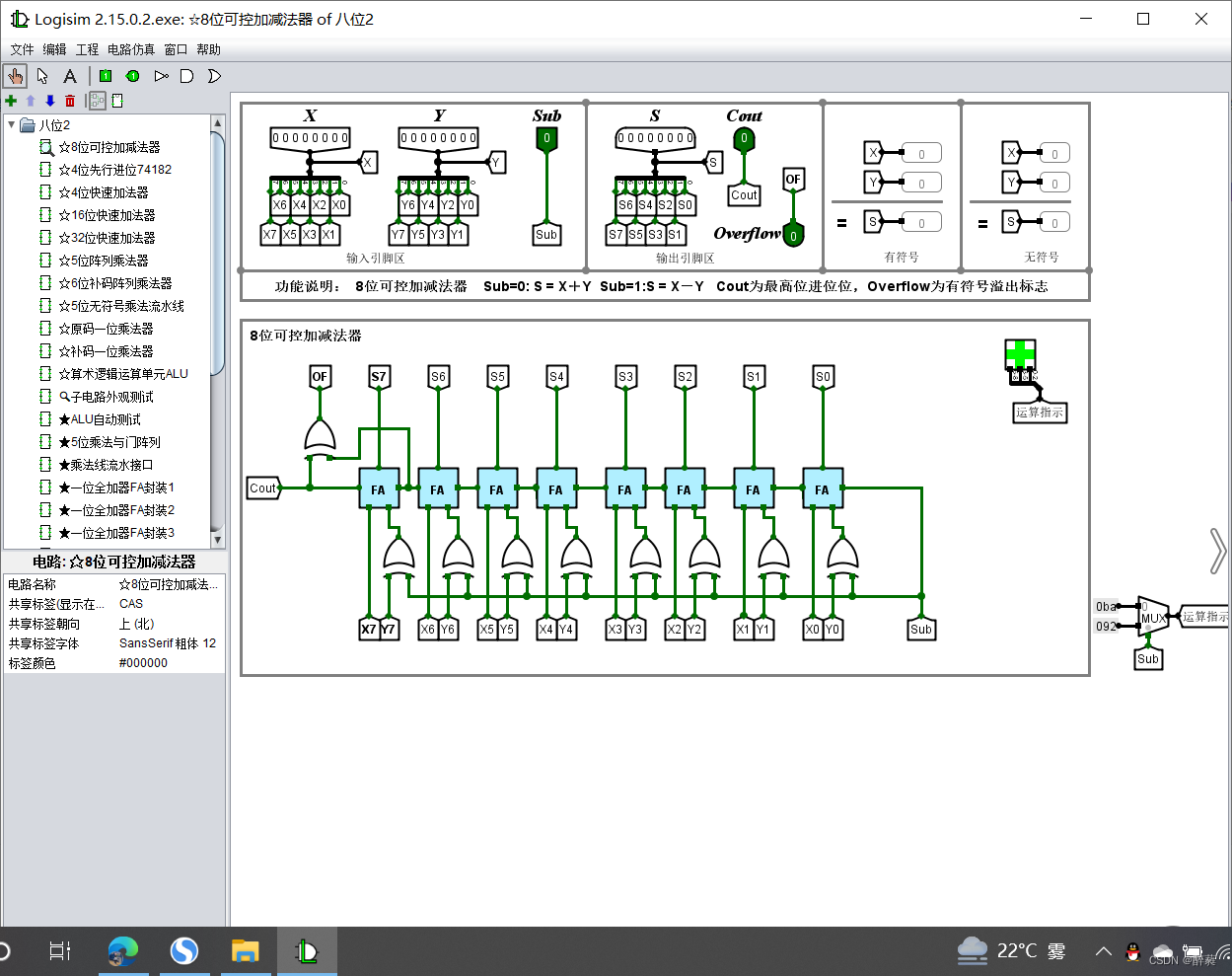

帮助学生掌握一位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑,熟悉 Logisim 平台基本功能,能在 logisim 中实现多位可控加减法电路。

实验内容

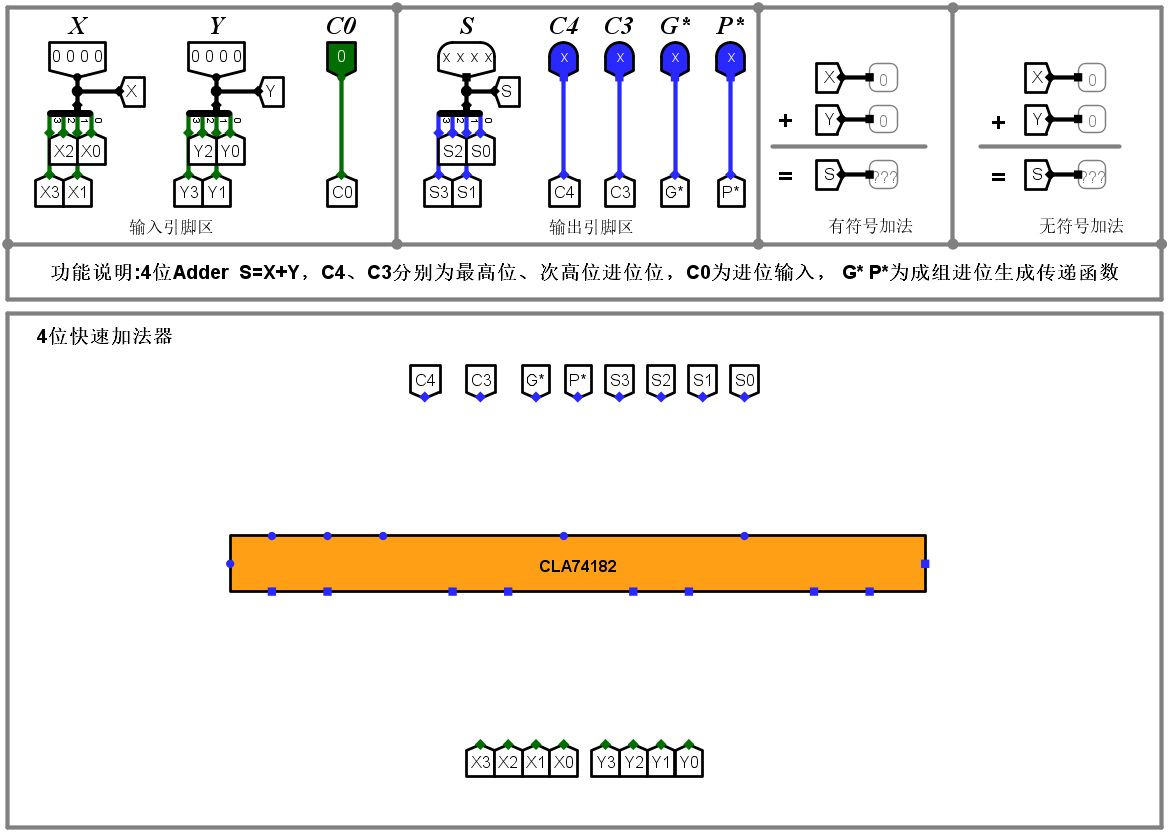

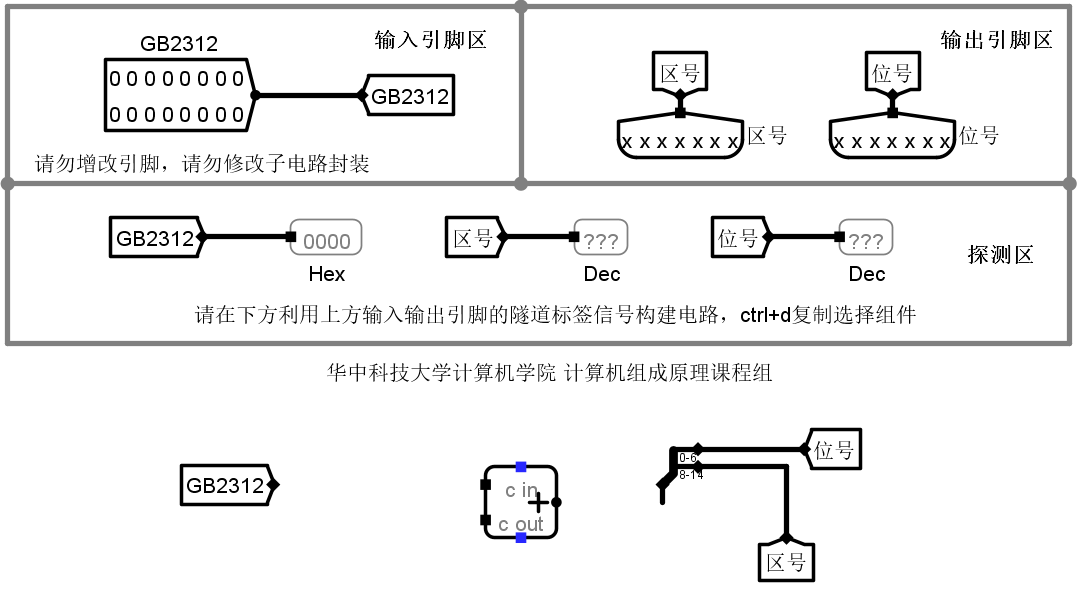

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。

电路框架

alu.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| X | 输入 | 8 位 | 加数/被减数 |

| Y | 输入 | 8 位 | 加数/减数 |

| Sub | 输入 | 1 位 | 运算控制位 1:减法 0:加法 |

| S | 输出 | 8 位 | 运算结果 和/差 |

| Cout | 输出 | 1 位 | 进位输出 |

| OF | 输出 | 1 位 | 有符号运算溢出检测位 |

电路测试

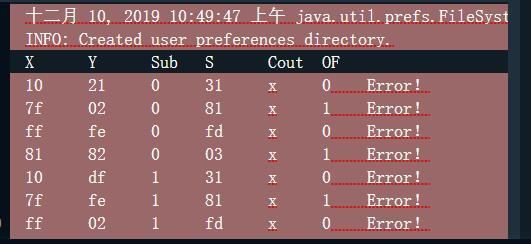

完成实验后,利用文本编辑工具打开 alu.circ 文件,将所有文字信息复制粘贴到 Educoder 平台的 alu.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

X Y Sub S Cout OF10 21 0 31 0 07f 02 0 81 0 1ff fe 0 fd 1 081 82 0 03 1 110 df 1 31 0 07f fe 1 81 0 1ff 02 1 fd 1 081 7e 1 03 1 1

常见问题

Cout 一直悬空,估计是没有接这个引脚。

解法:

图解:

代码题解(免费):

自己做的,立志打破积分下载垄断!代码有点长,上传资源了

3811

3811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?