第二关也通过啦!!

任务描述

本关任务:16 位先行进位加法器

实验目的

1、组间先行进位设计

2、CLU和CLA级联应用

实验原理

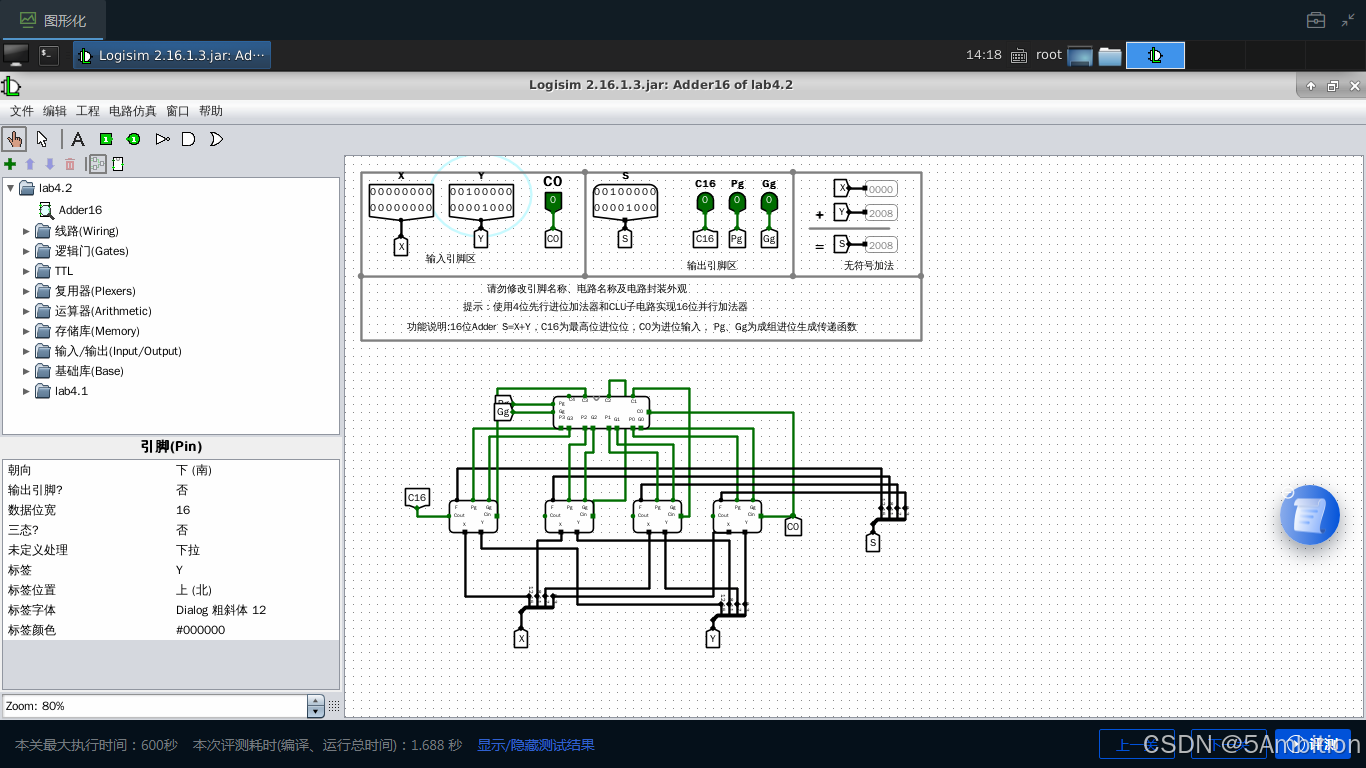

对于一个16位加法器,可以分成4组,每组用一个4位先行进位加法器CLA实现。下图是一个由4个4位先行进位加法器CLA与一个组间先行进位部件CLU构成的16位两级先行进位加法器原理图。

编程要求

在Logisim中打开文件/data/workspace/myshixun/lab4.2.circ,设计并实现16位先行进位加法器。

打开Logisim,在Project菜单下,加载lab4.1的电路源文件为库文件,如果已经加载lab4.1库文件则跳过该操作。

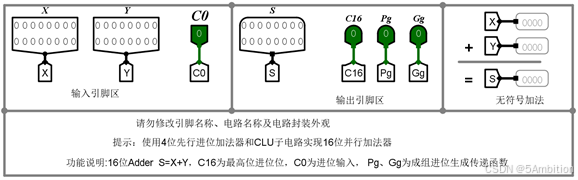

在Logisim工作区中按下图布局图所示,定义输入输出引脚和组件布局,其中包含输入输出引脚、隧道、4个4位快速加法器子电路、1个4位先行进位部件子电路、逻辑门电路等组件。参照电路原理图,连接组件,实现电路。通过设置不同的X、Y和Cin的输入值,观察结果F、进位Cout等输出值,以验证电路的正确性,记录测试数据。

测试说明

请不要更改电路封装、修改引脚、移动引脚、添加引脚,否则评测将出错。

平台会对你编写的代码进行测试:

X、Y、Cin表示输入的数据,分别表示被加数、加数和低位进位;S、Cout、Gg、Pg表示输出数据,分别表示和、进位、组间进位生成信号和组间进位传递信号。

测试数据:

Cnt X Y Cin S Cout Gg Pg

00 ffff 0002 0 0001 1 1 1

01 fffe 0003 0 0001 1 1 1

02 fffd 0004 0 0001 1 1 0

03 fffc 0005 0 0001 1 1 0

04 fffb 0006 0 0001 1 1 1

05 fffa 0007 0 0001 1 1 1

06 fff9 0008 0 0001 1 1 0

07 fff8 0009 0 0001 1 1 0

开始你的任务吧,祝你成功!

接下来就是展示电路连接了!!

850

850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?