不知道大家有没有想过,世界上有那么多种指令,为什么要把指令的长度设计成一样的,正所谓“君子和而不同”,大家都是为计算机服务的,干嘛要把指令的长度设计的一模一样?诶嘿,今天我们就要学习一类“君子”计算机,这类计算机称为复杂指令系统计算机CISC。而我们之前学习的指令长度固定且种类较少的计算机是精简指令系统计算机RISC。请跟随小编的步伐,一起出发学习吧!

目录

一、CISC与RISC

考点1:复杂指令系统计算机CISC与精简指令系统计算机RISC

1、CISC

主要特点:

①指令系统复杂庞大,指令数目一般为200条以上。

②指令的长度不固定,指令格式多,寻址方式多。(君子和而不同)

③可以访存的指令不受限制。

④各种指令使用频率相差很大。(大概只有20%的比较简单的指令会反复使用,约占整个程序的80%,而80%的指令则很少使用,约占整个程序的20%)

⑤各种指令执行时间差很大。

⑥控制器大多数采用微程序控制,而难以采用硬连线控制

⑦难以用优化编译生成高效的目标代码程序。

如此庞大的指令系统,对指令的设计提出了极高的要求,研究周期变得很长。后来,人们发现,一味地追求指令系统的复杂和完备程度不是提高计算机性能的唯一途径,RISC应运而生。

2、RISC

RISC的思想是要求指令精简化,指令格式力求一致,小编当时学计算机组成与设计时,那本黑皮书教材的名字就叫做RISC-V,长得跟一本魔法书一样,反正里面的文章对当时的小编来说就是天书。

其特点为:

①选取使用频率最高的一些简单指令,复杂指令的功能由简单指令的组合来实现。

②指令长度固定,指令格式种类少,寻址方式种类少

③只有Load/Store指令方寸,其余指令的操作都在寄存器之间进行

④CPU中通用寄存器的数量相当多

⑤RISC一定采用指令流水线技术,大部分指令在一个时钟周期内完成

⑥以硬布线控制为主,不用或少用微程序控制

⑦特别重视编译优化工作,以减少程序执行的时间

例题:下列描述中,不符合RISC指令系统特点的是():

A.指令长度固定,指令种类少

B.寻址方式种类尽量减少,指令功能尽可能强

C.增加寄存器的树木,以尽量减少访存次数

D.选取使用频率最高的一些简单指令,以及很有用但不复杂的指令

【答案】:B

【解析】:RISC的功能性很弱,由很多条简单指令完成复杂的一些操作。就比如人的走路行为,CISC中该指令可能就是“走路”,而RISC则会把这个指令拆成“抬左腿”,“向前迈一步”,“抬右腿”,“向前迈一步”……

考点2:CISC与RISC的对比

没有对比就没有伤害,我们自然而然的想将CISC与RISC浅浅的对比一下,找找不同,毕竟这该死的出题人就是喜欢移花接木,不捋清楚二者差异,很难的做题。

| CISC | RISC | |

| 指令系统 | 复杂,庞大 | 简单,精简 |

| 指令数目 | 一般大于200条 | 一般小于100条 |

| 指令字长 | 不固定 | 固定 |

| 可访存指令 | 不加限制 | 只有Load/Store指令 |

| 各种指令执行时间 | 相差较大 | 绝大多数在一个周期完成 |

| 各种指令使用频率 | 相差较大 | 都比较常用 |

| 通用寄存器数量 | 少 | 多 |

| 目标代码 | 难以用优化编译 | 采用优化编译 |

| 控制方式 | 绝大多数微程序控制 | 绝大多数组合逻辑控制 |

| 指令流水线 | 可以采用 | 必须采用 |

例题:下列关于RISC的说法中,正确的是()

A.RISC普遍采用微程序控制器

B.为了实现兼容,新设计的RISC是从原来CISC系统的指令系统中挑选一部分实现

C.RISC的指令数、寻址方式和指令格式的种类相对CISC少

D.CISC只有Load与Store指令能够访存

【答案】:C

【解析】:A项,RISC普遍采用组合逻辑控制(硬布线),不用或少用微程序控制;B项,RISC不可能兼容CISC;D项,RISC只有Load与Store指令能够访存

二、指令执行过程

考点4:指令周期

1、指令周期

刚刚我们谈论到,CISC与RISC有很多差别,比如说硬布线、微程序还有指令流水线、指令执行用时的差别。很显然,仅仅用一篇文章并不能把每一个差别背后的原理都说清楚,下面的篇幅里小编打算讲讲指令执行周期。

首先,我们知道CISC系统指令执行的时间相差较大,而RISC系统指令绝大多数能在“一个周期”内完成。这里的周期,指的是什么周期?CPU中又有哪几种容易搞混的周期?

| 指令周期 | CPU从主存取出并执行一条指令的时间称为指令周期 |

| 机器周期 | 通过一次总线事务访问一次主存或I/O的时间称为一个机器周期 |

| 存取周期 | 连续启动两次独立的读/写操作所需的最短时间称为存取周期 |

指令周期通常用若干机器周期来表示,一个机器周期又包含了若干时钟周期(也称为节拍或T周期,它是CPU操作的最基本单位)。一个完整的指令周期包括取指令周期、间址周期、执行周期还有中断周期这四个机器周期。而每个指令周期内的机器周期数可以不等,每个机器周期内的节拍数也可以不等。

例如无条件转移指令,在执行时不需要访问主存,只包含取指阶段和执行阶段,所以指令周期包括取址周期和执行周期。但是对于间接寻址的指令,为了取操作数,需要先访问一次主存,取出有效地址,然后访问主存,取出操作数,所以还包括间址周期。这两条指令的指令周期的机器周期数就不相等。而显然取指令与读写存储器所用的时长不同,故每个机器周期内的节拍数可以不相等!

这四个工作周期都有CPU访存操作,只是访存的目的不尽相同。取指周期是为了取指令,间址周期是为了取有效地址,执行周期是为了取操作数,中断周期是为了保存程序断点。

大家还需要注意一个点,这是一个有关语文错别字的点,指,址,值三个字千万别写错了!

例题:以下有关机器周期的说法中,错误的是():

A.通常把通过一次总线事务访问一次主存或I/O的时间定为一个机器周期

B.一个指令周期通常包含多个机器周期

C.不同的指令周期所包含的机器周期数可能不同

D.每个指令周期都包含一个中断响应的机器周期

【答案】:D

【解析】:A,B,C都通过上文能找到出处。D选项,只有在出现中断请求时,才会进入中断周期。

考点5:指令周期的数据流

2、各个周期的数据“动向”

数据流是根据指令要求依次访问的数据序列。在指令执行的不同阶段,要求一次访问的数据序列是不同的。而且对于不同的指令,它们的数据流往往也是不同的。

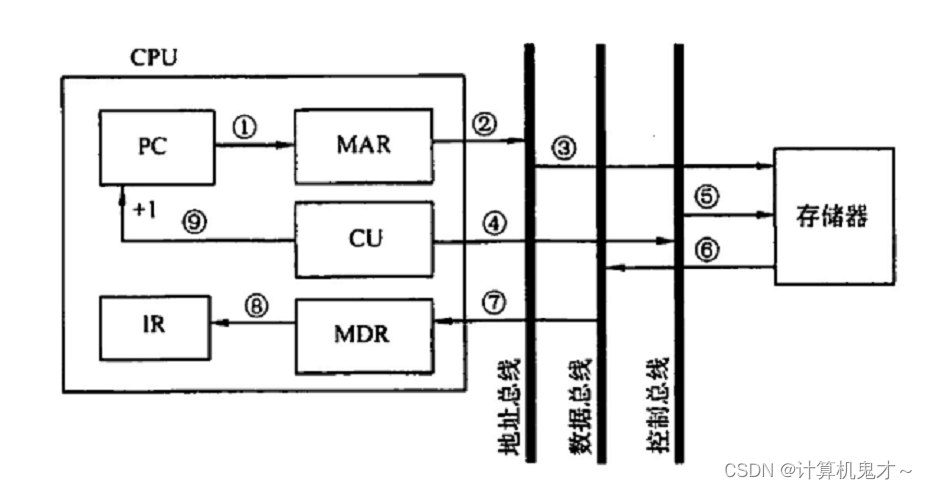

①取指周期

任务:根据PC中的内容从主存中取出指令代码并存放在IR中

步骤:

1)PC----->MAR----->地址总线----->主存

2)CU发出读命令----->控制总线----->主存

3)主存----->数据总线----->MDR----->IR(存放指令)

4)CU发出控制信号----->PC内容加1

【首先从PC中读出指令的地址,然后把这个地址放到存储器地址寄存器MAR中,经过地址总线从主存中找到这个地址,经过CU的读命令之后,取出该地址的指令,并且放到MDR中,以及IR中】

例题:在取指操作后,程序计数器中存放的是()

A.当前指令的地址

B.程序中指令的数量

C.已执行的指令数量

D.下一条指令的地址

【答案】:D

【解析】:取指周期的第四步,PC会自增,所以存放的是下一条指令的地址

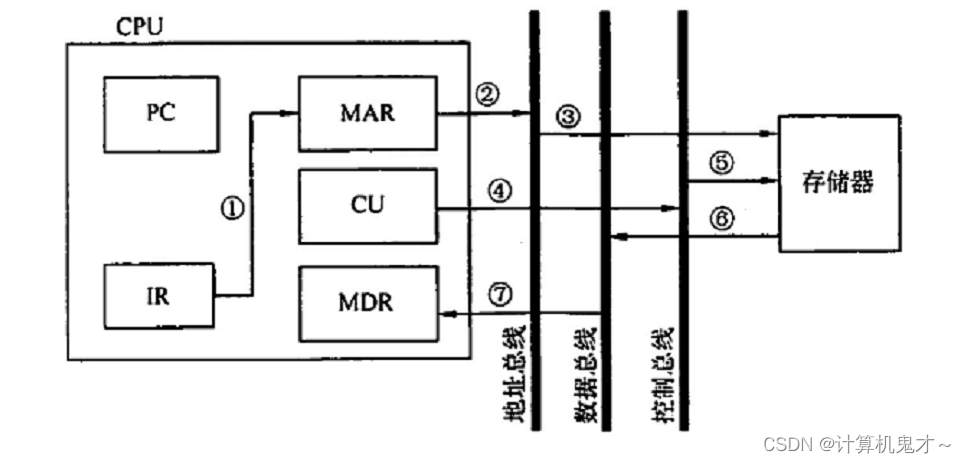

②间址周期

任务:取操作数有效地址

步骤:(以一次间址为例)

1)Ad(IR)或MDR----->MAR----->地址总线----->主存

2)CU发出读命令----->控制总线----->主存

3)主存----->数据总线----->MDR(存放有效地址)

其中Ad(IR)代表取出IR中存放的指令字的地址字段

例题:间址周期结束时,CPU内寄存器MDR中的内容为()

A.指令

B.操作数地址

C.操作数

D.无法确定

【答案】:B

【解析】:间址周期的任务是取操作数的有效地址,而最后一部把它放到了MDR里面

③执行周期

任务:取操作数,并根据IR中的指令字的操作码通过ALU操作产生指令结果

步骤:没有统一的步骤(加的步骤肯定和乘法的步骤不尽相同,所以根本统一不了)

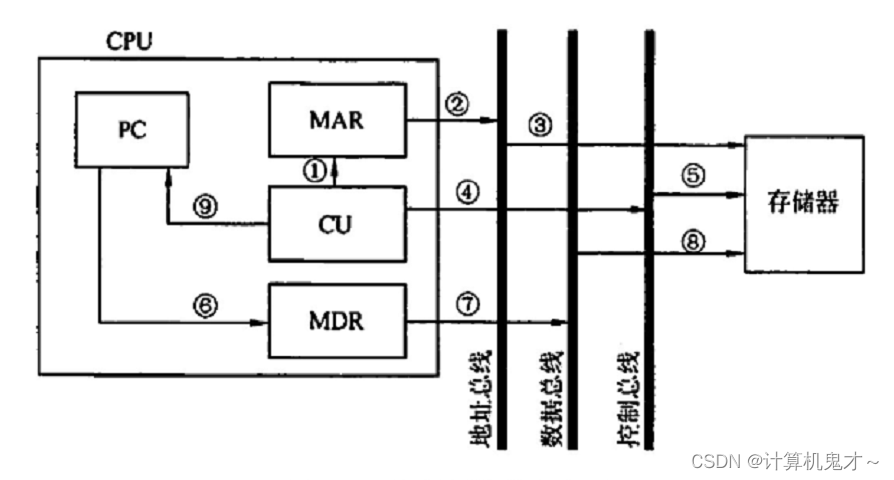

④中断周期

任务:处理中断请求

步骤:

1)CU控制将SP减1,SP----->MAR----->地址总线----->主存

2)CU发出写命令----->控制总线----->主存

3)PC----->MDR----->数据总线----->主存(程序断点存入主存)

4)CU(中断服务程序的入口地址)----->PC

例题:CPU响应中断的时间是():

A.一条指令执行结束

B.I/O设备提出中断

C.取指周期结束

D.指令周期结束

【答案】:A

【解析】:若有中断,则在执行周期后执行中断。

例题:冯诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是()

A.指令操作码的译码结果

B.指令和数据的寻址方式

C.指令周期的不同阶段

D.指令和数据所在的存储单元

【答案】:C

【解析】:冯诺依曼计算机根据指令周期的不同阶段来区分从春初期取出的是指令还是数据,取值周期取出的是指令,执行周期取出来的是数据。因此,控制器可以区分存储单元中存放的是指令还是数据,存储器和运算器不能。

好的,本期的计算机考研408的文章就到这里结束啦,感兴趣的兄弟姐妹们能给我一个免费的点赞和关注再走吗?

1346

1346

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?