前几天画pcb的时候,出现这个错误,开始百思不得其解,后面搞明白了

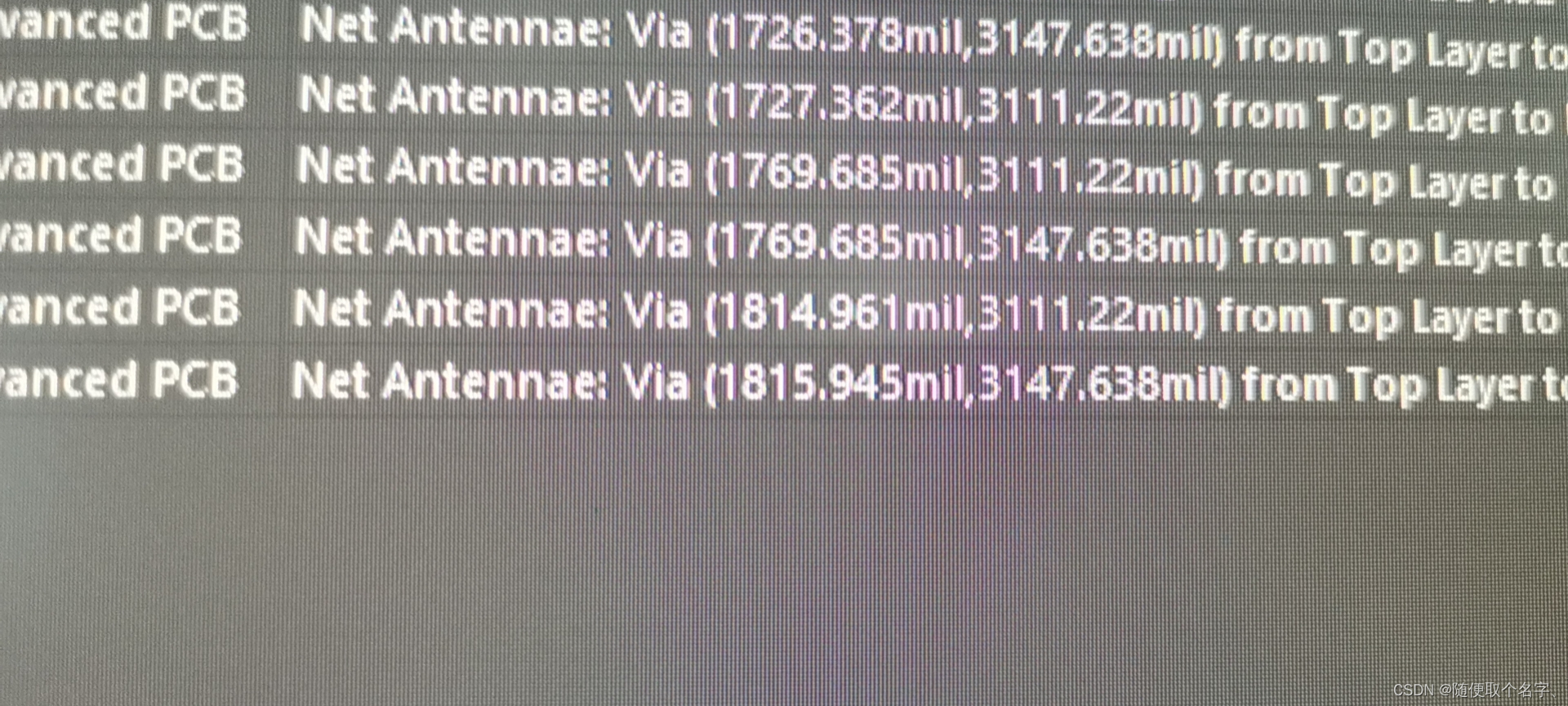

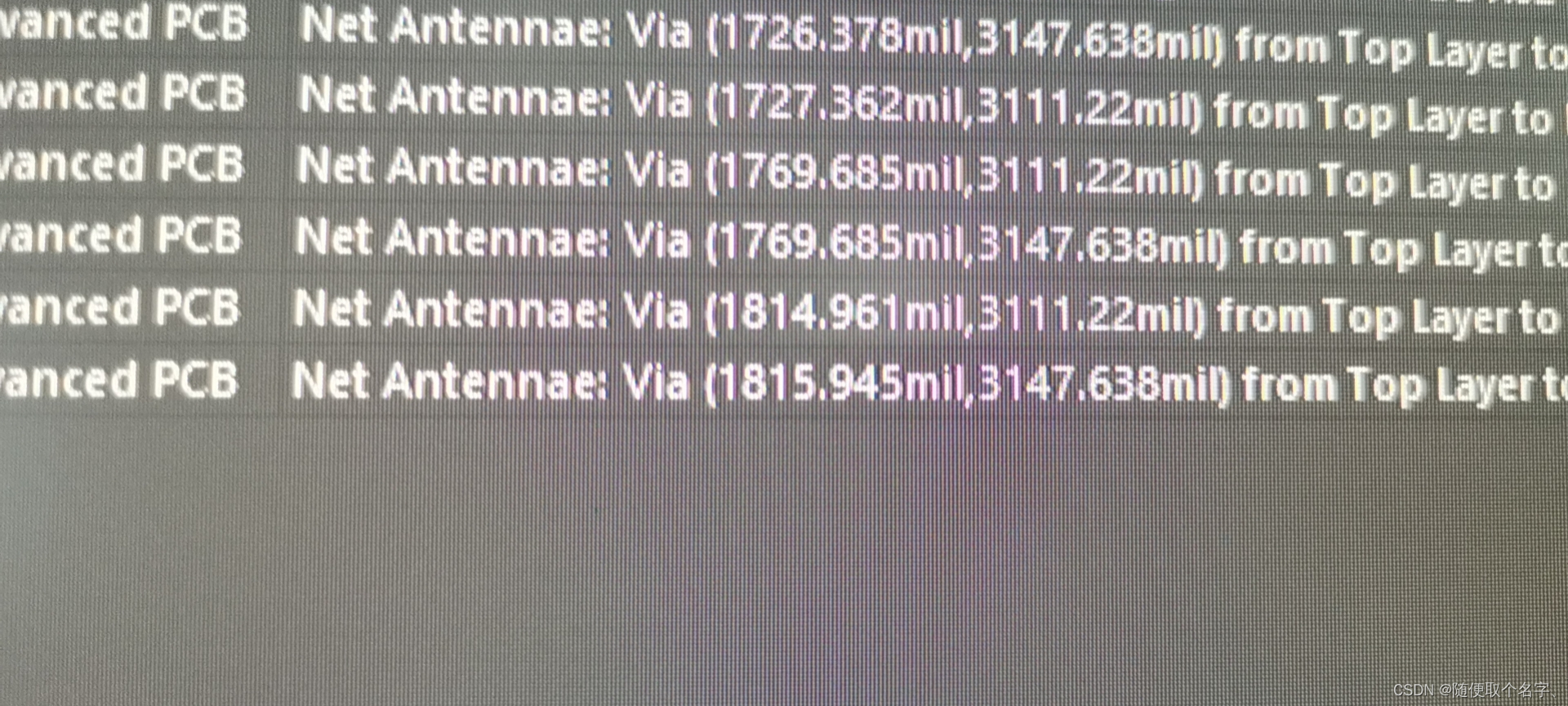

绘制PCB的时候,出现了“net antenna:via……”的错误原因:

1、规则里面设置错误

2、过孔上的这根线没有连接上了网络

3、不需要过孔的铺铜放了过孔。

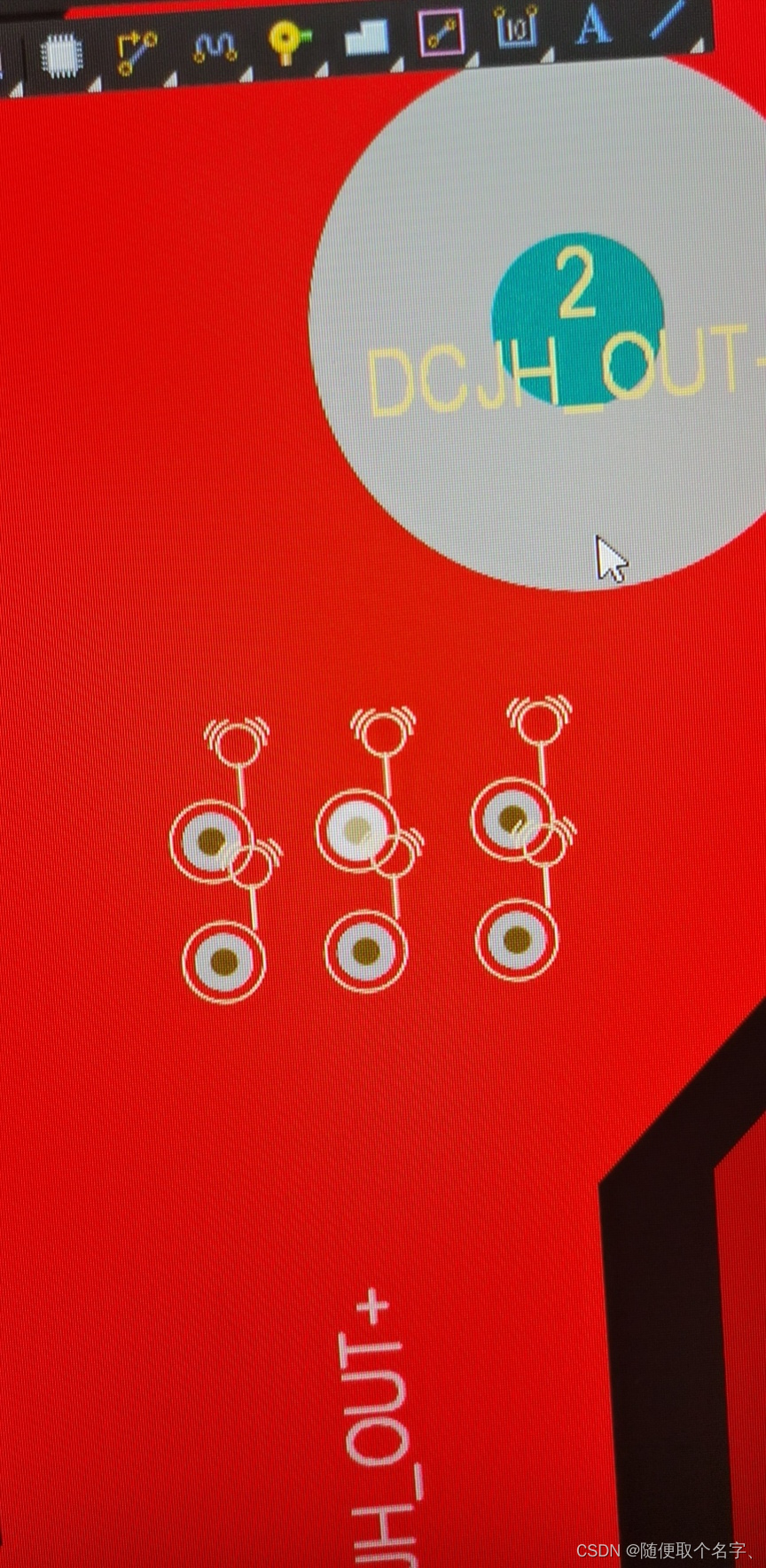

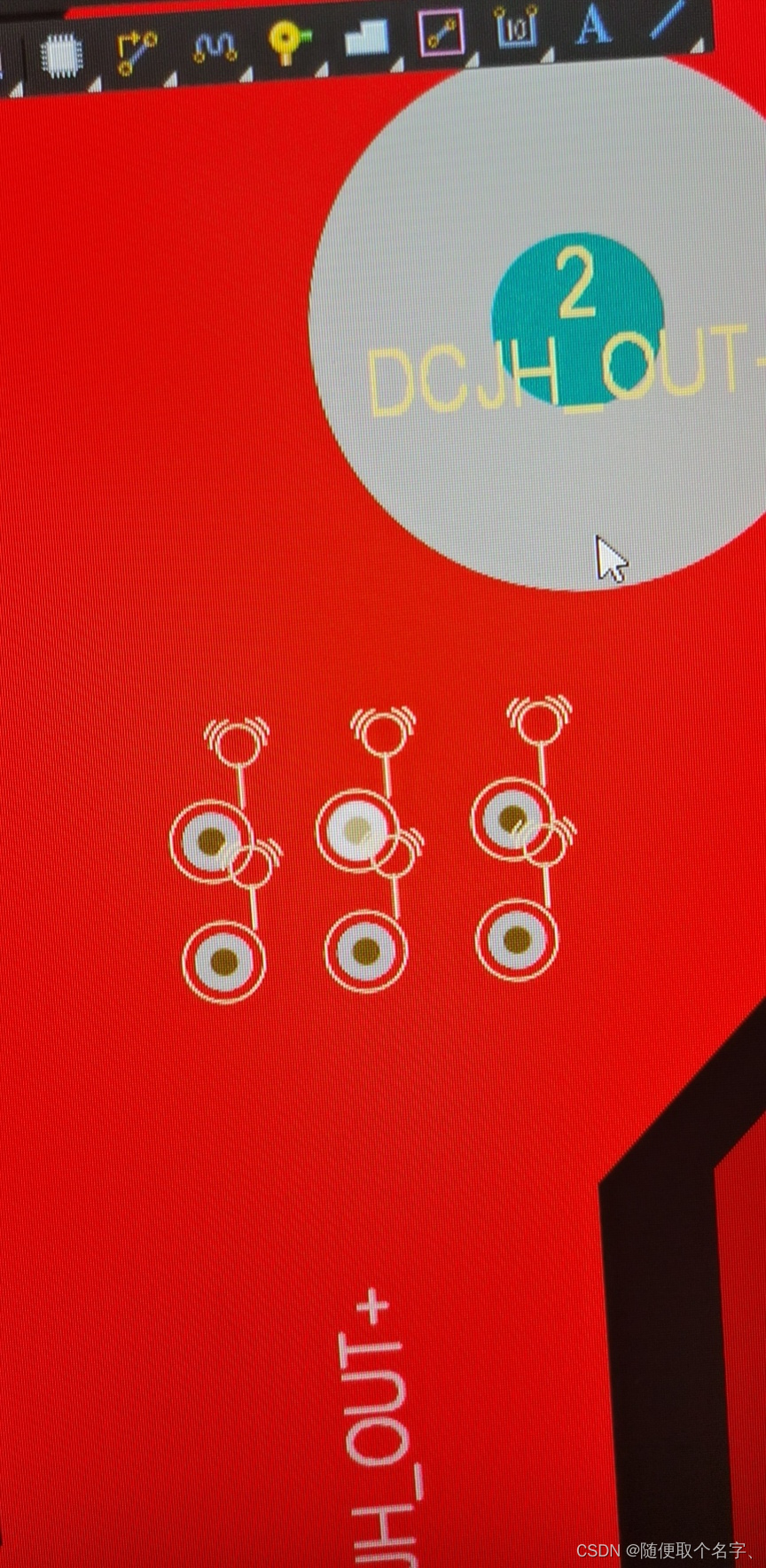

我当时错误原因:

我的铺铜在顶层 ,但这个铺铜的网络并没有穿层,仅出现在在顶层,所以解决方法是:把这些不必要的过孔删掉。

前几天画pcb的时候,出现这个错误,开始百思不得其解,后面搞明白了

绘制PCB的时候,出现了“net antenna:via……”的错误原因:

1、规则里面设置错误

2、过孔上的这根线没有连接上了网络

3、不需要过孔的铺铜放了过孔。

我当时错误原因:

我的铺铜在顶层 ,但这个铺铜的网络并没有穿层,仅出现在在顶层,所以解决方法是:把这些不必要的过孔删掉。

6232

6232

2万+

2万+

5万+

5万+

3413

3413

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?