4.2 选择题

(1)[2010] 下列有关 RAM 和 ROM 的叙述中,正确的是 。

Ⅰ.RAM 是易失性存储器,ROM 是非易失性存储器

Ⅱ.RAM 和 ROM 都采用随机存取方式进行信息访问

Ⅲ.RAM 和 ROM 都可用作 cache

Ⅳ.RAM 和 ROM 都需要进行刷新

A.仅Ⅰ和Ⅱ B.仅Ⅱ和Ⅲ C.仅Ⅰ、Ⅱ和Ⅳ D.仅Ⅱ、Ⅲ和Ⅳ

答案:

A

解析:

RAM (Random Access Memory) 随机存取存储器是易失性存储器,而 ROM (Read Only Memory)只读存储器是非易失性存储器(课本96页),故Ⅰ正确;

按存取方式分类,RAM 为随机存储器,能够采用随机存取的方式进行信息访问(课表95页)

而 ROM 只能随机读出而不能写入,其中随机读出的操作也证明了ROM采用随机存取的方式进行信息访问,故 Ⅱ 正确;

一般 cache 采用高速的 SRAM 制作,对当前使用的信息进行读写操作,而ROM不能满足该功能,故 Ⅲ 错误;

动态 RAM 是靠 MOS 电路中的栅极电容来记忆信息的,由于电容上的电荷会泄漏,需要定时给与补充,所以动态 RAM 需要设置刷新电路,即 RAM 需要刷新,而 ROM 不需要刷新,故 Ⅳ 错误

(2)[2014] 某容量为 256MB 的存储器由若干 4M×8 位的 DRAM 芯片构成,该 DRAM 芯片的地址引脚和数据引脚总数是 。

A.19

B.22

C.30

D.36

答案: A

解析: 4M: 2 2 × 2 20 = 2 22 2^2 \times{2^{20}}=2^{22} 22×220=222,对应22根地址线,但由于DRAM芯片采用了行列地址复用技术,故地址线有11根;8:对应8根数据线,所以地址引脚+数据引脚=11+8=19。

(3)[2009] 某计算机主存容量为 64KB,其中 ROM 区为 4KB,其余为 RAM 区,按字节编址。现要用 2KB×8 位的 ROM 芯片和 4KB×4 位的 RAM 芯片来设计该存储器,则需要上述规格的 ROM 芯片数和 RAM 芯片数分别是 。

A.1、15

B.2、15

C.1、30

D.2、30

答案:

D

解析:

主存:

计算机主存容量为 64KB,按字节编址,而 1 字节等于 8 字,说明该存储器的规格为 64KB × 8位;

ROM区:

用 2KB × 8 位的 ROM 芯片构成 ROM 区为 4KB,需要 4/2(片) = 2 片该 ROM 芯片进行字扩展;

RAM区:

RAM 区 = 主存容量 64KB - ROM 区 4KB=60KB,用 4KB × 4 位的 RAM 芯片构成RAM区,

首先需要 60/4(片) = 15 片 4KB × 4 RAM芯片进行字扩展,组成 60KB × 4 位的 RAM芯片,

然后需要 8/4 (组) = 2 组 60KB × 4 位的 RAM 芯片进行位扩展,组成 60KB × 8 位的 RAM芯片

所以需要 2组 × 15片(每组15片) = 30片 4KB × 4 位的 RAM 芯片。

或者首先需要 8/4 (片) = 2 片 4KB × 4 位的 RAM 芯片进行位扩展,组成 4KB × 8 位的 RAM芯片,

然后需要 60/4(组) = 15 组 4KB × 8 位的 RAM 芯片进行字扩展,组成 60KB × 8 位的 RAM芯片,

所以需要 15组 × 2片(每组2片) = 30片 4KB × 4 位的 RAM 芯片。

(4)[2010] 假定用若干个 2KB×4 位的芯片组成一个 8K×8 位的存储器,则地址 0B1FH 所在芯片的最小地址是。

A.0000H

B.0600H

C.0700H

D.0800H

答案:

D

解析:

由于2KB×4 位的芯片的数据总线位宽不满足 8K,存储容量不满足 8 位,

可以先进行位扩展,用8/4 = 2 片 2KB × 4 位的芯片组成 2KB × 8 位的芯片,

再进行字扩展,用 8/2 = 4 组 2KB × 8 位的芯片组成 8K × 8 位的存储器,

8K × 8 位的存储器有 13 根地址线( 2 13 K B = 8 K B 2^{13}KB=8KB 213KB=8KB),对应 A 0 − A 12 A_{0}-A_{12} A0−A12,

而 2KB × 4 位的芯片有 11 根地址线( 2 11 K B = 2 K B 2^{11}KB=2KB 211KB=2KB),选中低11位作为片内地址,对应 A 0 − A 10 A_{0}-A_{10} A0−A10,

多余的2根地址线(13 - 11 = 2)通过 2:4 译码器产生各存储芯片的片选信号,选择低11~12位作为片选地址,对应 A 11 − A 12 A_{11}-A_{12} A11−A12;

当 A 12 A 11 A_{12}A_{11} A12A11为 “00” 时,选中第一组芯片:

第一组芯片最小地址和最大地址如下表,转换为十六进制为 0000H ~ 07FFH,而题目所需地址 0B1FH不在该组芯片中;

A 12 A_{12} A12 A 11 A_{11} A11 A 10 A_{10} A10 A 9 A_{9} A9 A 8 A_{8} A8 A 7 A_{7} A7 A 6 A_{6} A6 A 5 A_{5} A5 A 4 A_{4} A4 A 3 A_{3} A3 A 2 A_{2} A2 A 1 A_{1} A1 A 0 A_{0} A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 当 A 12 A 11 A_{12}A_{11} A12A11为 “01” 时,选中第二组芯片:

第二组芯片最小地址和最大地址如下表,转换为十六进制为 0800H ~ 0FFFH,而题目所需地址 0B1FH在该组芯片中,故地址 0B1FH 所在芯片的最小地址是 0800H。

A 12 A_{12} A12 A 11 A_{11} A11 A 10 A_{10} A10 A 9 A_{9} A9 A 8 A_{8} A8 A 7 A_{7} A7 A 6 A_{6} A6 A 5 A_{5} A5 A 4 A_{4} A4 A 3 A_{3} A3 A 2 A_{2} A2 A 1 A_{1} A1 A 0 A_{0} A0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 这里提供其他网站的解答链接:牛客网解答

如果你还是……还是没看懂……那那那私聊我也可以滴( ´・・)ノ(._.`)

(5)[2018] 假定 DRAM 芯片中存储阵列的行数为 r、列数为 c,对于一个 2KB×1 位的 DRAM 芯片,为保证其地址引脚数最少,并尽量减少刷新开销,则 r、c 的取值分别是 。

A.2048、1

B.64、32

C.32、64

D.1、2048

答案: C

解析: 2KB: 2 1 × 2 10 = 2 11 = 2048 2^1 \times{2^{10}}=2^{11}=2048 21×210=211=2048,对应总行数 × 总列数 = 2048;又由于要尽量减少刷新开销,那么要让芯片的行数尽可能的少,同时因为 DRAM 芯片采用了行列地址复用技术,那么行数与列数之间的差值要尽可能的小(减小开销),四个选项中只有 C 选项最符合。

(6)[2019] 假定一台计算机采用 3 通道存储器总线,配套的内存条型号为 DDR3-1333,即内存条所接插的存储器总线的工作频率为 1333MHz、总线宽度为 64 位,则存储器总线的总带宽大约是 。

A.10.66GB/s

B.32GB/s

C.64GB/s

D.96GB/s

答案:B

解析:

(7)[2015] 某计算机使用 4 体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为 8005、8006、8007、8008、8001、8002、8003、8004、8000,则可能发生访存冲突的地址对是 。

A.8004 和 8008

B.8002 和 8007

C.8001 和 8008

D.8000 和 8004

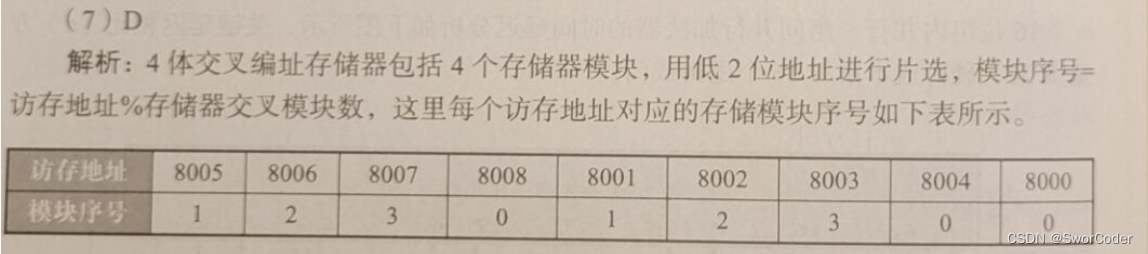

答案:D

解析:

(8)[2015] 下列存储器中,在工作期间需要周期性刷新的是 。

A.SRAM

B.SDRAM

C.ROM

D.FLASH

答案:B

解析:

(9)[2011] 下列各类存储器中,不采用随机存取方式的是 。

A.EPROM

B.CDROM

C.DRAM

D.SRAM

答案:B

解析:

(10)[2012] 下列关于闪存(Flash Memory)的叙述中,错误的是 。

A.信息可读可写,并且读、写速度一样快

B.存储元由 MOS 管组成,是一种半导体存储器

C.掉电后信息不丢失,是一种非易失性存储器

D.采用随机访问方式,可替代计算机外部存储器

答案:A

解析: 闪存可读可写,但读快写慢(课本97页),故A错误;(补充:读快写慢的原因在于闪存写入时必须擦除原有数据,因此写速度比读速度慢)

闪存属于 ROM 中的一种,其存储元由 MOS 管组成(课本111页);按存储介质分类,ROM 属于半导体存储器(课本95页),故B正确;

闪存属于非易失性存储器,掉电后信息不会丢失(课本96页),故C正确;

闪存属于 ROM 中的一种,而 ROM 只能随机读出而不能写入,其中随机读出的操作也证明了ROM 采用随机访问方式读取信息;计算机外部存储器中包含 U盘、SSD 等,而常见的

U 盘、SSD 均采用闪存这种存储单元(课本112页),即闪存可以替代计算机外部存储器,故D正确。

(11)[2017] 下列关于数组 a 的访问局部性的描述中,正确的是 。

A.时间局部性和空间局部性皆有

B.无时间局部性,有空间局部性

C.有时间局部性,无空间局部性

D.时间局部性和空间局部性皆无

答案:A

解析:

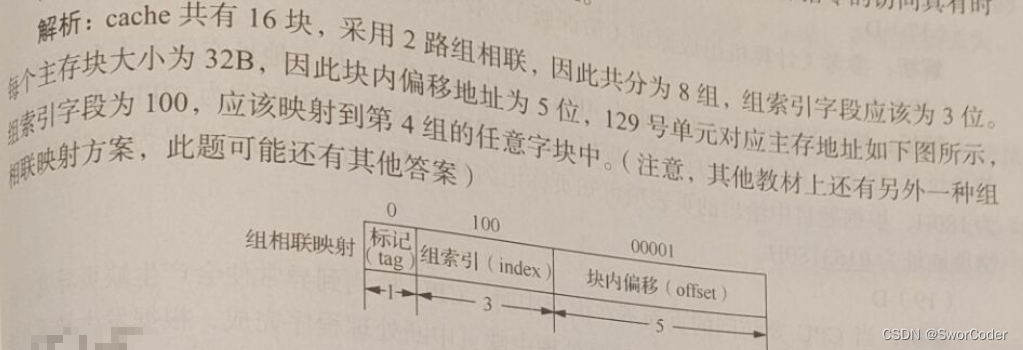

(12)[2009] 某计算机的 cache 共有 16 块,采用二路组相联映射方式(即每组 2 块)。每个主存块大小为 32B,按字节编址。主存 129 号单元所在主存块应装入的 cache 组号是 。

A.0

B.1

C.4

D.6

答案:C

解析:

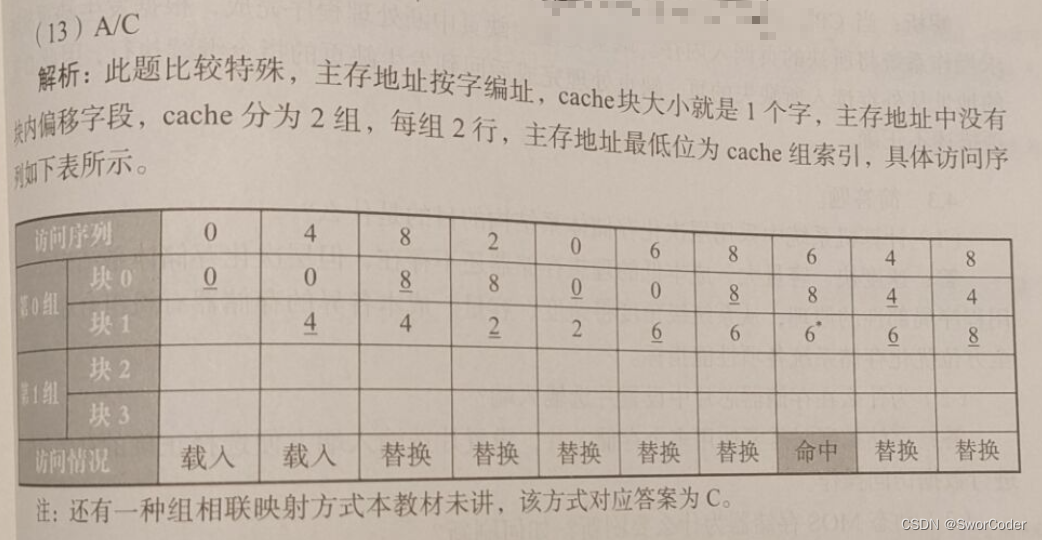

(13)[2012] 假设某计算机按字编址,cache 有 4 行,cache 和主存之间交换的块大小为 1 个字。若cache 的内容初始为空,采用二路组相联映射方式和 LRU 替换策略。访问的主存地址依次为 0、4、8、2、0、6、8、6、4、8 时,命中 cache 的次数是 。

A.1

B.2

C.3

D.4

答案:A/C

解析:

(14)[2015] 假定主存地址为 32 位,按字节编址,主存和 cache 之间采用直接相联映射方式,主存块大小为 4 个字,每个字 32 位,采用写回的方式,则能存放 4K 字数据的 cache 的总容量至少是()位。

A.146K

B.147K

C.148K

D.158K

答案:

C

解析:

(1)根据地址映射方式,画出主存地址细分图:

根据直接相连映射算法,主存字节地址细分如下图:

(2)分别计算块内偏移位数和区内行地址位数:

①主存块大小为 4 个字,每个字 32 位,那么每一块大小为 4 × 32 位 = 128 位,

由于主存按字节编址,故每一块的字节大小为 128 ÷ 8 B = 16 B = 2 4 B 2^{4}B 24B(1字节 = 8位),故块内偏移地址位数为 4 位;

②由于Cache的存储容量为 4 K 字= 4 K × 4 B = 16 KB(1字 = 32位 = 4字节),那么 Cache 一共有 16 KB ÷ 16 B = 1 K 行= 2 10 2^{10} 210行,故 Cache 行索引字段位数为 10 位;

(3)根据主存地址位数、块内偏移位数和区内行地址位数计算区地址位数:

区地址位数 = 主存地址位数 - 块内偏移位数 - 区内行地址位数 = (32 - 4 - 10) 位 = 18 位;

(4)根据Cache行大小和行数计算Cache总容量:

Cache 的总容量 = Cache 行大小 × 行数,由题目中给出的信息和已学知识可以推断:一个 Cache 行包括有效位(默认为 1 位)、标记位(在直接相联映射方式中就是指区地址位数,前面计算出来有 18 位)、写回标志(采用写回的方式,默认为 1 位)和数据块副本(前面计算出来为 128 位)。因此,Cache 的总容量 = ( 1 + 18 + 1 + 128 ) × 2 10 位 = 148 K 位 (1+18+1+128)×2^{10}位=148K位 (1+18+1+128)×210位=148K位。

注意:

1 字节 (byte) = 8 位 (bit)是固定的,但 1 字 (word) = 32 位 (bit) = 4 字节 (byte) 还是 1 字 (word) = 64 位 (bit) = 8 字节 (byte),这个要看题目具体说明!!!

位、字节、字,这三个概念你还在搞混吗?——知乎

(15)[2014] 采用指令 cache 与数据 cache 分离的主要目的是 。

A.降低 cache 的缺失损失

B.提高 cache 的命中率

C.降低 CPU 平均访存时间

D.减少指令流水线资源冲突

答案:D

解析:

(16)[2015] 假定编译器将赋值语句“x=x+3;”转换为指令“add xaddr,3”,其中,xaddr 是 x 对应的存储单元地址。若执行该指令的计算机采用页式虚拟存储管理方式,并配有相应的 TLB,且 cache 使用写穿的方式,则完成该指令功能需要访问主存的次数至少是 。

A.0

B.1

C.2

D.3

答案:B

解析:

(17)[2010] 下列命中组合情况中,一次访存过程中不可能发生的是 。

A.TLB 未命中,cache 未命中,Page 未命中

B.TLB 未命中,cache 命中,Page 命中

C.TLB 命中,cache 未命中,Page 命中

D.TLB 命中,cache 命中,Page 未命中

答案:D

解析:

(18)[2013] 某计算机主存地址空间大小为 256MB,按字节编址。虚拟地址空间大小为 4GB,采用页式存储管理方式,页面大小为 4KB,TLB(快表)采用全相联映射,有 4 个页表项,内容如表 4.12所示。

答案:A

解析:

(19)[2019] 下列关于缺页处理的叙述中,错误的是 。

A.缺页是在地址转换时 CPU 检测到的一种异常

B.缺页处理由操作系统提供的缺页处理程序完成

C.缺页处理程序根据页故障地址从外存读入所缺失的页

D.缺页处理完成后执行发生缺页的指令的下一条指令

答案:D

解析:

4.3 简答题

(1)计算机系统中采用层次化存储体系结构的目的是什么?

答: 速度快、容量大、成本低的理想存储器还不存在(存储器技术指标),但层次化存储体系结构可以利用程序局部性的原理,从系统级的角度将速度、容量、成本各异的存储器有机结合在一起,全方位优化存储系统各项性能指标。

(3)动态 MOS 存储器为什么要刷新?如何刷新?

答: 在动态存储单元中,信息以电荷形式存储在工作管的栅极电容中,但电容容量较小,所存电荷会在一段时间后逐渐泄露(一般为ms级)。为使所存信息能长期保存,需要在电容中电荷泄露完之前定时地补充电荷,这一过程称为刷新。动态 MOS 存储器刷新方式主要有集中刷新、分散刷新和异步刷新3种,由于存储器采用行列结构,因此刷新时先按行进行。

4.6 用 32K×8 位 RAM 芯片和 64K×4 位 ROM 芯片设计 256K×8 位存储器。其中,从 30000H 到3FFFFH 的地址空间为只读存储区,其他为可读、可写存储区。完成存储器与 CPU 的连接。

答:

30000H 到 3FFFFH 的地址空间为只读存储区,

故所需ROM的存储容量为:3FFFFH-30000H+1=10000H= 1 6 4 B = 2 16 B = 64 K B 16^{4}B=2^{16}B=64KB 164B=216B=64KB,

64K的存储容量满足设计,但由于存储器为8位数据位宽,而ROM芯片为4位数据位宽,故需要进行位扩展,需要2片64K×4 位 ROM 芯片;

所需RAM的存储容量=总容量-ROM容量=256KB-64KB=192KB,8位数据位宽满足设计,

但由于存储器需要RAM的存储容量为192KB,而RAM 芯片的存储容量为32KB,

故需要进行字扩展,需要192/32(片)=6片RAM芯片。

ROM 芯片设计 256K×8: 256 k = 2 18 256k=2^{18} 256k=218,故共有18根地址线,对应 A 0 − A 17 A_{0}-A_{17} A0−A17;

“256K×8”,故有8根数据线,对应 D 0 − D 7 D_{0}-D_{7} D0−D7;

由于RAM芯片为32K,故需要15根地址线,对应 A 0 − A 14 A_{0}-A_{14} A0−A14,

其余3根地址线可以拿来控制片选信号;而ROM芯片存储容量为64K,故需要16根地址线,对应 A 0 − A 15 A_{0}-A_{15} A0−A15,

其余2根地址线可以拿来控制片选信号,综上所述,可以使用3:8译码器来控制片选信号,用3根地址线控制8个芯片的片选信号。

位扩展时,所有芯片需要同时工作;而字扩展时,所有芯片中只有一个芯片工作,由于ROM芯片有2片,地址线同时也有两根,故需要使用或门来进行控制片选;

RAM的控制信号为CS#和WE#,读写控制R/W#和访存请求MREQ#

绘图如下:

4.8 用 64K×1 位的 DRAM 芯片构成 1M×8 位的存储器,若采用异步刷新,每行刷新间隔不超过2ms,则产生刷新信号的间隔时间是多少?假设读写周期为 0.5μs,若采用集中刷新方式,则存储器刷新一遍最少要用多少个读写周期? CPU 的“死”时间为多少?

答: 64KB×1位的DRAM芯片的排列方式为256行×256列,已知每行刷新间隔不超过2ms,可知最大刷新周期为2ms,如采用异步刷新,需要将2ms分成256个时间段,2ms/256=7.8125μs,每个时间段最后0.5μs用于刷新DRAM的一行,因此产生刷新信号的时间间隔为7.8125μs。

若采用集中刷新,存储器刷新一遍至少需要256个读写周期,CPU的“死”时间是256×0.5μs=128μs。

4.9 设有某动态 RAM 芯片,容量为 64K×1 位,除电源线、接地线和刷新线外,该芯片的最小引脚数量是多少?

答: 该芯片有1位数据线,行选通RAS和列选通CAS各1位,64KB存储器对应16根地址线,由于DRAM中行列地址复用,所以实际地址线为8根,故在不考虑电源线的情况下,该DRAM芯片的最小引脚数位1+1+1+8=11个。

4.10 用 16K×1 位的 DRAM 芯片构成 64K×8 位的存储器,设存储器的读写周期为 0.5μs,要使 CPU在 1μs 内至少访问存储器一次,采用哪种刷新方式比较合适?若每行刷新间隔不超过 2ms,该方式下刷新信号的产生周期是多少?

答: CPU在1μs内至少访问存储器一次,而存储器的读写周期为0.5μs,故不可采用集中式刷新方式,因为其“死”时间会超过1μs,无法满足CPU在1μs内至少访问存储器一次,故采用异步刷新方式或分散刷新方式比较合适。

设16KB×1位的DRAM芯片采用128×128的排列方式,如采用异步刷新,则需将2ms分为128个时间段,每段的时间为2ms/128=15.625μs,则刷新信号的产生周期为15.625μs。

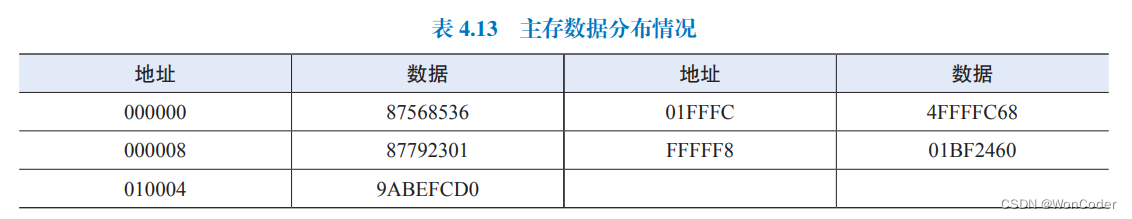

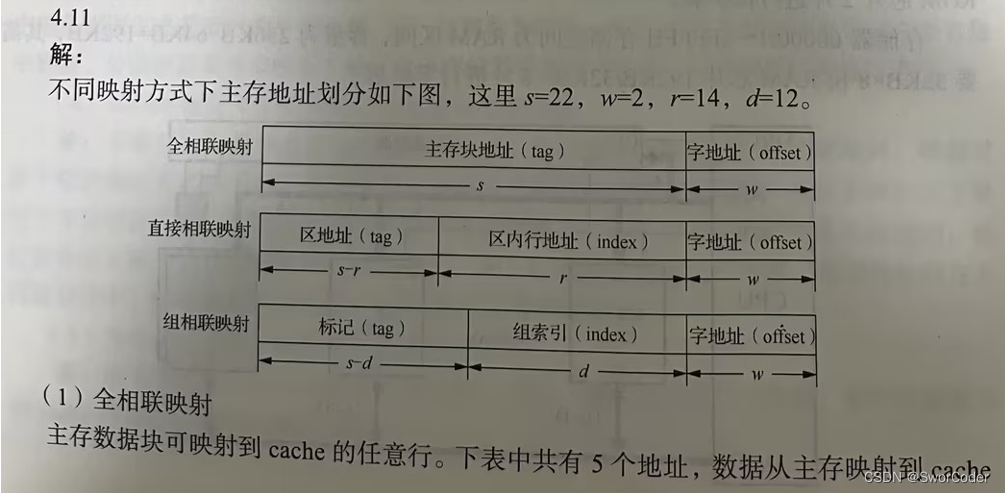

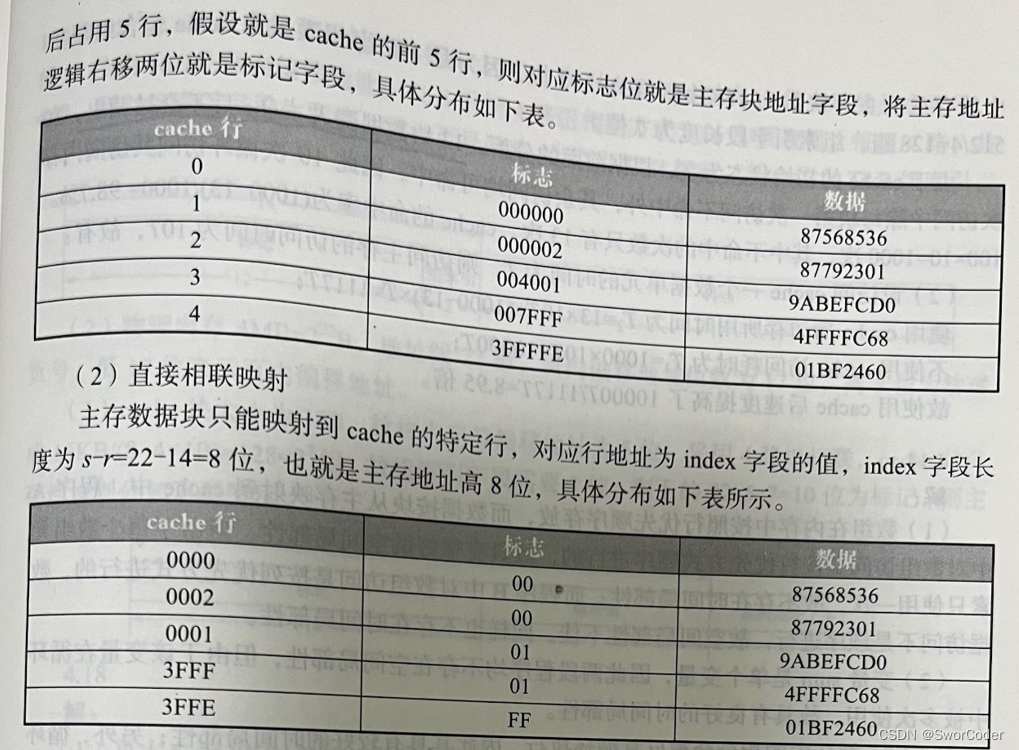

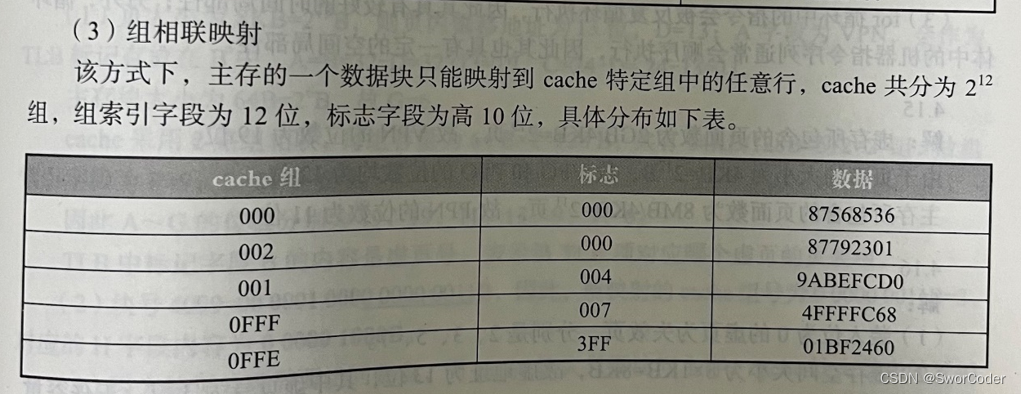

4.11 设 cache 的容量为 214 块,每块是一个 32 位字,主存容量是 cache 容量的 256 倍,其中有表 4.13所示的数据(地址和数据均采用十六进制表示)。将主存中这些数据装入 cache 后,cache 各块中的数据内容及相应的标志是什么?

(1)全相联映射;(2)直接相联映射;(3)四路组相联映射

答:

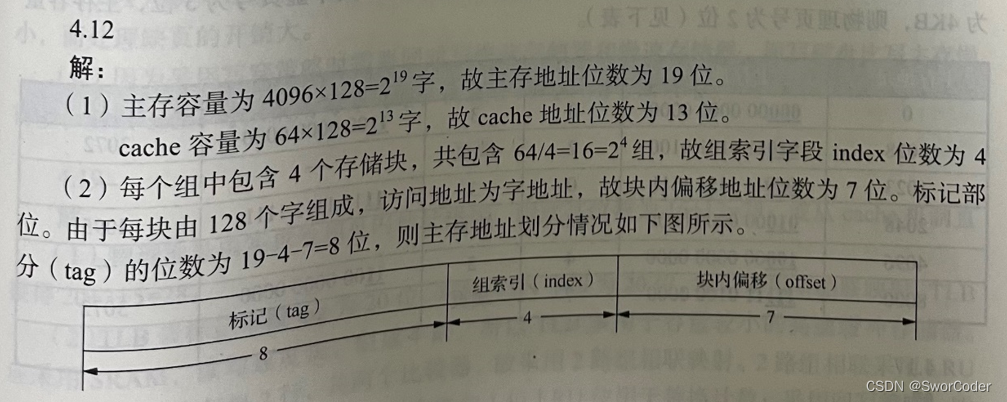

4.12 某计算机的 cache 由 64 个存储块构成,采用四路组相联映射方式,主存包含 4096 个存储块,每块由 128 个字组成,访问地址为字地址。

(1)主存地址和 cache 地址各有多少位?

(2)按照题干条件中的映射方式,列出主存地址的划分情况,并标出各部分的位。

答:

4.13 某计算机的主存容量为 4MB,cache 容量为 16KB,每块包含 8 个字,每字为 32 位,映射方式采用四路组相联。设 cache 的初始状态为空,CPU 依次从主存第 0,1,2,…,99 号单元读出 100 个字(每次读一个字),并重复此操作 10 次,替换算法采用 LRU 算法。

(1)求 cache 的命中率。

(2)若 cache 比主存快 10 倍,分析采用 cache 后存储访问速度提高了多少。

答:

4.14 假定某数组元素按行优先顺序存放在主存中,则在以下两段伪代码 A 和 B 中,分析下列问题。

(1)两段代码中对数组访问的时间局部性和空间局部性。

(2)变量 sum 的时间局部性和空间局部性。

(3)for 循环体对指令访问的时间局部性和空间局部性。

// 伪代码A

int sum_array_A(int a[M][N])

int i,j,sum=0;

for(i=0;i<M;i++)

for(j=0;j<N;j++)

sum+=a[i][j];

return sum;

// 伪代码B

int sum_array_B(int a[M][N])

int i,j,sum=0;

for(i=0;i<N;i++)

for(j=0;j<M;j++)

sum+=a[j][i];

return sum;

答:

(1) 数组在内存中按照行优先顺序存放,而数据按块从主存映射到 cache 中。程序A 中对数组访问是按行优先方式顺序进行的,故具有很好的空间局部性,但由于每个数组元素只使用一次,故不存在时间局部性;而程序 B 中对数组访问是按列优先方式进行的,数据访问不是顺序进行,故空间局部性不佳,同样也不存在时间局部性。

(2) 变量 sum 是单个变量,因此两段程序均不存在空间局部性,但由于该变量在循环中被多次使用,故具有良好的时间局部性。

(3) for 循环中的指令会被反复循环执行,因此其具有较好的时间局部性;另外,循环体中的机器指令序列通常会顺序执行,因此其也具有一定的空间局部性。

参考文档:【存储技术】局部性(时间局部性、空间局部性)—— CSDN

9088

9088

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?