目录

描述

题目描述:

请编写一个信号发生器模块,根据波形选择信号wave_choise发出相应的波形:wave_choice=0时,发出方波信号;wave_choice=1时,发出锯齿波信号;wave_choice=2时,发出三角波信号。

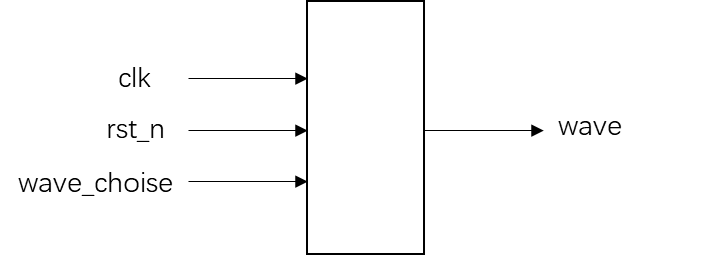

模块的接口信号图如下:

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

wave_choise:2比特位宽的信号,根据该信号的取值不同,输出不同的波形信号

输出描述:

wave:5比特位宽的信号,根据wave_choise的值,输出不同波形的信号

代码如下:

(CSDN代码块不支持Verilog,代码复制到notepad++编辑器中,语言选择Verilog,看得更清楚)

`timescale 1ns/1ns

module signal_generator(

input clk,

input rst_n,

input [1:0] wave_choise,

output reg [4:0]wave

);

reg [4:0] cnt;

reg flag;

// 方波模式下,计数器控制

always@(posedge clk or negedge rst_n) begin

if(~rst_n)

cnt <= 0;

else

cnt <= wave_choise!=0 ? 0:

cnt ==19? 0:

cnt + 1;

end

// 三角波模式下,标志位控制

always@(posedge clk or negedge rst_n) begin

if(~rst_n)

flag <= 0;

else

flag <= wave_choise!=2 ? 0:

wave ==1 ? 1:

wave ==19? 0:

flag;

end

// 更新wave信号

always@(posedge clk or negedge rst_n) begin

if(~rst_n)

wave <= 0;

else

case(wave_choise)

0 : wave <= cnt == 9? 20 :

cnt ==19? 0 :

wave;

1 : wave <= wave==20? 0 : wave+1;

2 : wave <= flag==0 ? wave-1: wave+1;

default: wave <= 0;

endcase

end

endmodule

4437

4437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?