成像原理

CMOS 的材质主要是利用硅和锗这两种元素所做成的半导体,在CMOS上共存着带N(带 ━ 电) 和 P(带 + 电)级的半导体,这两个互补效应所产生的电流即可被处理晶片纪录和解读成影像。CMOS因为在像素的旁边就放置了信号放大器,导致其缺点容易出现杂点 ,特别是处理快速变化的影像时,由于电流变化过于频繁而会产生过热的现象,更使得杂讯难以抑制。

sensor硬件结构

像素(Pixel),是图像传感器的最小感光单元,像素阵列排列在一起形成了图像传感器的感光区域。

一个严格意义上的像素,即pixel,是一个具备红、绿、蓝三个颜色分量的组合体,能够表达RGB空间中的一个点。而sensor上的一个像点只能表达三种颜色中的一个,所以在sensor范畴内并不存在严格意义上的像素概念。但是很多情况下人们并不刻意区分像素和像点在概念上的差别,经常会用像素来指代像点,一般也不会引起歧义。

ppi 像素密度

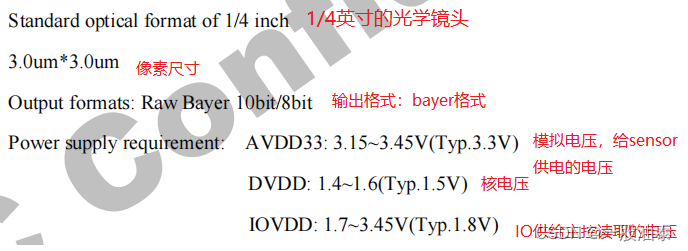

像素尺寸(Pixel Size),是指图像传感器单个感光元件的尺寸,像素的尺寸越大,接收光子的数量就越多,同光照条件和曝光时间内产生的电荷也越多。

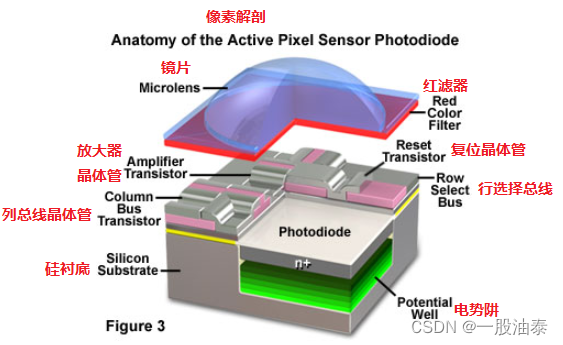

一个像点的结构:

- 硅感光区,捕获光子,激发光生电子

- 势阱,用电场捕获、存储光生电子

- 电路,将电荷数量变换为电压信号,以及复位、选择、读出逻辑

- 滤光膜,选择性透过三种波长中的一种

- 微透镜,将入射光线会聚到感光区

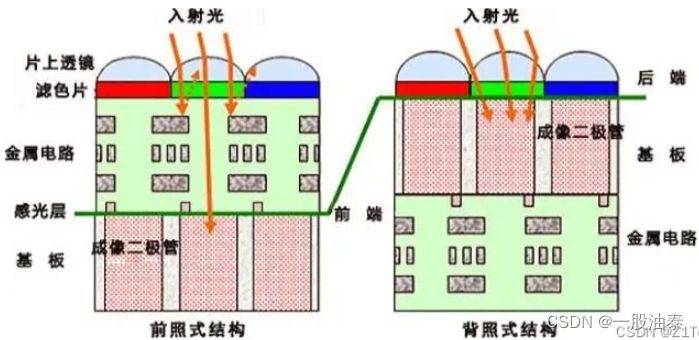

sensor的结构

主要分为FSI(前照式)和BSI(背照式)两种,前照式的金属布线层在CFA(色彩滤波列阵)和光电二极管的中间,当光线进入二极管时会有损失,背照式则将金属布线层放在了光电二极管的下面,光线透过彩色滤波片后可直接进入到光电二极管,这种结构不仅增大了进光量,且有效抑制了光线射入角变化引起的感光度下降。如今,背照式已成为中高端CIS的主流技术。堆叠式/堆栈式(Stark)则是在背照式的一种改良,将线路层挪到了感光元件的底部,最大化了感光区域,同时也缩小了芯片的整体面积。

CFA(色彩滤波列阵)

每个像素点上覆盖有一种颜色的滤光片,从而去感知每种颜色的亮度。为了能够区分颜色,人们在硅感光区上面设计了一层滤光膜,每个像素上方的滤光膜可以透过红、绿、蓝三种波长中的一种,而过滤掉另外两种

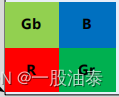

Bayer阵列格式:绿色分量为总像素数的一半,红色蓝色为总像素的四分之一

Bayer数据,其一般格式为:

奇数扫描行输出 RGRG……

偶数扫描行输出 GBGB……

奇数扫描行的第1,2,3,4,…象素分别采样和输出R,G,R,G,…数据;

偶数扫描行的第1,2,3,4,…象素分别采样和输出G,B,G,B,…数据。

HVblank

H_Blank:是指行消隐或称水平消隐,假定曝光起始位置在图像的左上角,对于逐行曝光的 sensor 来说,曝光从第一个像素开始,依次曝光直至这行的最后一个像素曝光结束,这时曝光位置要从此行的尾部快速移动到下一行的头部,开始下一行的曝光,这段行与行之间的返回过程称为H_Blank。

V_Blank:是指场消隐或称垂直消隐,假定曝光起始位置在图像的左上角,曝光完成一帧图像后,曝光位置要从图像的右下角返回左上角,开始新一帧的曝光,这一段时间间隔称为V_Blank。

传输接口

主要有MIPI和DVP等接口,(Mobile Industry Processor Interface)是串口,移动行业处理器接口,是MIPI联盟发起的为移动应用处理器制定的开放标准,具有传输速度快,抗干扰能力强等特点,主要有CLKP/N、DATAP/N管脚,一般有1/2/4Lane。DVP(Digital Video Port)是并口,主要有MCLK,PCLK,VSYNC,HSYNC,DATA管脚,可以传输8/10/12 bits数据,速度较慢,传输的宽带低。除此之外,还有LVDS、Parallel、HISPI以及索尼的SLVS-EC接口等等。

379

379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?