一.HLS

1.HLS介绍

HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境中来实现,无缝的将硬件仿真环境集合在一起,使用软件为中心的工具、报告以及优化设计,很容易的在 FPGA 传统的设计工具中生成 IP。、

2.与VHDL/Verilog编程技术关系

HLS是一种高层次的硬件设计方法,可以使用C/C++等高级语言来描述和生成FPGA或ASIC的电路。HLS与VHDL/Verilog的关系是,HLS可以自动转换成VHDL/Verilog等底层硬件描述语言(RTL),从而简化了硬件设计的过程。

3.关键技术

HLS的关键技术问题包括如何优化资源利用率、性能、功耗等指标,以及如何保证高层次设计和底层实现的一致性 。

4.存在什么技术局限性

HLS的技术局限性主要是,HLS还不能支持所有的C/C++语法和特性,有些复杂的算法和数据结构难以用HLS实现,而且HLS生成的RTL代码可能不如手写的代码高效和精确。

二.HLS实例

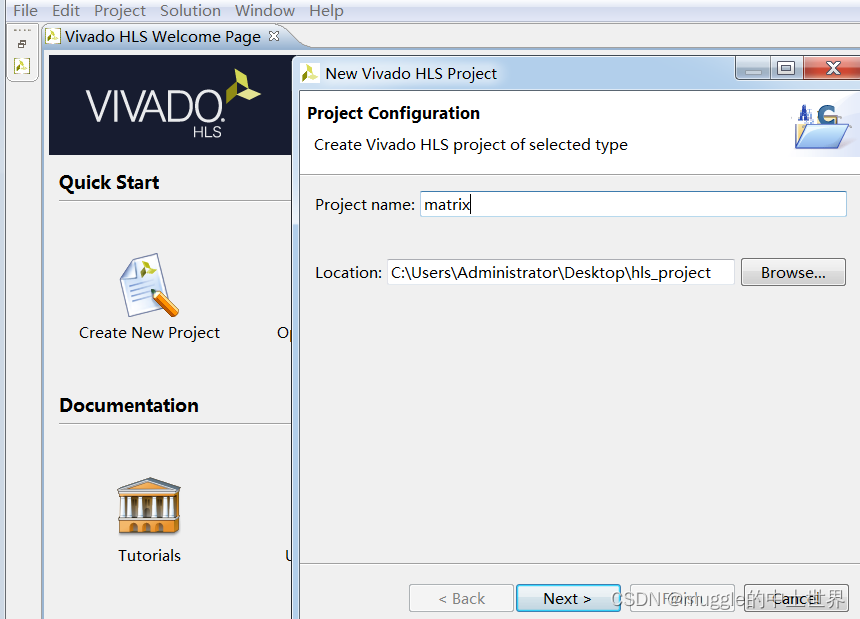

1.新建工程

2.添加源文件和测试文件

编写代码

#include <hls_stream.h>

#include <ap_axi_sdata.h>

#define N 32

#define M 32

#

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2950

2950

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?