一、CPU的功能和组成 1、CPU的功能

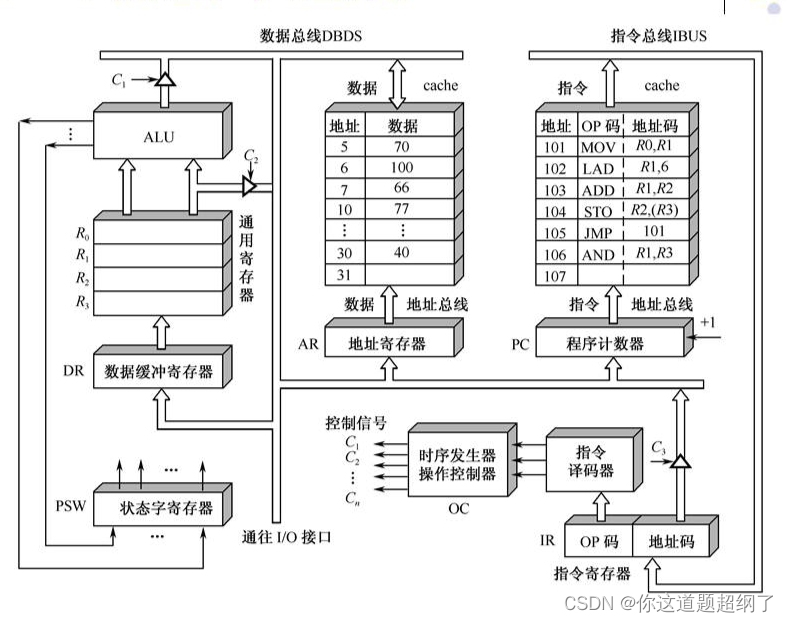

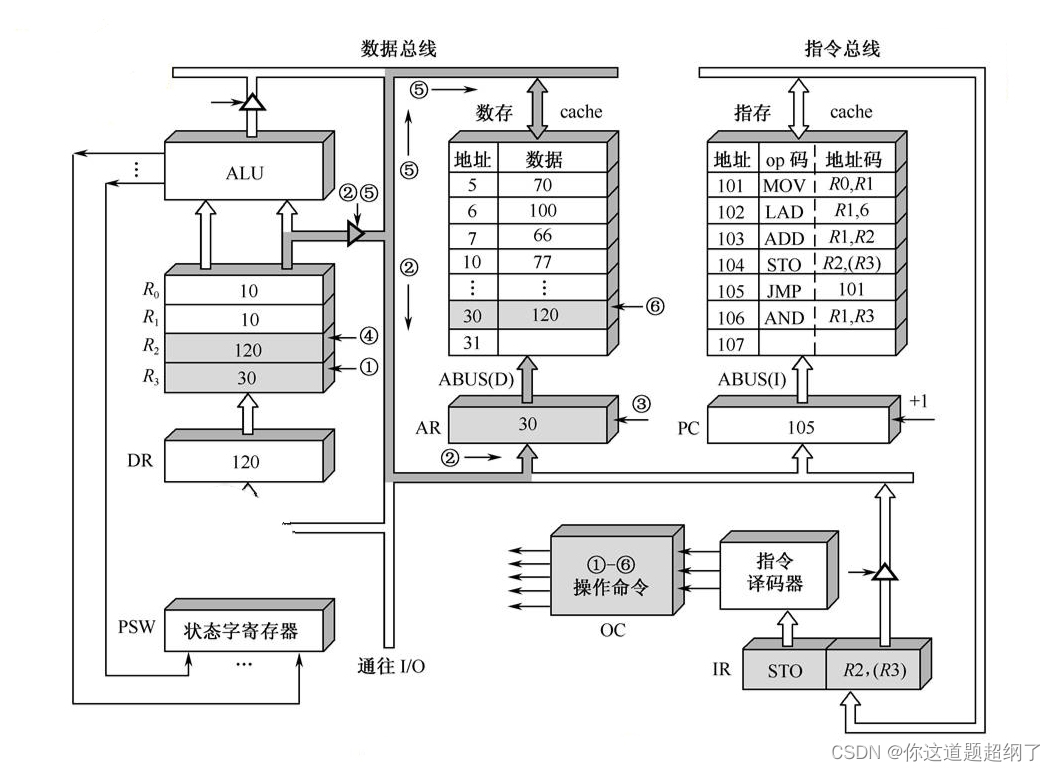

指令控制(程序的顺序控制) 操作控制(一条指令有若干操作信号实现) 时间控制(指令各个操作实施时间的定时) 数据加工(算术运算和逻辑运算) 2、CPU的基本组成  (1)中央处理器CPU=运算器+ cache +控制器 (2)运算器 ALU 通用寄存器:R0~R3 暂存器:DR状态字 寄存器:PSW (3) cache 指令cache:PC,IBUS 数据cache:AR,DBUS (4)控制器

(1)中央处理器CPU=运算器+ cache +控制器 (2)运算器 ALU 通用寄存器:R0~R3 暂存器:DR状态字 寄存器:PSW (3) cache 指令cache:PC,IBUS 数据cache:AR,DBUS (4)控制器

控制器组成:程序计数器、指令寄存器、数据缓冲器、地 址寄存器、通用寄存器、状态寄存器、时序发生器、指令译码器、 总线(数据通路)

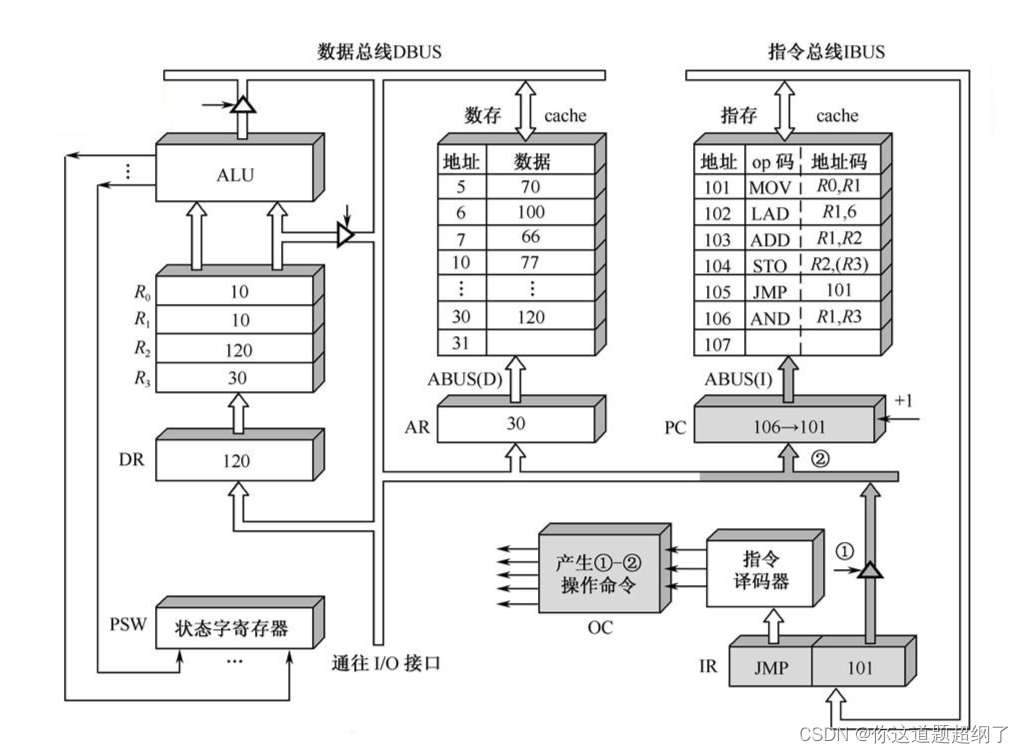

(5)程序计数器PC(Programming Counter)

用来存放正在执行的指令的地址或接着将要执行的下一条指令的地 址。

顺序执行时,每执行一条指令,PC的值应加1

要改变程序执行顺序的情况时,一般由转移类指令将转移目标地址 送往PC,可实现程序的转移。

(6)指令寄存器IR(Instruction Register)

指令寄存器用来存放从存储器中取出的待执行的指令。

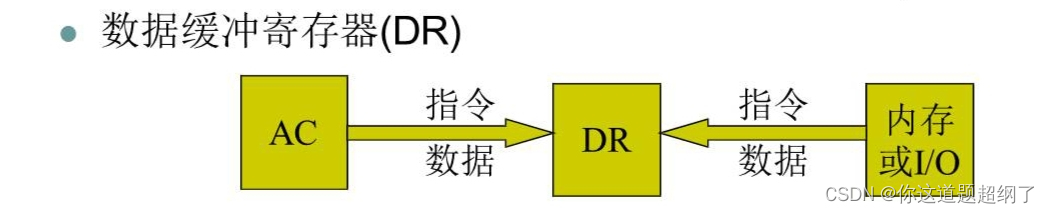

在执行该指令的过程中,指令寄存器的内容不允许发生变化,以保证实现指令的全部功能。 3、CPU中的主要寄存器  中转站 补偿速度差别 指令寄存器(IR) 程序计数器(PC) 数据地址寄存器(AR) 通用寄存器(Ro~R3) 状态字寄存器(PSW) 4、控制操作器和时序产生器 ①数据通路 ② 操作控制器:为数据通路的建立提供各 种操作信号。根据设计方法不同,可分为时序逻辑型和存储逻辑型: 硬布线控制器、微程序控制器 ③时序产生器:提供定时和时序信号 其他功能部件:中断系统、总线接口等

中转站 补偿速度差别 指令寄存器(IR) 程序计数器(PC) 数据地址寄存器(AR) 通用寄存器(Ro~R3) 状态字寄存器(PSW) 4、控制操作器和时序产生器 ①数据通路 ② 操作控制器:为数据通路的建立提供各 种操作信号。根据设计方法不同,可分为时序逻辑型和存储逻辑型: 硬布线控制器、微程序控制器 ③时序产生器:提供定时和时序信号 其他功能部件:中断系统、总线接口等

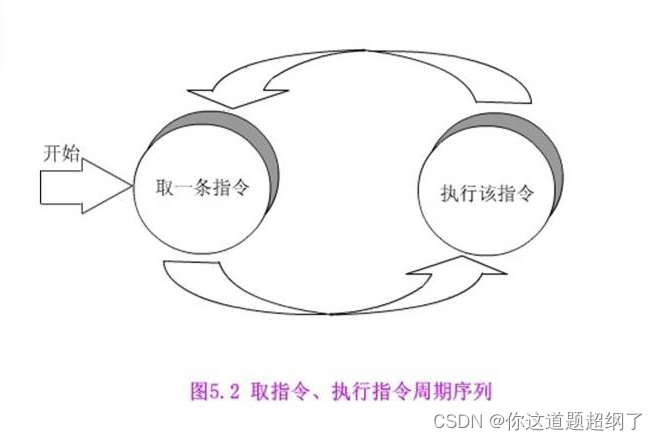

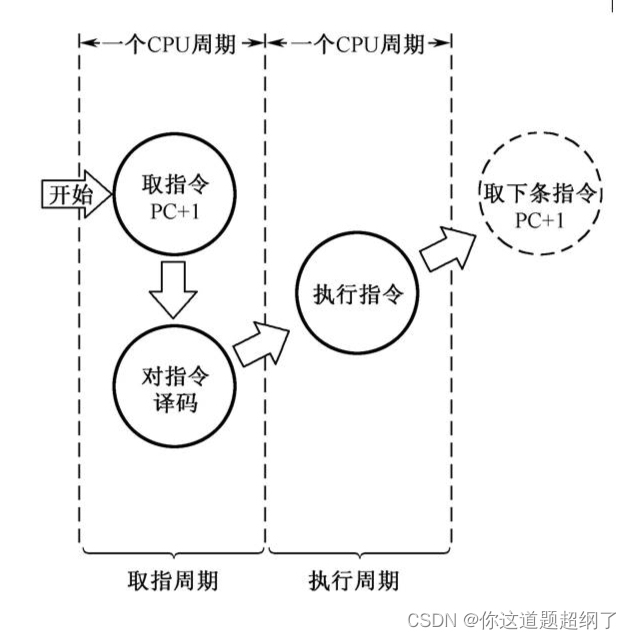

二、指令周期 1、指令周期的基本概念

(1)概念

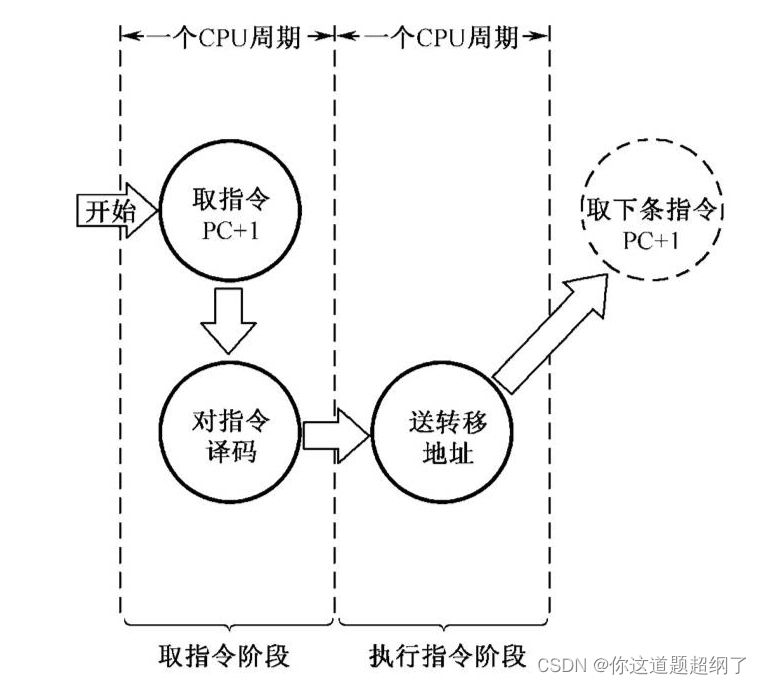

①指令周期:指取指令、分析指令到执行完该指令所需的全部 时间。

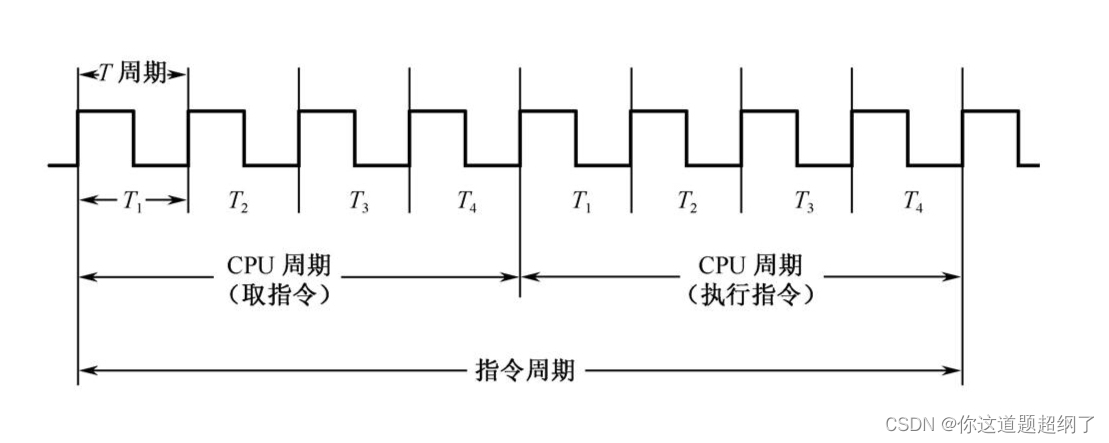

②CPU周期通常又称时钟周期

通常把一条指令周期划分为若干个机器周期,每个机器周期 完成一个基本操作。

主存的工作周期(存取周期)为基础来规定CPU周期,比如, 可以用CPU读取一个指令字的最短时间来规定CPU周期 不同的指令,可能包含不同数目的CPU周期。

一个CPU周期中,包含若干个节拍脉冲(T周期)

单周期、多周期的概念

③时钟周期

在一个CPU周期内,要完成若干个微操作。这些微操作 有的可以同时执行,有的需要按先后次序串行执行。因 而需要把一个CPU周期分为若干个相等的时间段,每一 个时间段称为一个节拍脉冲或T周期。

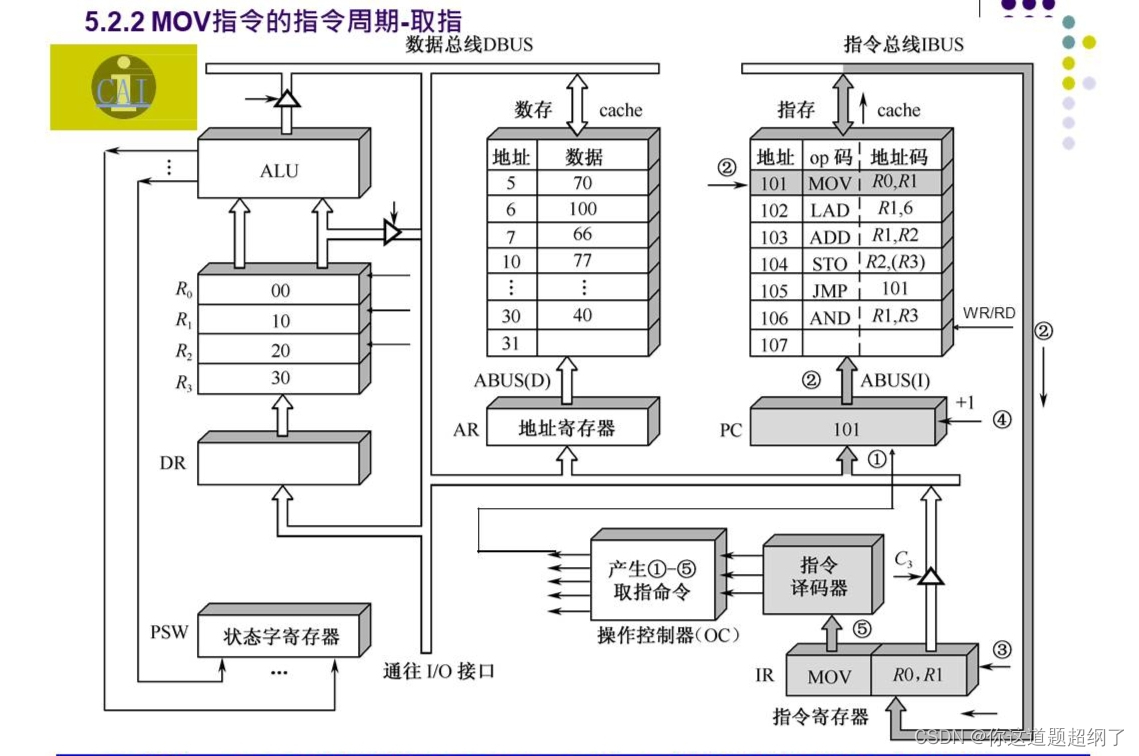

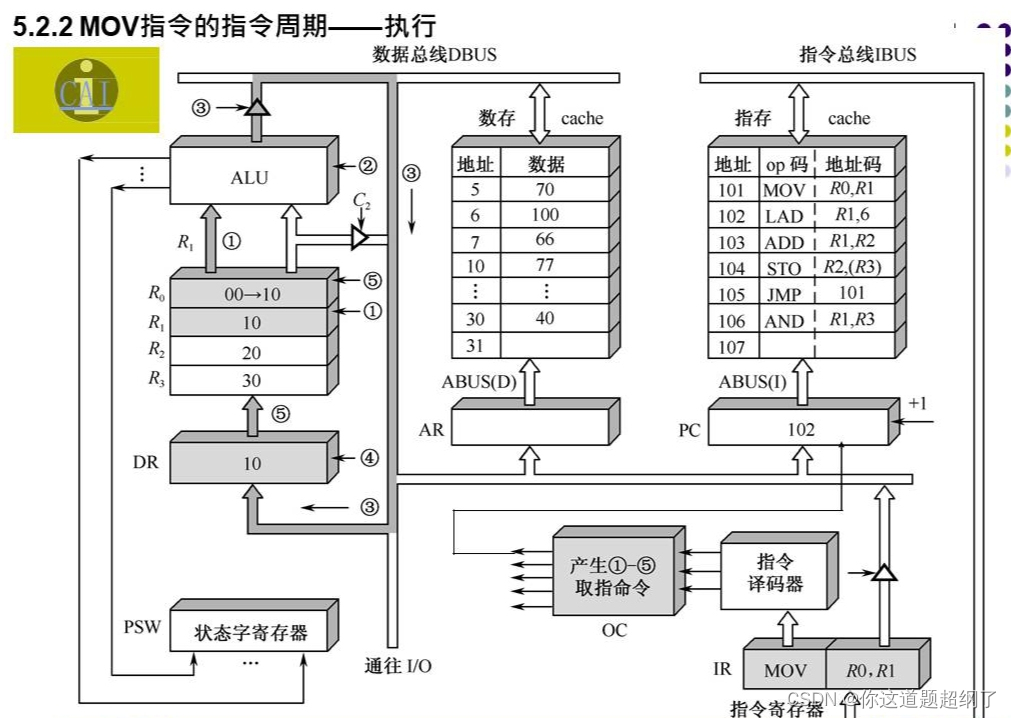

时钟周期通常定义为机器主频的倒数。时钟周期不等于T周期。 2、MOV指令的指令周期 取指周期,执行周期

2、MOV指令的指令周期 取指周期,执行周期

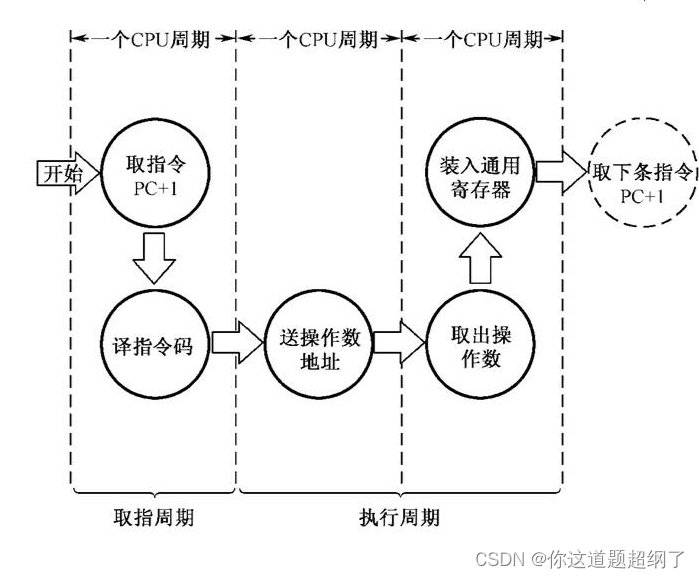

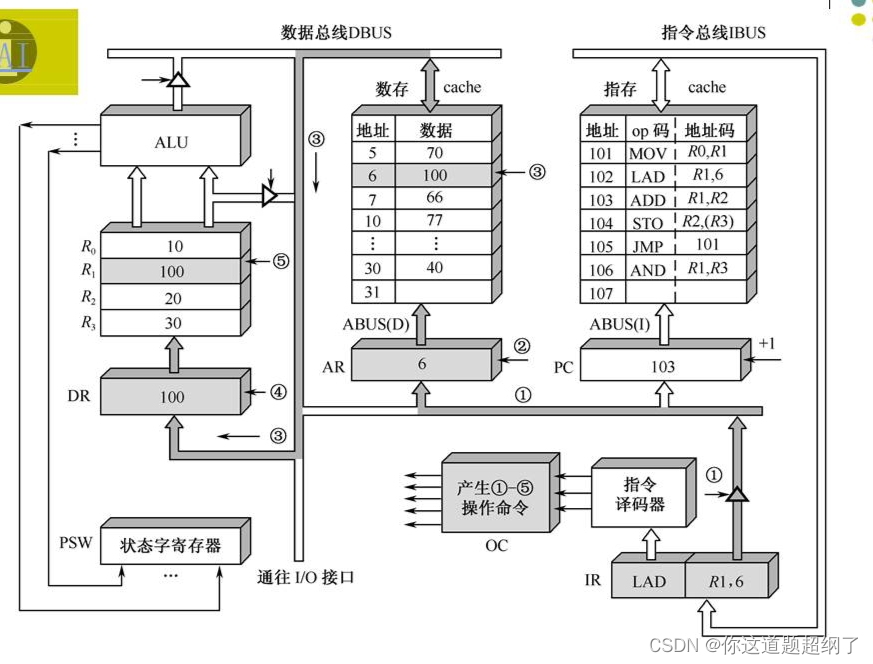

3、LAD指令的指令周期 取指周期,执行周期

3、LAD指令的指令周期 取指周期,执行周期

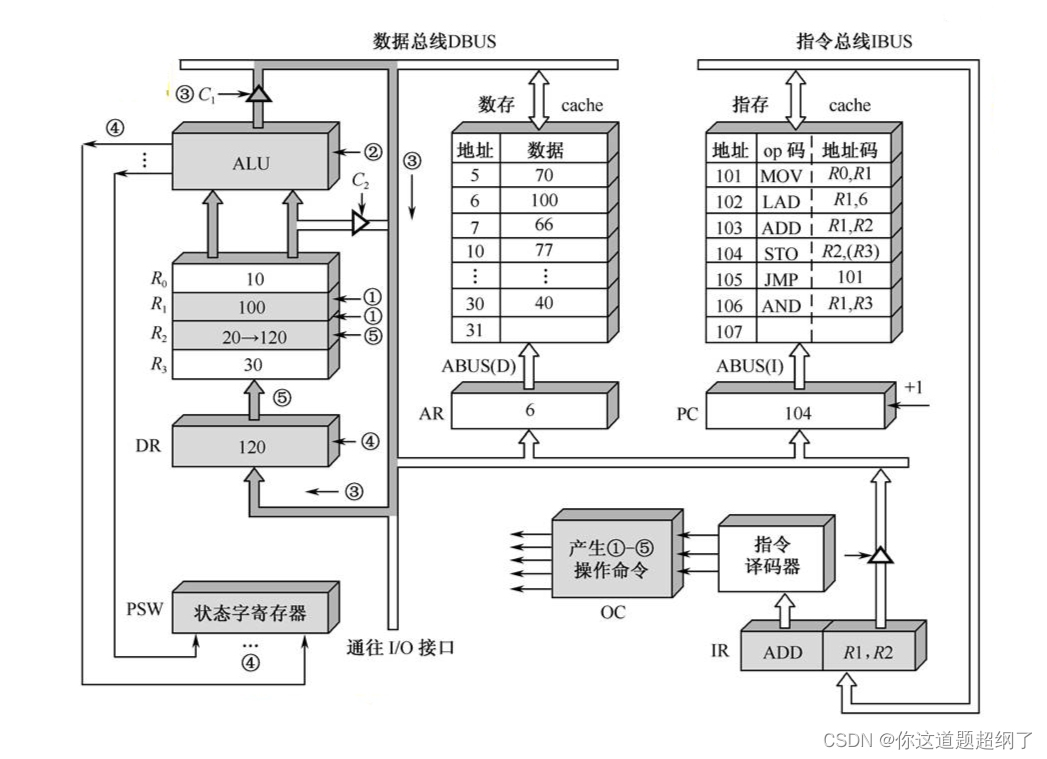

4、ADD指令的指令周期

第1个CPU周期取ADD指令(指令cache) 第2个CPU周期执行加法运算(运算器) 5、STO指令的指令周期

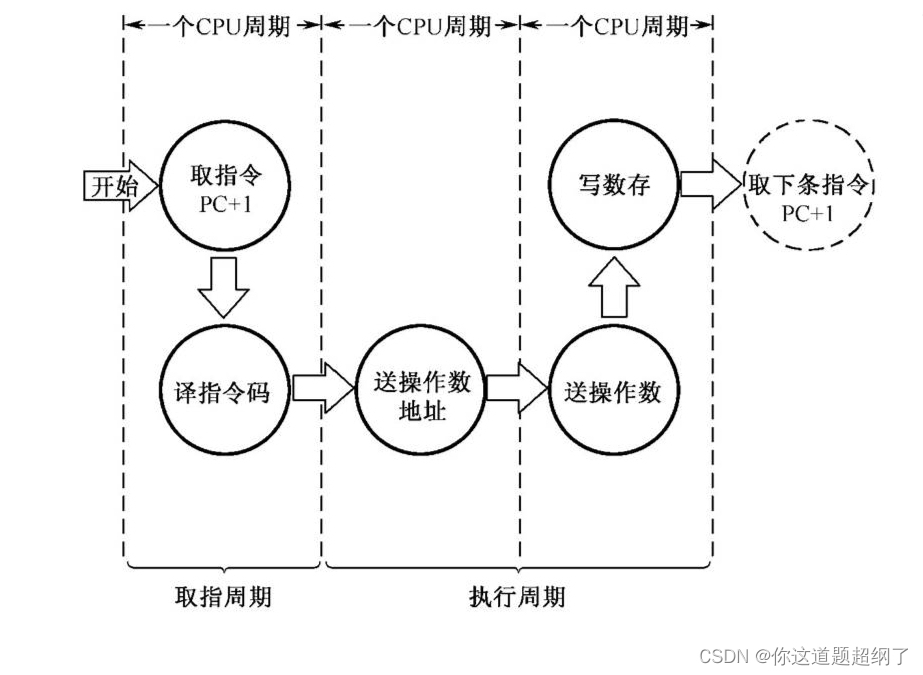

5、STO指令的指令周期

6、JMP指令的指令周期

6、JMP指令的指令周期

三、流水CPU 1、并行处理技术

(1)并行性(Parrelism)概念

问题中具有可以同时进行运算或操作的特性 例:在相同时延的条件下,用n位运算器进行n位 并行运算速度几乎是一位运算器进行n位串行运算 的n倍(狭义)

(2)(广义)含义

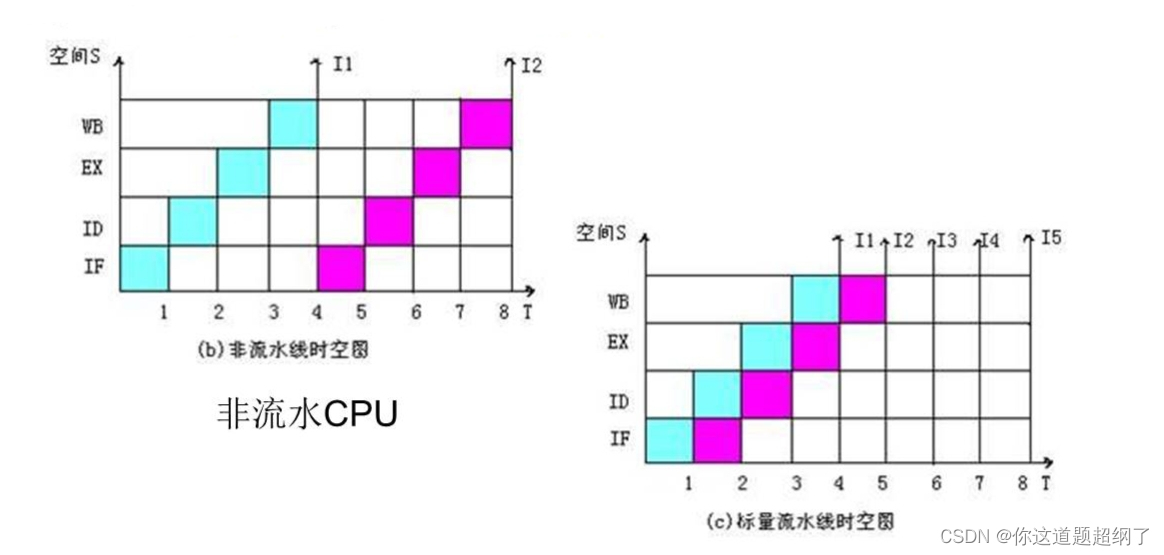

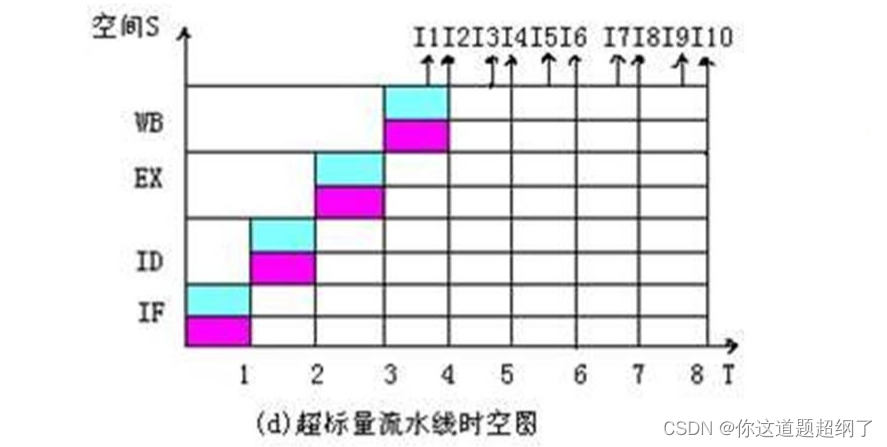

只要在同一时刻(同时性)或在同一时间间隔 内(并发性)完成两种或两种以上性质相同或 不同的工作,他们在时间上相互重叠,都体现了并行性 (3)三种形式 ①时间并行(重叠):让多个处理过程在时间上相互错开,轮流使用同一套硬件设备的各个部件,以加快硬件周转而赢得速度,实现方式就是采用流水处理部件 ②空间并行(资源重复):以数量取胜它能真正的体现同时性LSI和VLSI为其提供了技术保证 ③时间+空间并Pentium中采用了超标量流水线技术 2、流水CPU的结构  流水计算机的系统组成

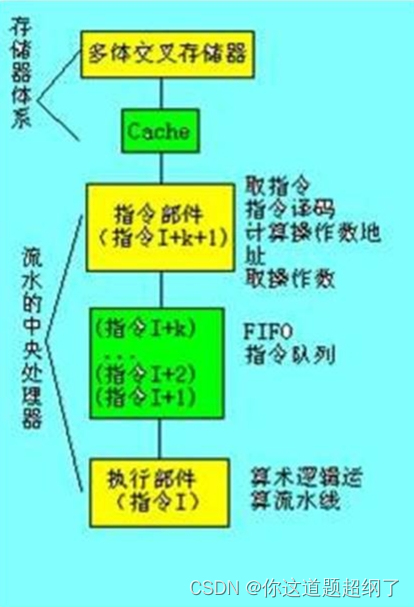

流水计算机的系统组成

存储器体系:主存采用多体交叉存 储器;Cache

流水方式CPU:指令部件、指令队 列、执行部件

指令流水线

指令队列:FIFO

执行部件:可以有多个采用流水 线方式构成的算术逻辑部件构成, 可以将定点运算部件和浮点运算部件分开。

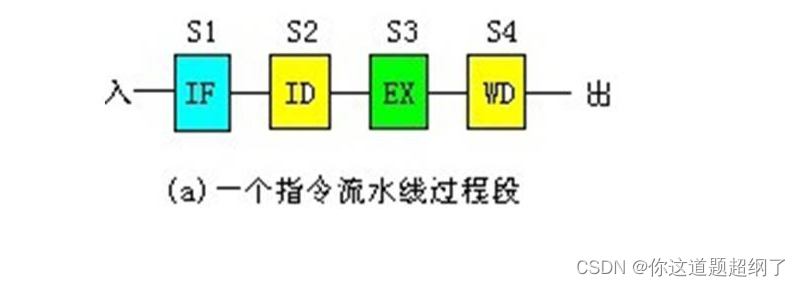

流水线CPU时空图

IF(Instruction Fetch取指)

ID(Instruction Decode指令译码) EX(Execution执行)

WB(Write Back写回)

具有两条以上的指令流水线

具有两条以上的指令流水线

●上图中流水线满载时,每一个时钟周期可以执行2条指令 ●采用时间和空间并行技术 流水线(Pipelining)的分类按级别分为:

指令流水线

算术流水线

处理机流水线(宏流水线) 3、流水线中的主要问题

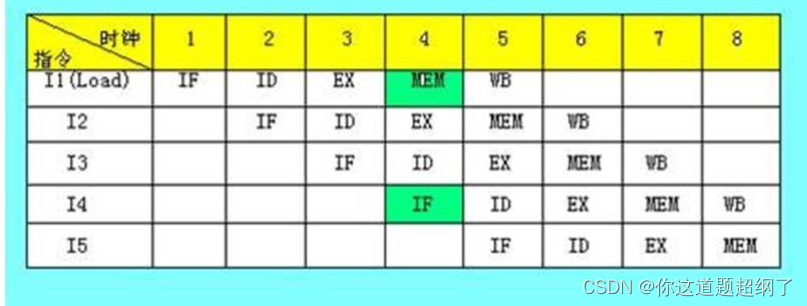

三种相关冲突:资源相关、数据相关、控制相关

①资源相关:多条指令进入流水线后在同一时钟周期内争用同一功能部件。

解决办法:后边指令拖一拍再推进;增设一个功能部件 ②数据相关

②数据相关

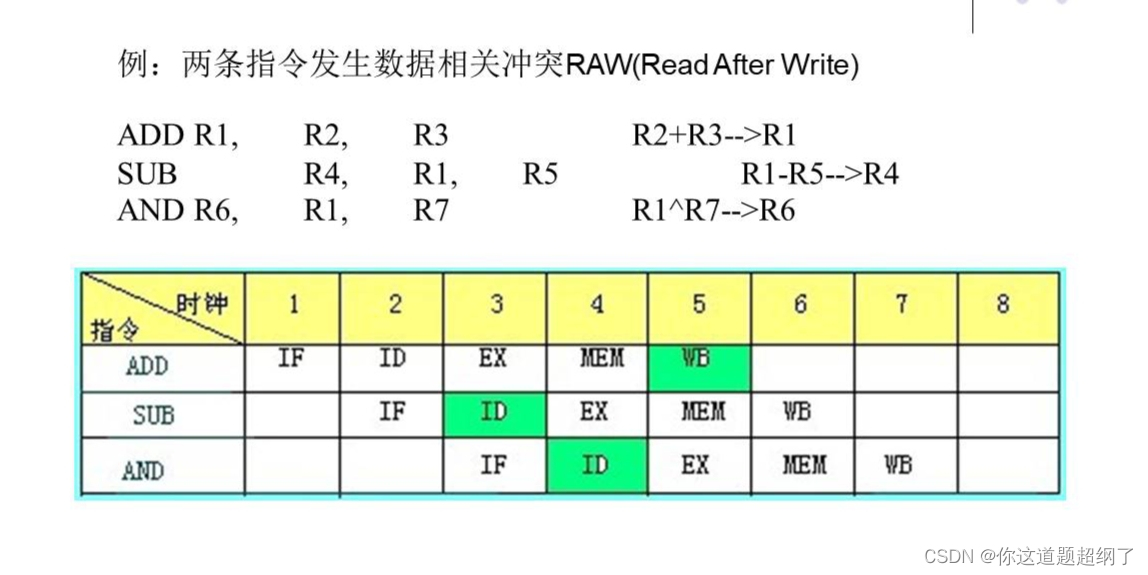

RAW(Read After Write)

后面指令用到前面指令所写的数据

WAW(Write After Write)

两条指令写同一个单元

在简单流水线中没有此类相关,因为不会乱序执行 WAR(Write After Read)

后面指令覆盖前面指令所读的单元

在简单流水线中没有此类相关

解决办法:

可以推后后继指令对相关单元的读操作

设置相关的直接通路(Forwarding) ③控制相关

③控制相关

引起原因:转移指令

解决办法:延迟转移法,转移预测法

1272

1272

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?