使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表

电路图如下:

真值表:

采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图

代码如下:

module decoder3_8

2 (

3 input wire in1 , //输入信号 in1

4 input wire in2 , //输入信号 in2

5 input wire in3 , //输入信号 in3

6

7 output reg [7:0] out //输出信号 out

8 );

9

10 //out:根据 3 个输入信号选择输出对应的 8bit out 信号

11 always@(*)

12 //使用"{}"位拼接符将 3 个 1bit 数据按照顺序拼成一个 3bit 数据

13 if({in1, in2, in3} == 3'b000)

14 out = 8'b0000_0001;

15 else if({in1, in2, in3} == 3'b001)

16 out = 8'b0000_0010;

17 else if({in1, in2, in3} == 3'b010)

18 out = 8'b0000_0100;

19 else if({in1, in2, in3} == 3'b011)

20 out = 8'b0000_1000;

21 else if({in1, in2, in3} == 3'b100)

22 out = 8'b0001_0000;

23 else if({in1, in2, in3} == 3'b101)

24 out = 8'b0010_0000;

25 else if({in1, in2, in3} == 3'b110)

26 out = 8'b0100_0000;

27 else if({in1, in2, in3} == 3'b111)

28 out = 8'b1000_0000;

29 else

30 //最后一个 else 对应的 if 中的条件只有一种情况,还可能产生以上另外的 7 种情况

31 //如果不加这个 else 综合器会把不符合该 if 中条件的上面另外 7 种情况都考虑进去

32 //会产生大量的冗余逻辑并产生 latch(锁存器),所以在组合逻辑中最后一个 if

33 //后一定要加上 else,并任意指定一种确定的输出情况

34 out = 8'b0000_0001;

35endmodule

电路图如下:

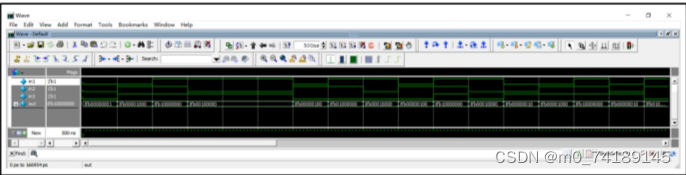

对其进行仿真

回答问题

1.Verilog综合生成的电路是由逻辑门和触发器等基本元件组成的,而logisim设计电路则是由逻辑门和连线等基本元件组成的。仿真测试生成的结果与真值表相一致。

2.在 Verilog 中,reg 变量用于存储时序逻辑的状态信息,而 wire 变量用于传递组合逻辑的输出信号。在 3-8 译码器中,我们需要使用 reg 型变量来存储输出信号的状态,因为它们的值会随着时钟信号的变化而改变。换句话说,由于 3-8 译码器是一个时序电路,其输出信号是根据时钟信号和输入信号进行计算的。因此,我们需要使用 reg 型变量来存储输出信号的状态。如果我们将输出信号定义为 wire 型变量,则编译器将其解释为组合逻辑,从而导致输出信号无法随着时钟信号的变化而改变。所以,改为 wire 型变量并不可行,会导致设计出错。在设计时序电路时,我们通常使用 reg 来存储状态信息,而使用 wire 来传递输出信号。

verilog的门级描述

在logsim中的1位全加器:

用verilog来完成

采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器

代码:

module add_1_m (a,b,cin,cout,sum);

input a,b;

input cin;

output cout;

output sum;

wire [2:0] w;

and

a1(w[0],a,cin),

a2(w[1],a,b),

a3(w[2],b,cin);

xor a4(sum,a,b,cin);

or a5(cout,w[0],w[1],w[2]);

endmodule

//use add_1_m connect to add_4

module add_4_m (a,b,cin,cout,sum);

input [3:0] a,b;

input cin;

output cout;

output [3:0] sum;

wire [3:1] c;

add_1_m u1 (a[0],b[0],cin,c[1],sum[0]);

add_1_m u2 (a[1],b[1],c[1],c[2],sum[1]);

add_1_m u3 (a[2],b[2],c[2],c[3],sum[2]);

add_1_m u4 (a[3],b[3],c[3],cout,sum[3]);

endmodule

采用Verilog的行为级方式

1位

module adder_dataflow1(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

wire t1,t2,t3;

assign sum=a^b^cin;

assign t1=a&b;

assign t2=a&cin;

assign t3=b&cin;

assign cout=t1|t2|t3;

endmodule

4位

module adder1 (

input A, B, Cin,

output Sum, Cout

);

assign {Cout, Sum} = A + B + Cin;

endmodule

module adder4

(

input [3:0]A,B,

input cin,

output [3:0]sum,

output cout

);

wire[4:0]c;

assign c[0] = cin;

adder1 adder10(A[0],B[0],c[0],sum[0],c[1]);

adder1 adder11(A[1],B[1],c[1],sum[1],c[2]);

adder1 adder12(A[2],B[2],c[2],sum[2],c[3]);

adder1 adder13(A[3],B[3],c[3],sum[3],c[4]);

assign cout = c[4];

endmodule

1543

1543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?