(本文整理自B站up主:ele实验室)

模拟电路部分

在了解基本电路的原理基础上理解电子管(上过初中高中并学过物理和化学):

电子管

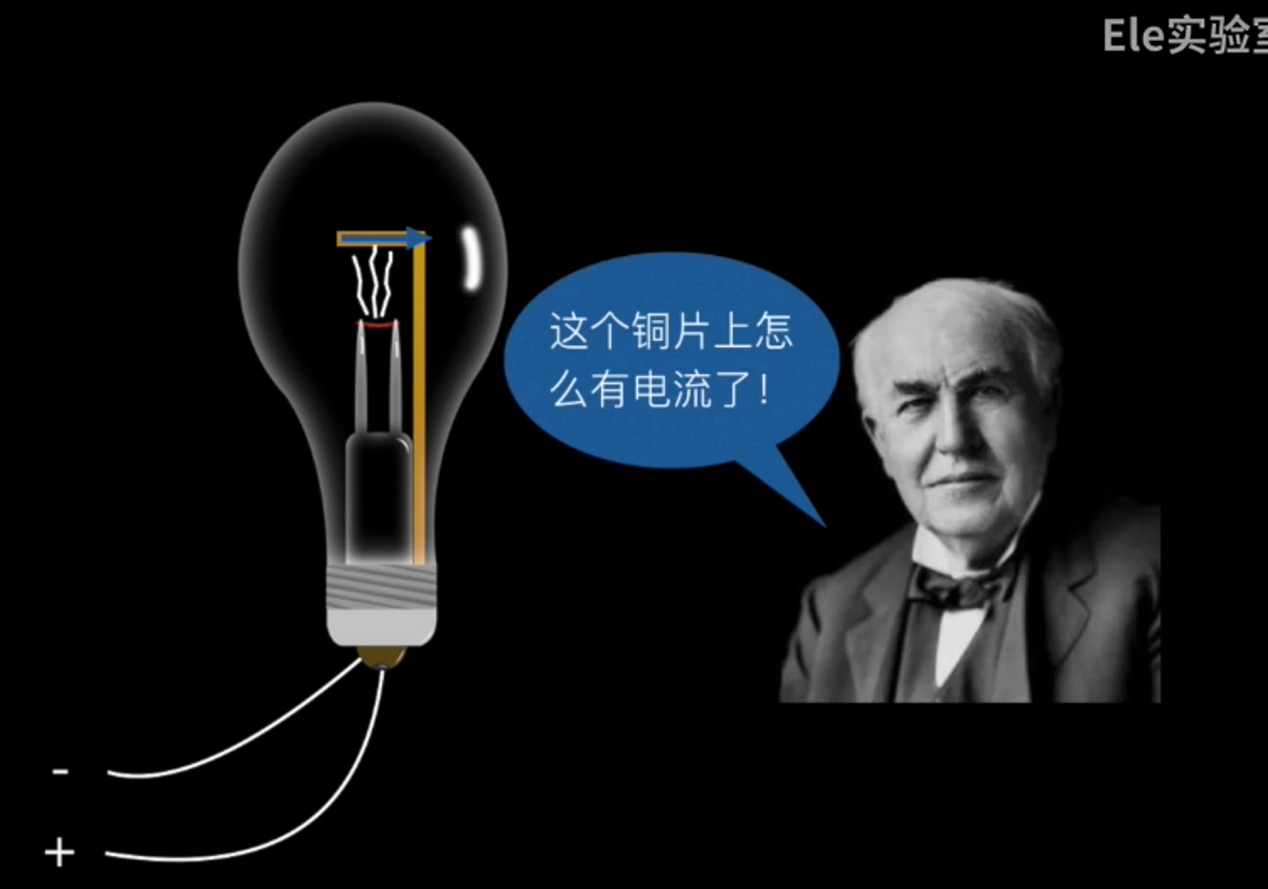

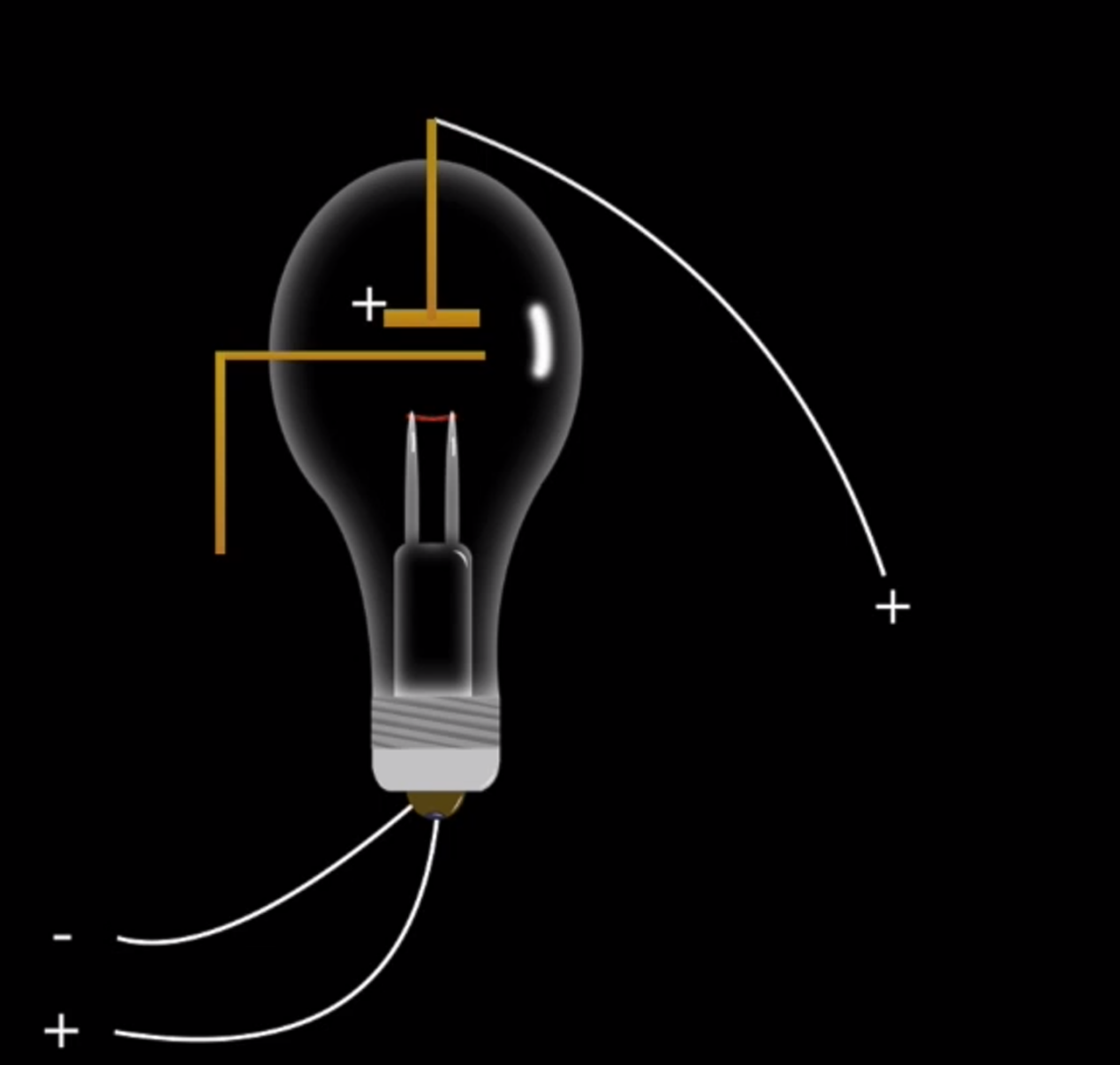

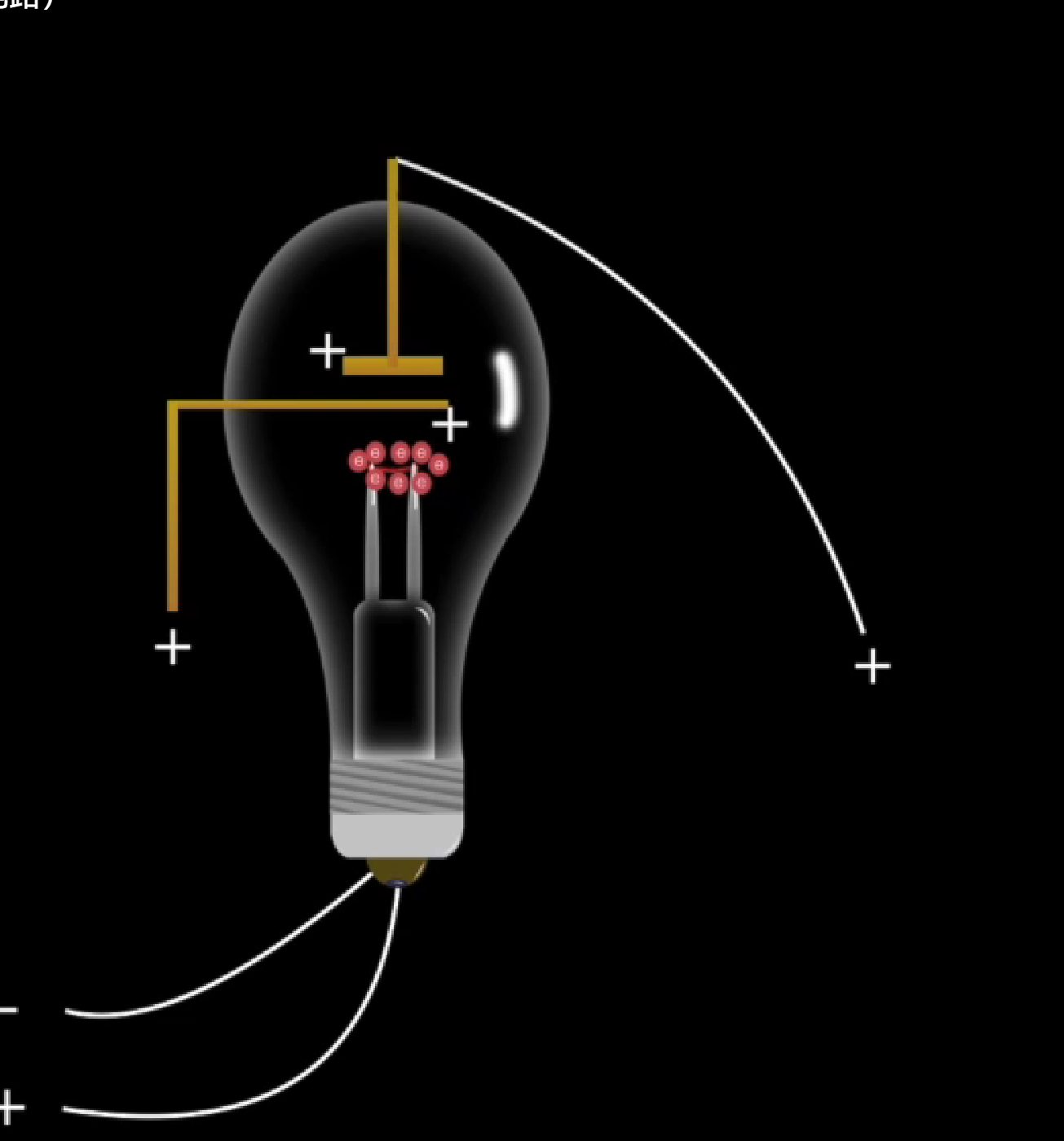

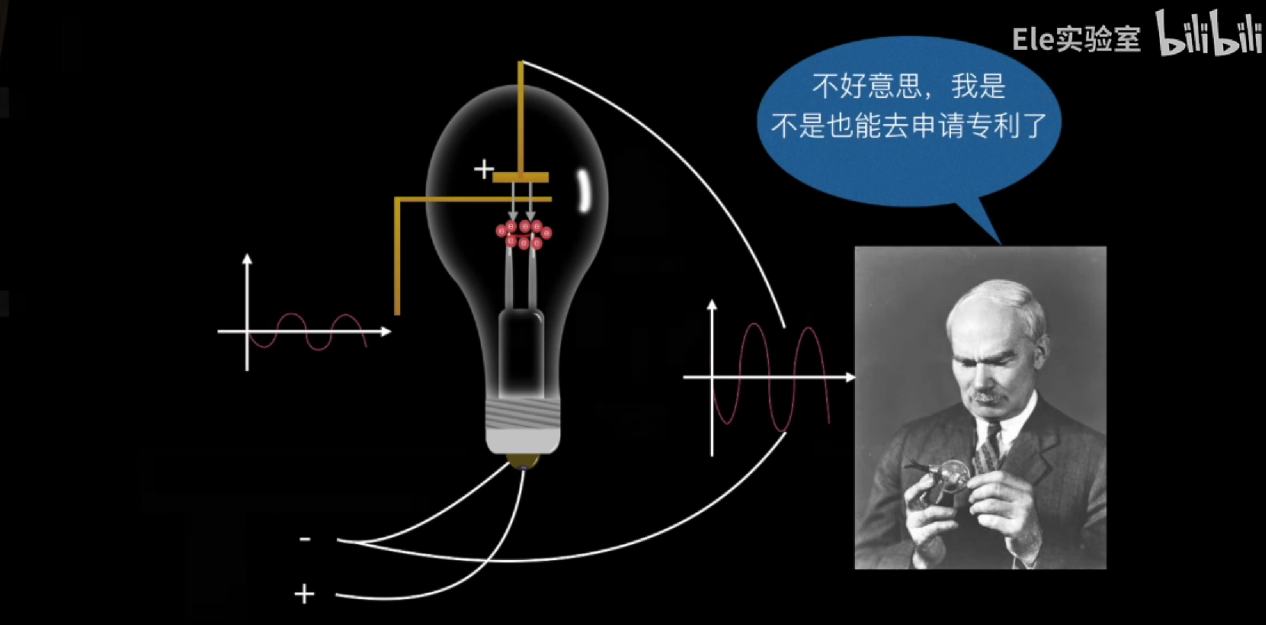

爱迪生效应的发现:在19世纪末期,当爱迪生正在研究电灯泡的时候,他注意到了一个现象:在一个由两个金属片构成的真空空间中,如果一个金属片被加热至高温(比如灯丝),那么在两片金属之间会有一个电流产生,即使另一个金属片没有外加电压也能够吸引带电粒子(但是小爱同学未进行深入研究因为赚不到马内,只是申请了一个专利)

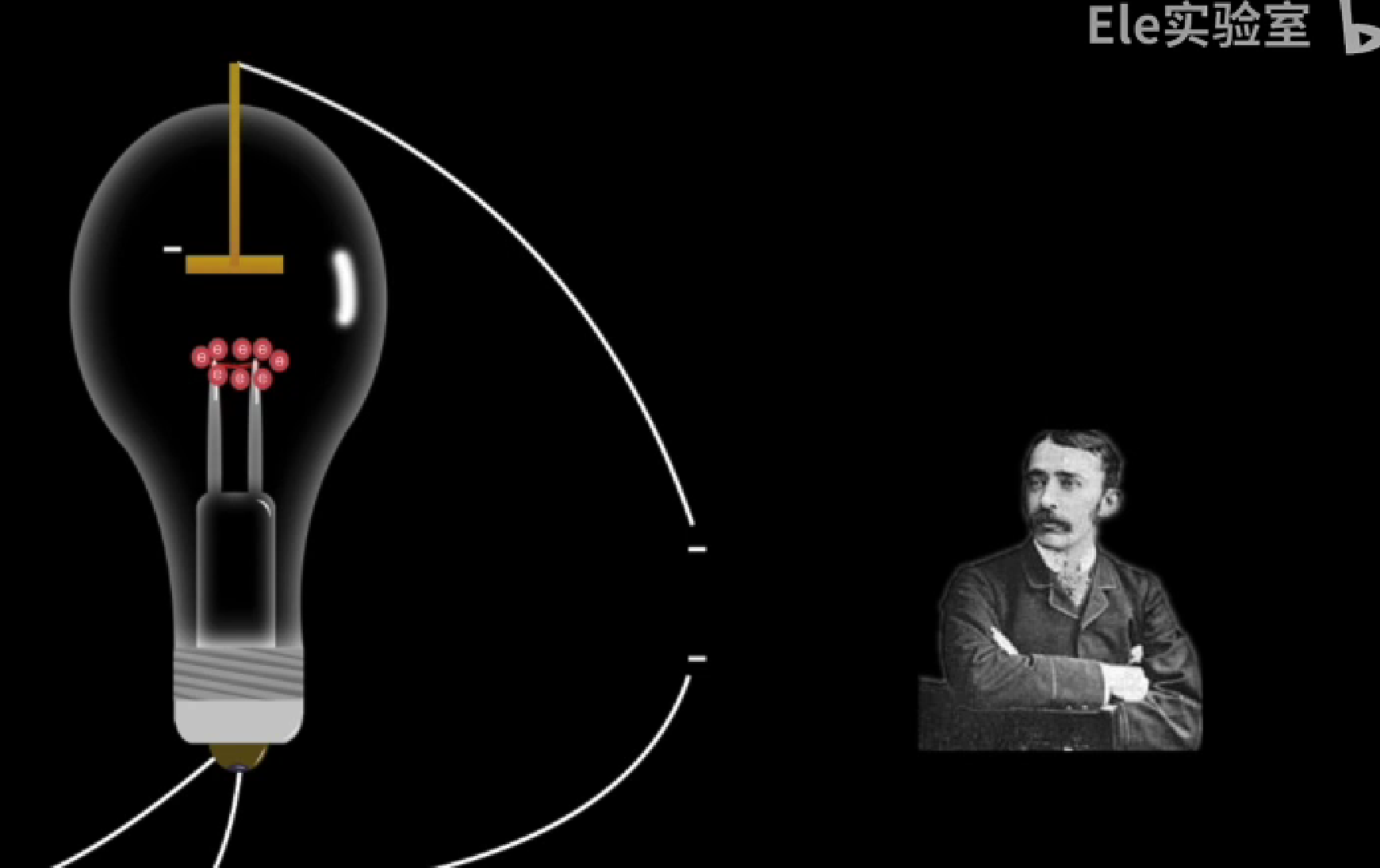

弗莱明的科学解释:这是因为热金属片发射了电子,这些电子随后可以被另一个金属片收集起来。这一发现后来成为了热电子发射的基础,并且对电子管的发展起到了重要作用。

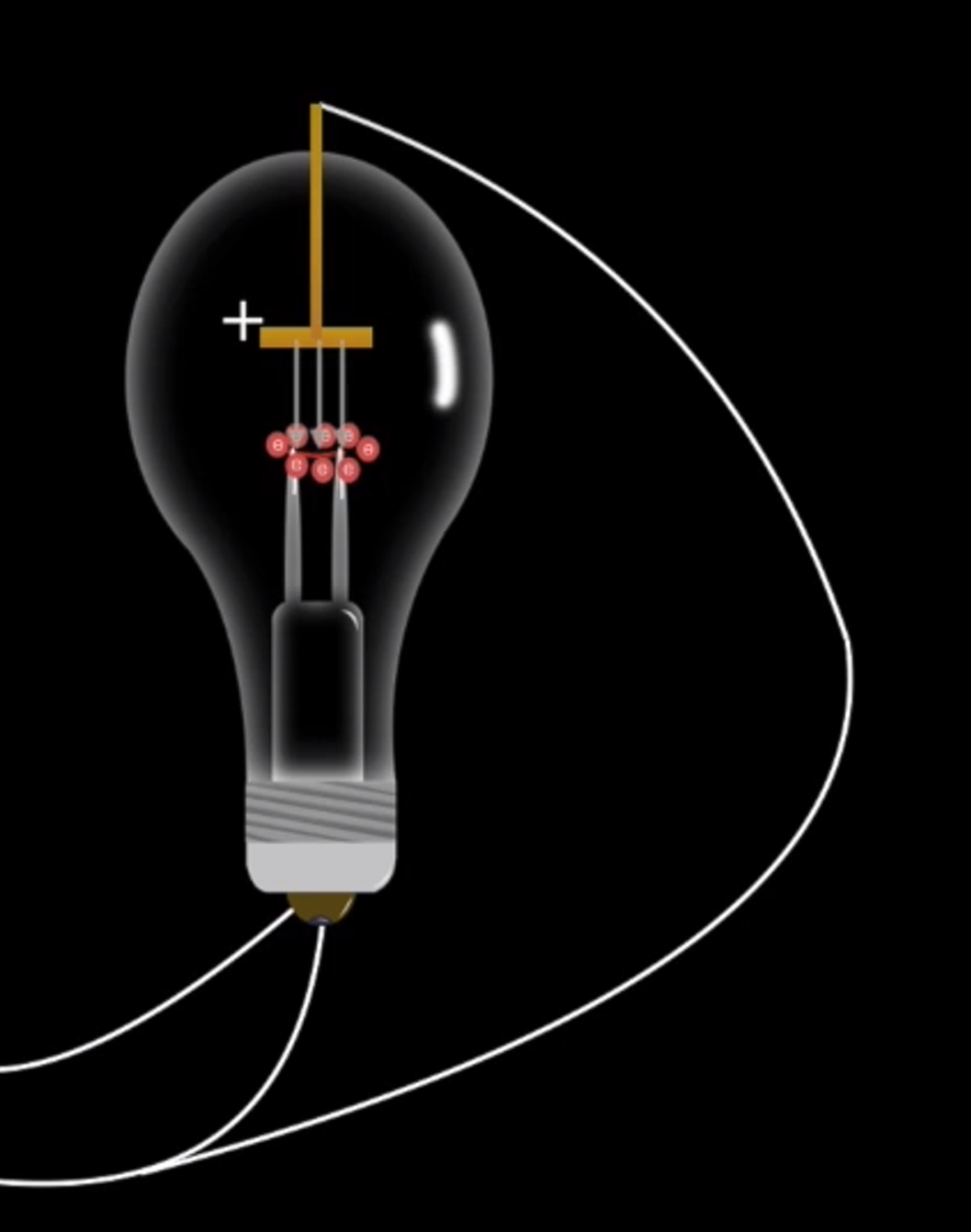

若上板带正电电子被吸引就可以形成电流:

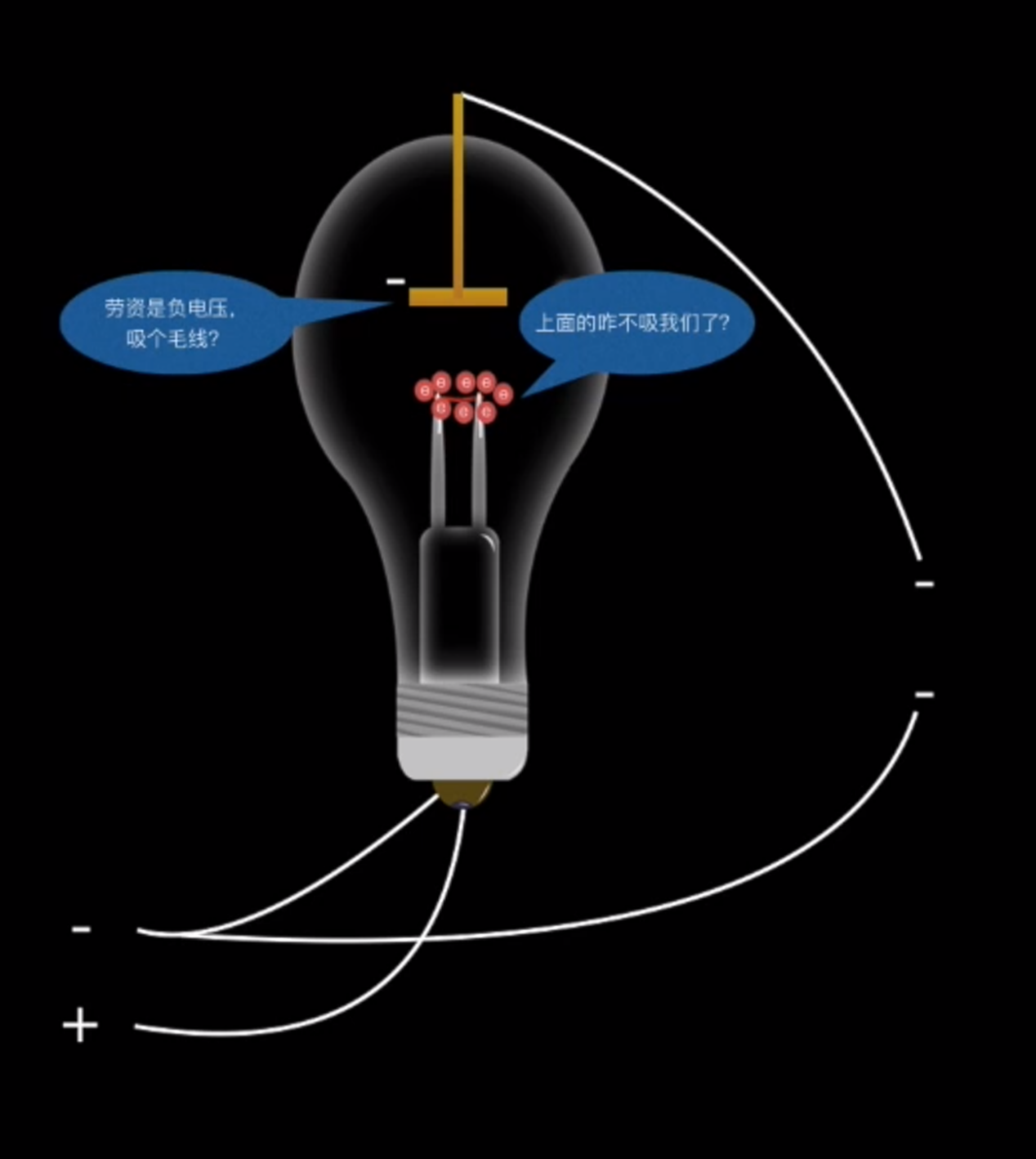

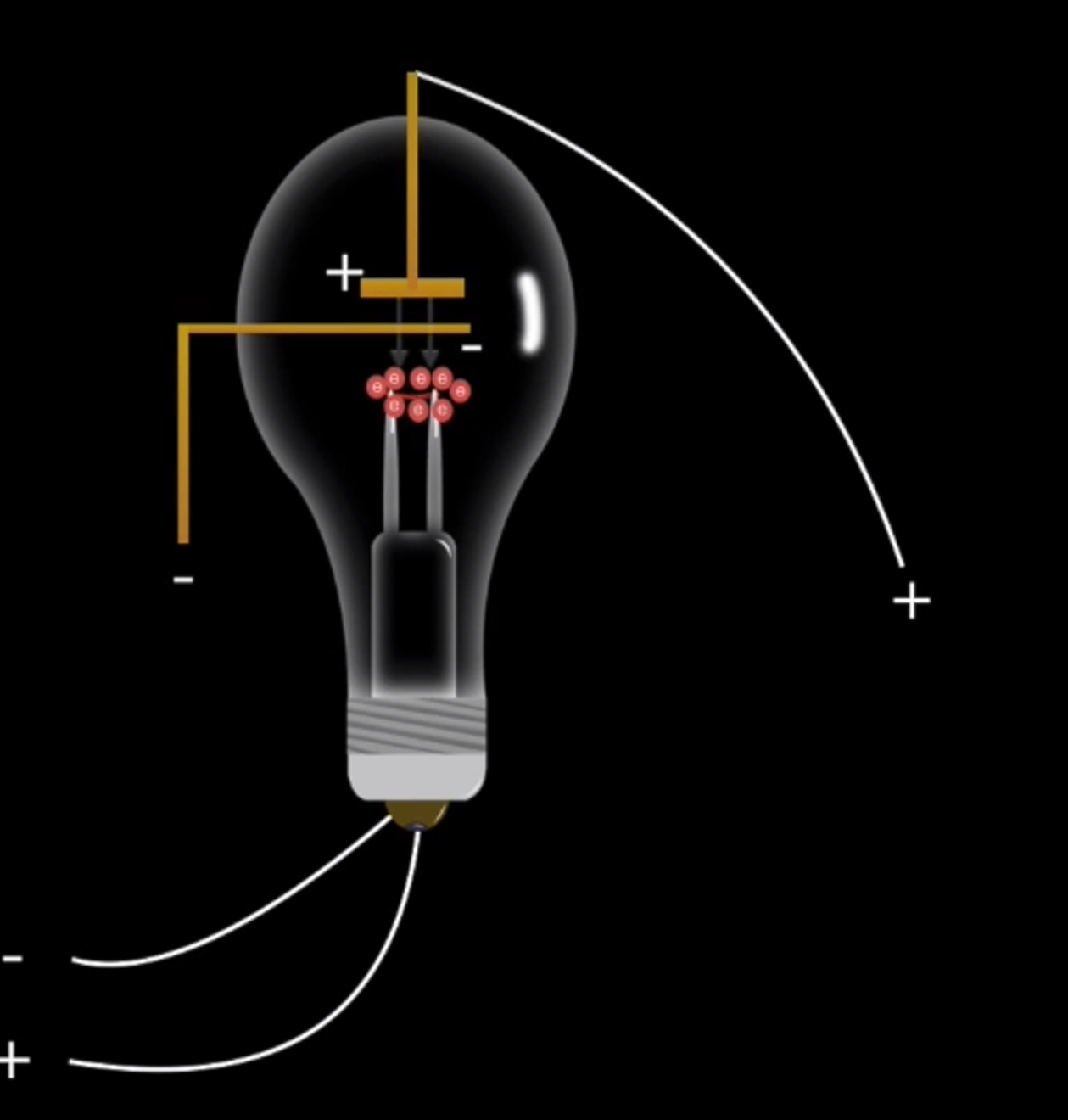

反过来上极板带负电则无法形成电流:

显然可以起到整流的作用,第一个二极管由此诞生,开启了电子工业的大门;(看来1%的灵感的确不够用啊)

李·德·弗雷斯特(搞无线电的)的改进:

第一个三极管诞生由此

第三级带正电 加强电子移动

第三个极板带负电会削弱电场

在第三极发生微小的变化,都会在上极板产生很大的变化: 可以用来放大信号。

借此李·德·弗罗斯特改进了意大利马可尼的无线电,解决了信号衰减的问题;

后来他发明了真空电子管;

电子管具有抗电磁干扰,工作温度范围广,在高端音响设备中仍有电子管的身影,也就是发烧友口中的胆机;

电子管的缺点:

-

体积大、重量重:电子管通常比晶体管更大、更重,这限制了它们在便携式或空间受限设备中的使用。

-

能耗高:电子管需要较高的电压来工作,且会消耗更多的电力,这导致效率较低。

-

寿命较短:电子管的工作寿命通常不如固态器件长,而且它们可能会因灯丝烧断或其他原因失效。

-

启动时间较长:电子管需要一段时间预热才能达到正常工作状态,这使得它们不适合需要立即响应的应用。

-

稳定性较差:电子管的性能可能会随温度变化而变化,这影响了其稳定性和可靠性。

电子管的缺点显然无法满足电子工业的需求:于是晶体管诞生了

晶体管

三位二战老兵的故事(老兵创业??)

约翰·巴丁(John Bardeen)、沃尔特·布拉顿(Walter Brattain)和威廉·肖克利(William Shockley)。他们在1947年发明了第一个点接触型晶体管,获得诺贝尔物理学奖 这一发明标志着固态电子学时代的开始,并为后来的微电子革命奠定了基础。

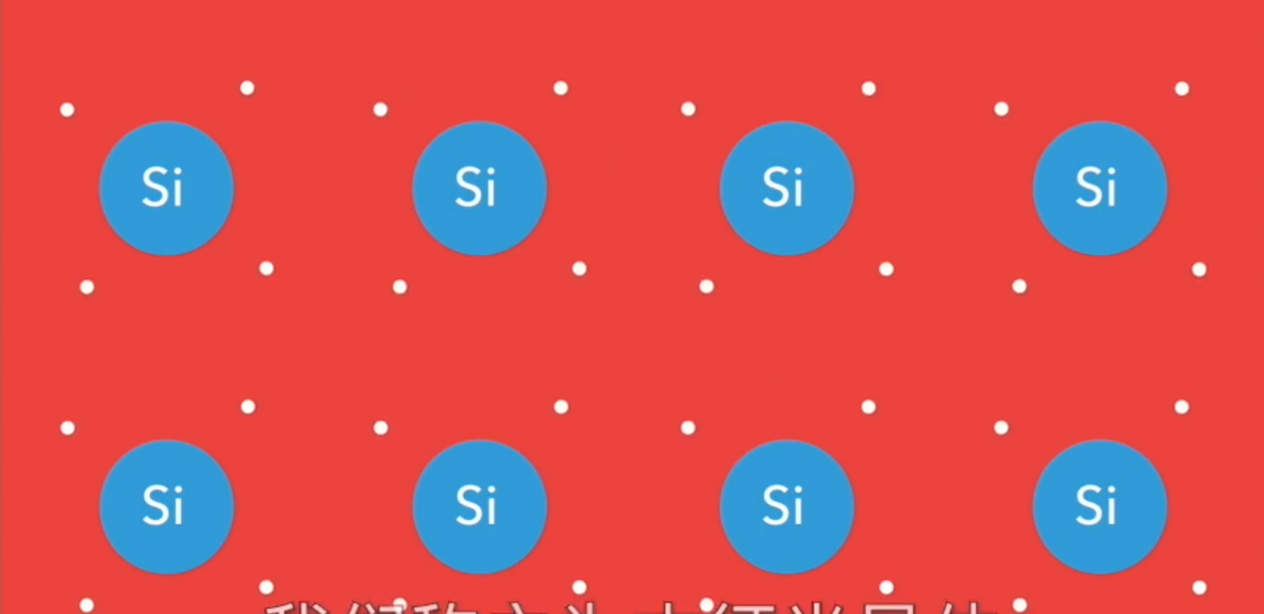

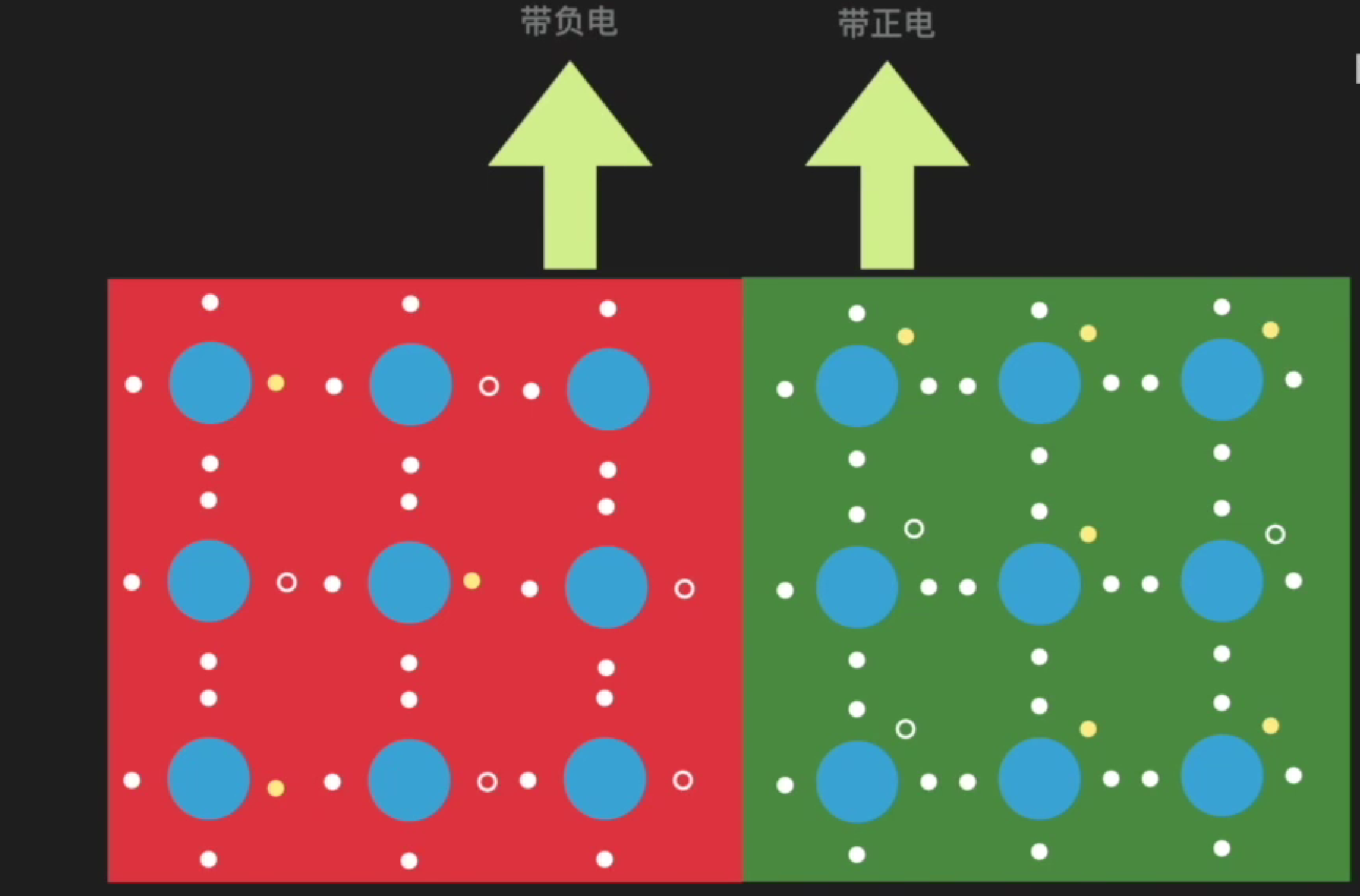

我们知道当原子核外电子小于四时容易失去电子,大于4容易得电子,当等于4时就是半导体

纯净的半导体 称为本征半导体;

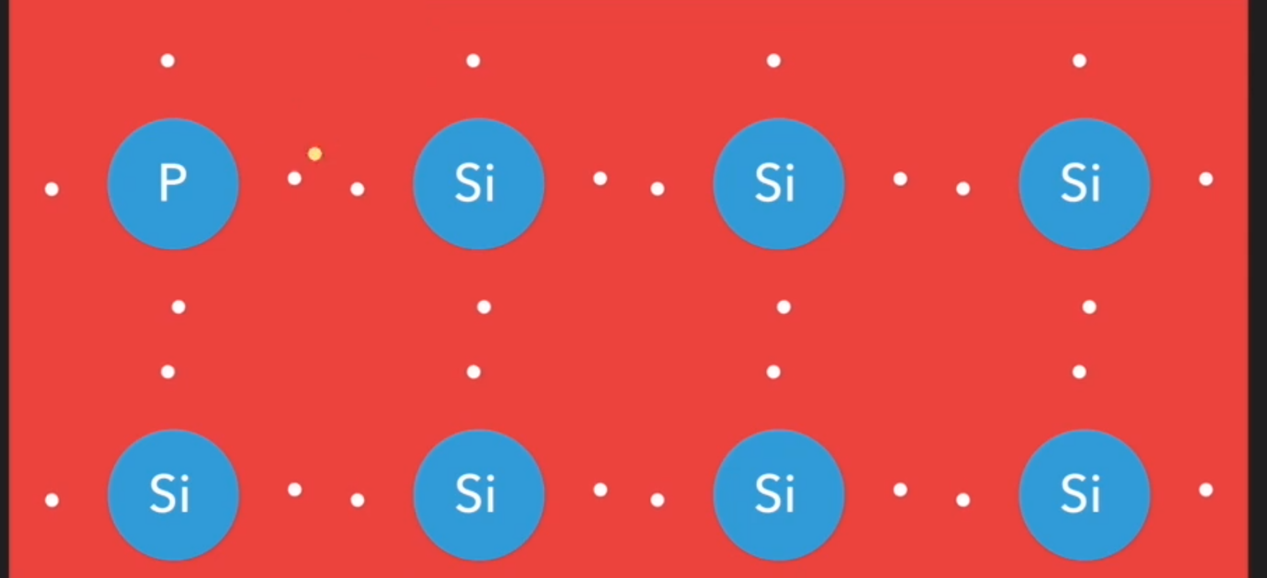

在本征半导体中掺入磷

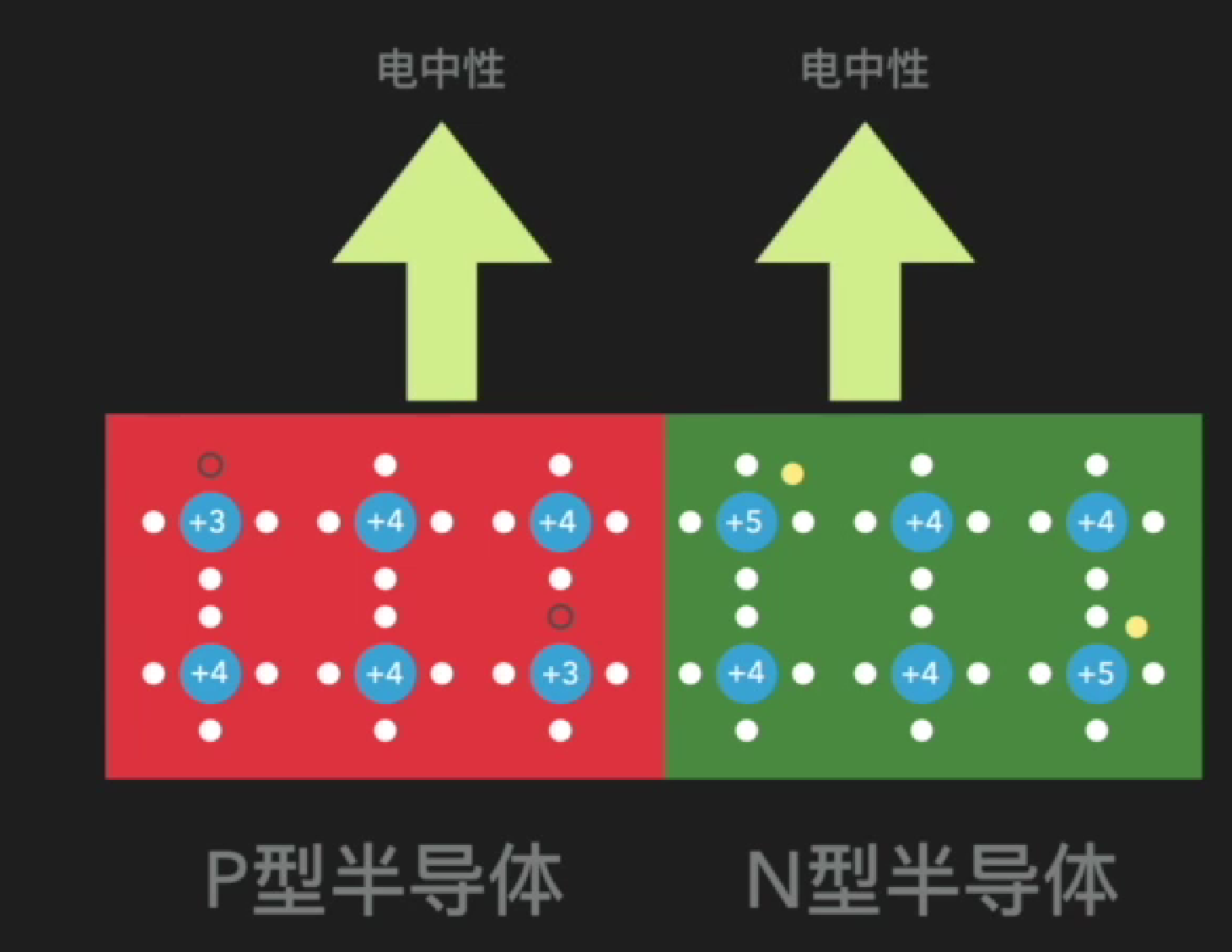

多了一个电子带负电 不如叫negative半导体吧 简称N型半导体;(需要说明这里的P/N型半导体都是电中性,命名只是便于表诉,不涉及电性)

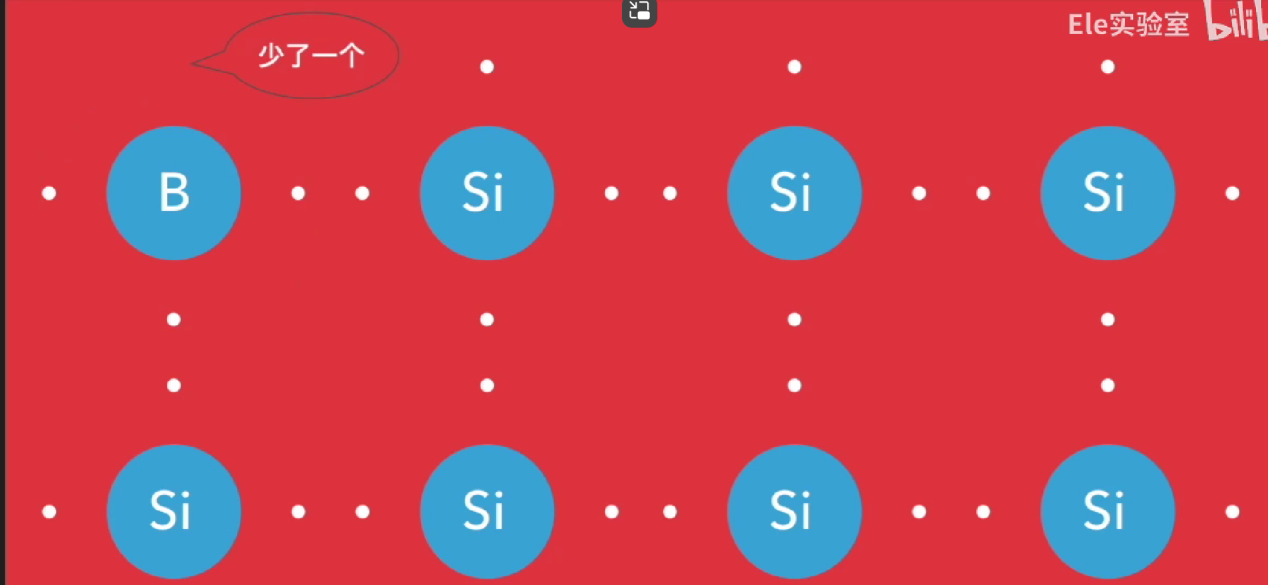

掺入硼

电子少了 就叫Positive半导体吧,简称P型半导体吧

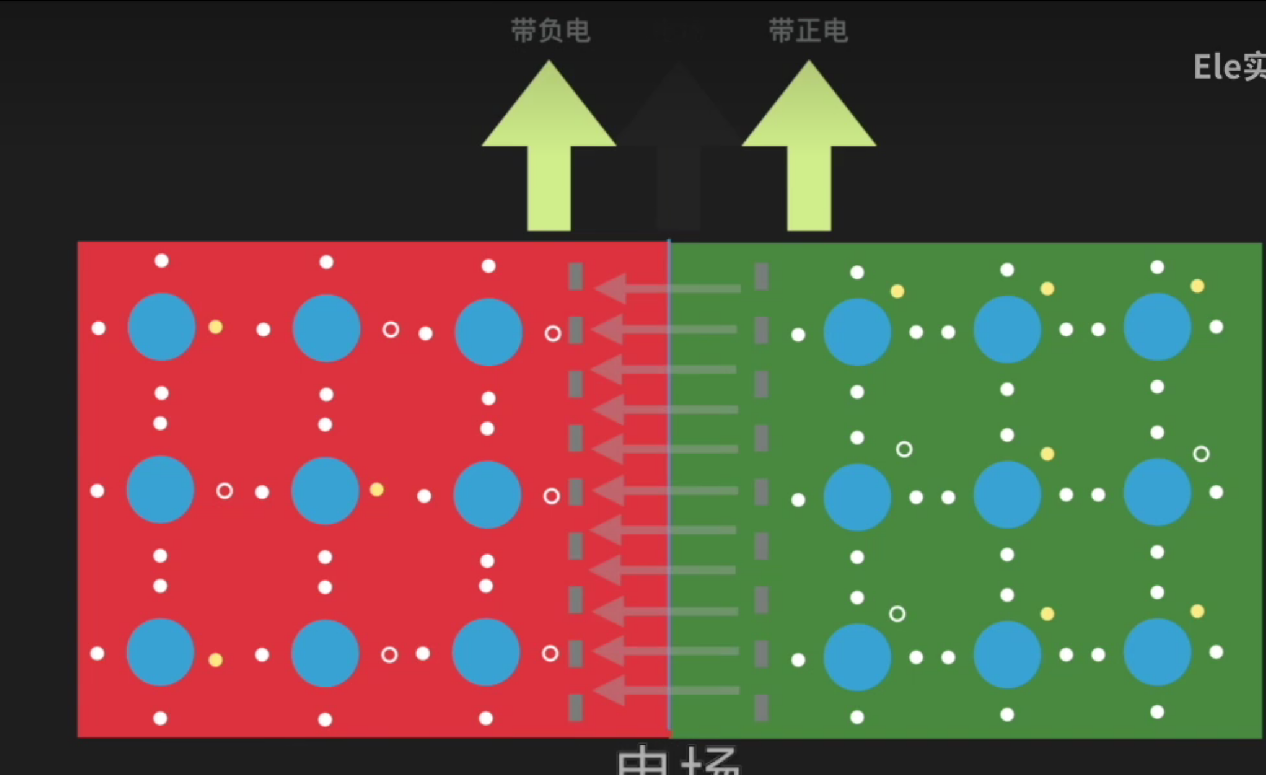

PN节

N型半导体中电子浓度高 P型半导体电子浓度低,电子会从N型半导体中跑到P型中去,

在这过程中电场建立

电场建立会约束电子的移动,会将电子往N型那边拉,称为漂移运动,然后当电子达到一定浓度电子又会向P区迁移如此往复,动态平衡 。本质上是中间电场力与质子对电子的电场力之间主次矛盾的相互转换

中间的电场区称为PN节。

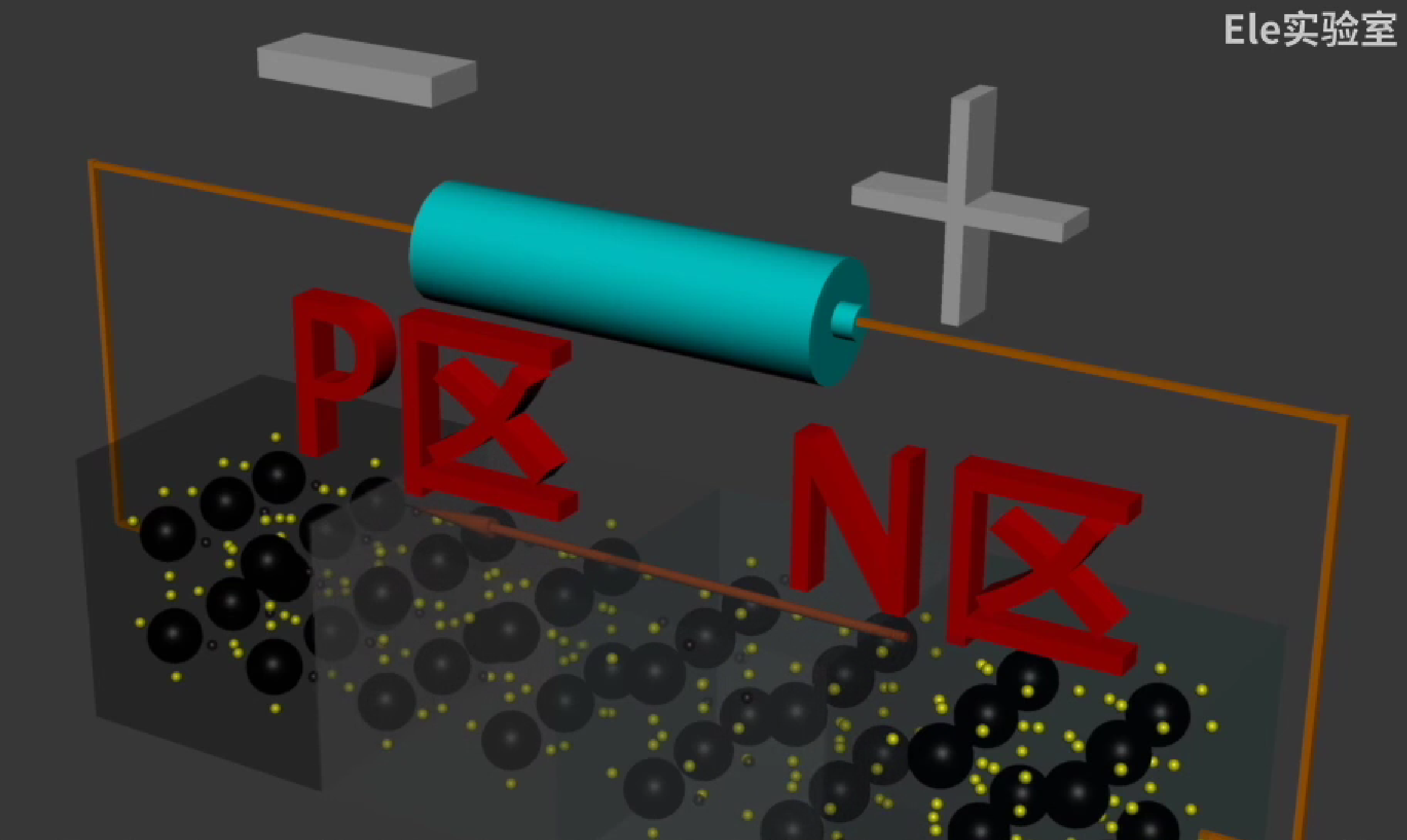

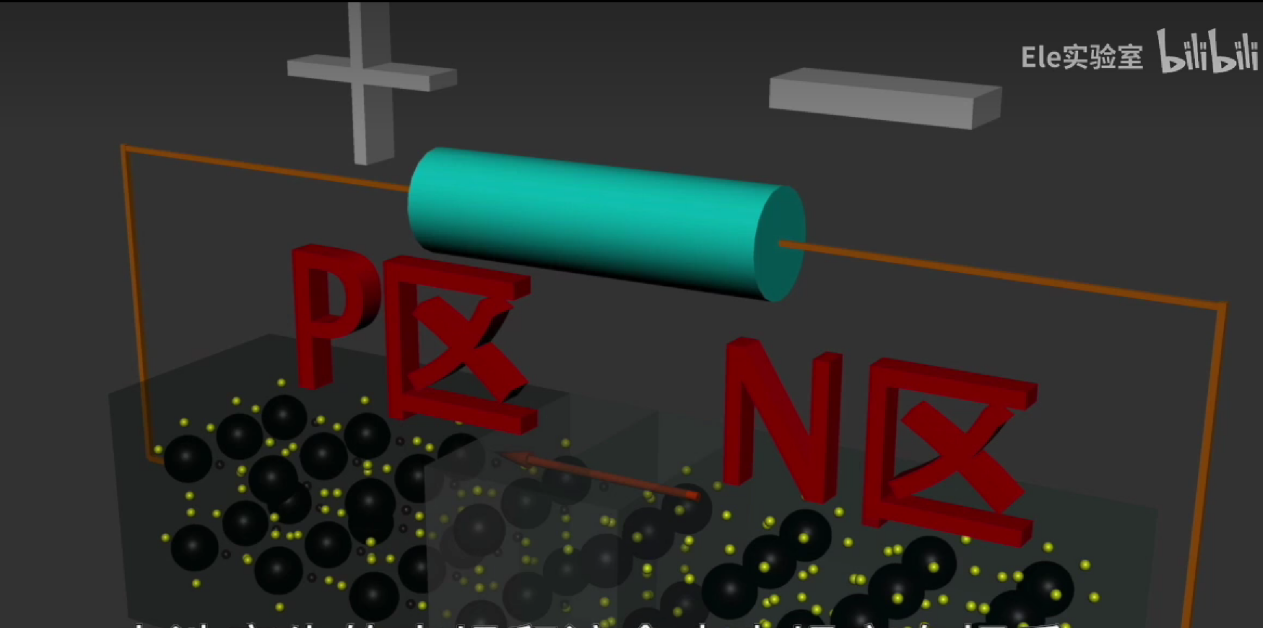

PN节的导通与截断:

当外部电源负极在P区时,电子不断被吸引,中间电场被拉长,电子无法移动,电流截断;

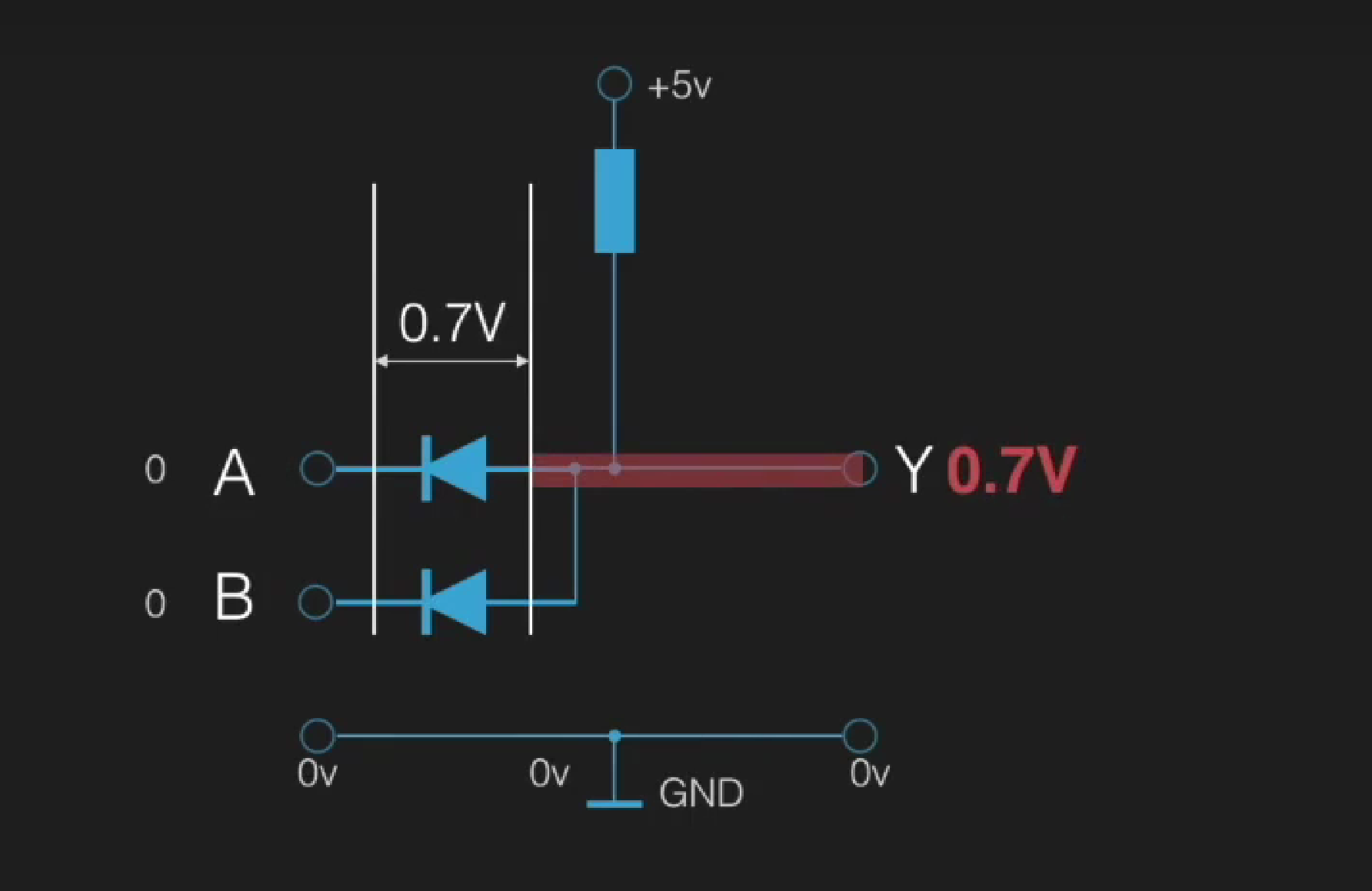

反向通电时,电子到N区,随着电子的不断累积,当达到一定值时,就可以克服内电场,电流导通 ! (晶体二极管)导通电压 硅管>=0.7v,锗管>=0.3v 晶体二极管都有晶体三级管还会吗?

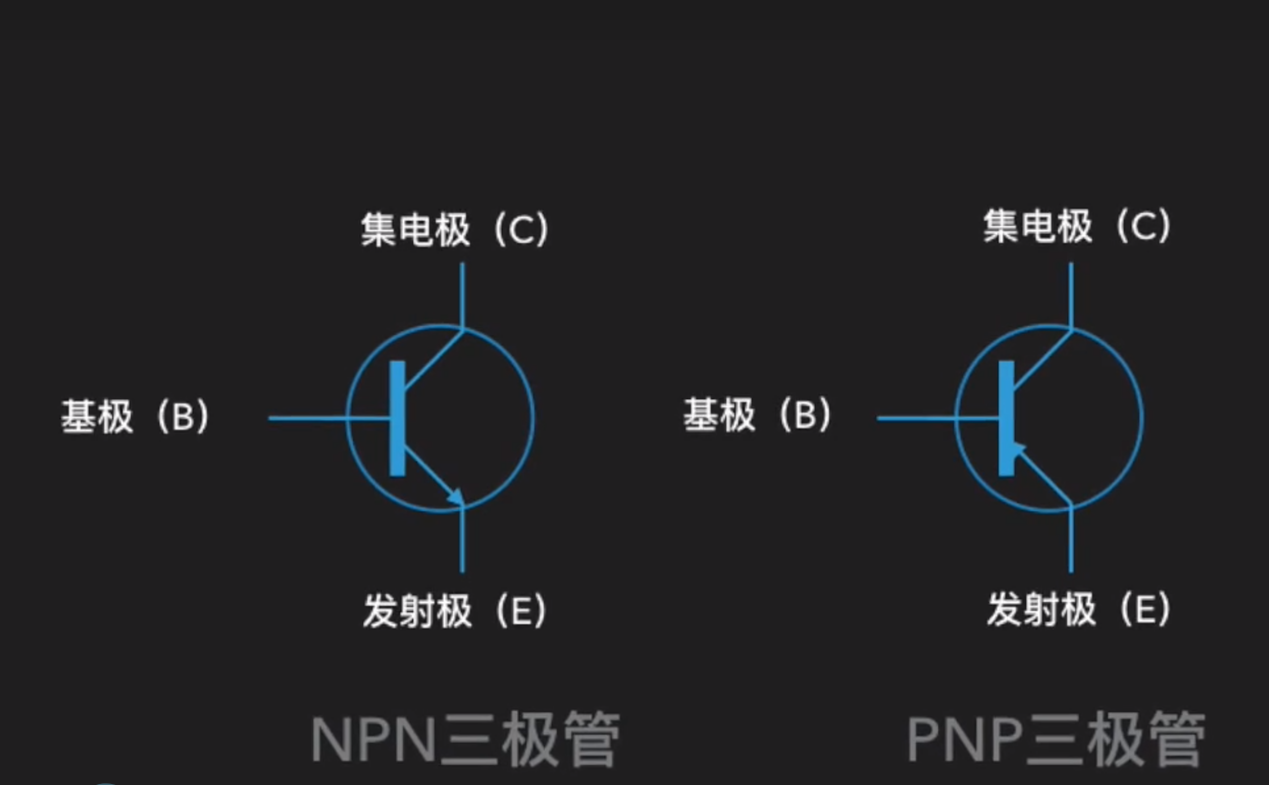

晶体三极管:

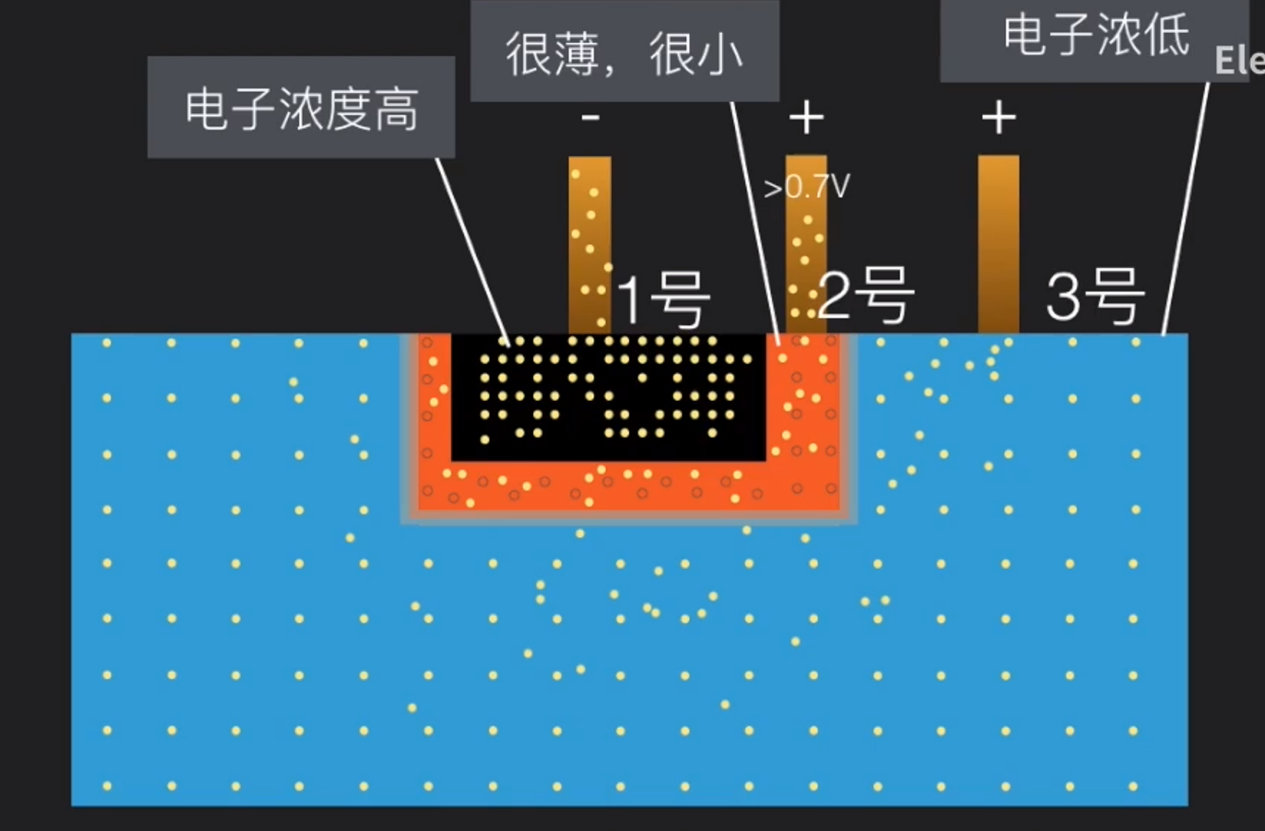

NPN型

1号区N型 边缘掺入较多P电子较多;发射电子(发射极)

2号区P型 较薄;控制一号电子流入速度(基极)

3号区N型 较厚 电子较少;收集电子(集电极)

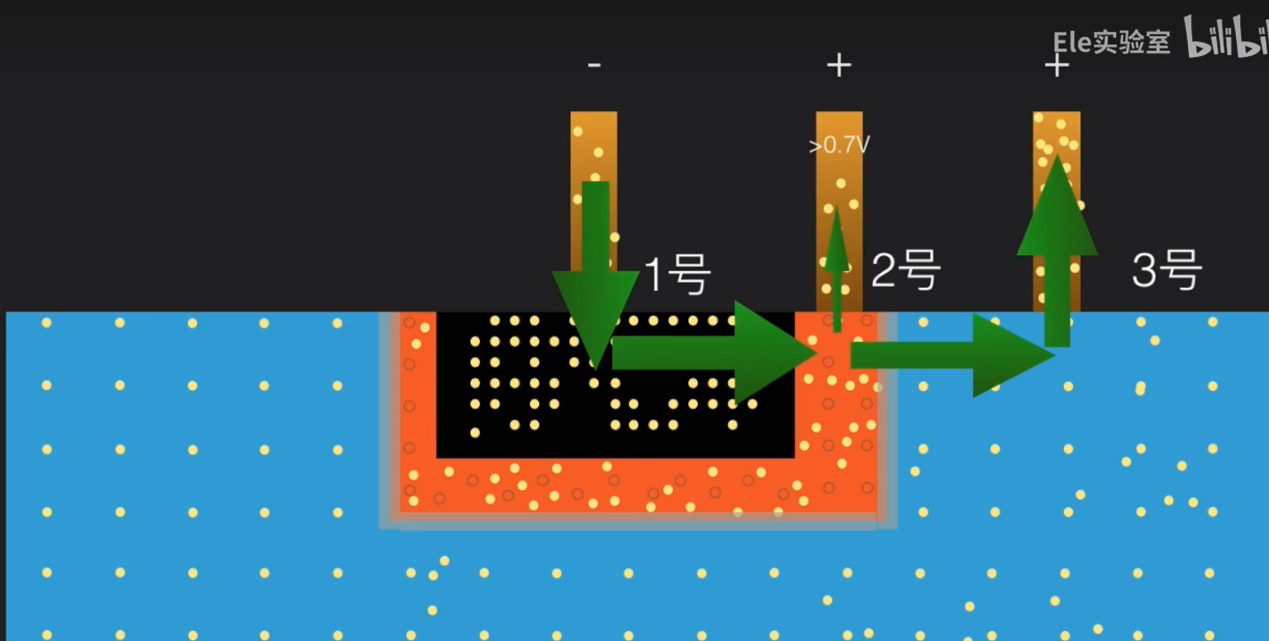

1 2号之间导通,大量电子流行2号,2号较薄,无法留住大量电子,电子涌入3号,3号接正极,电子迅速流入正极,2号与3号导通。

电子实际来源于1号,所以1,3号导通。

2号较薄消耗的电子比较少,电流小;3号,比较厚消耗电子比较多,电流大;(I=nqvs)

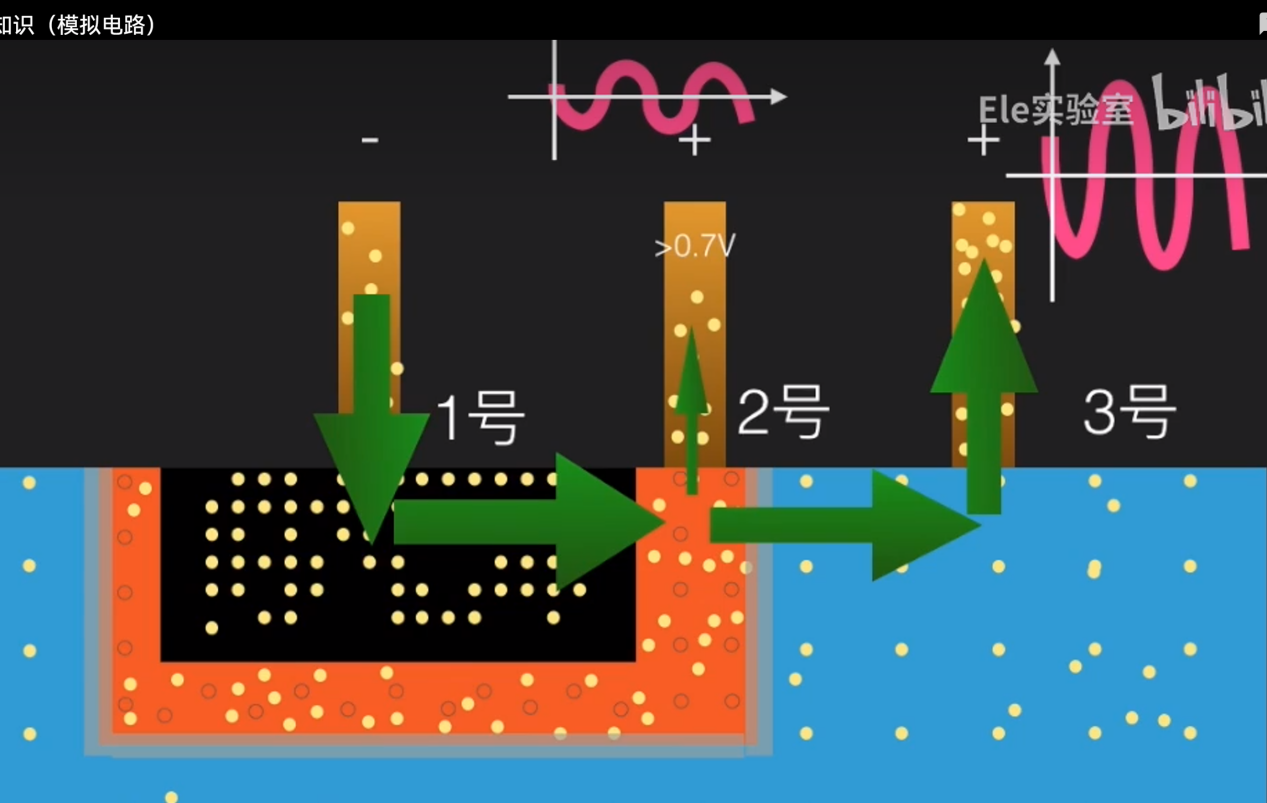

当2号有微小改变时,1号区电子流入速度就会有较大变化,从而引起电子涌入3号速度的巨大变化,从而放大信号。(晶体三极管)

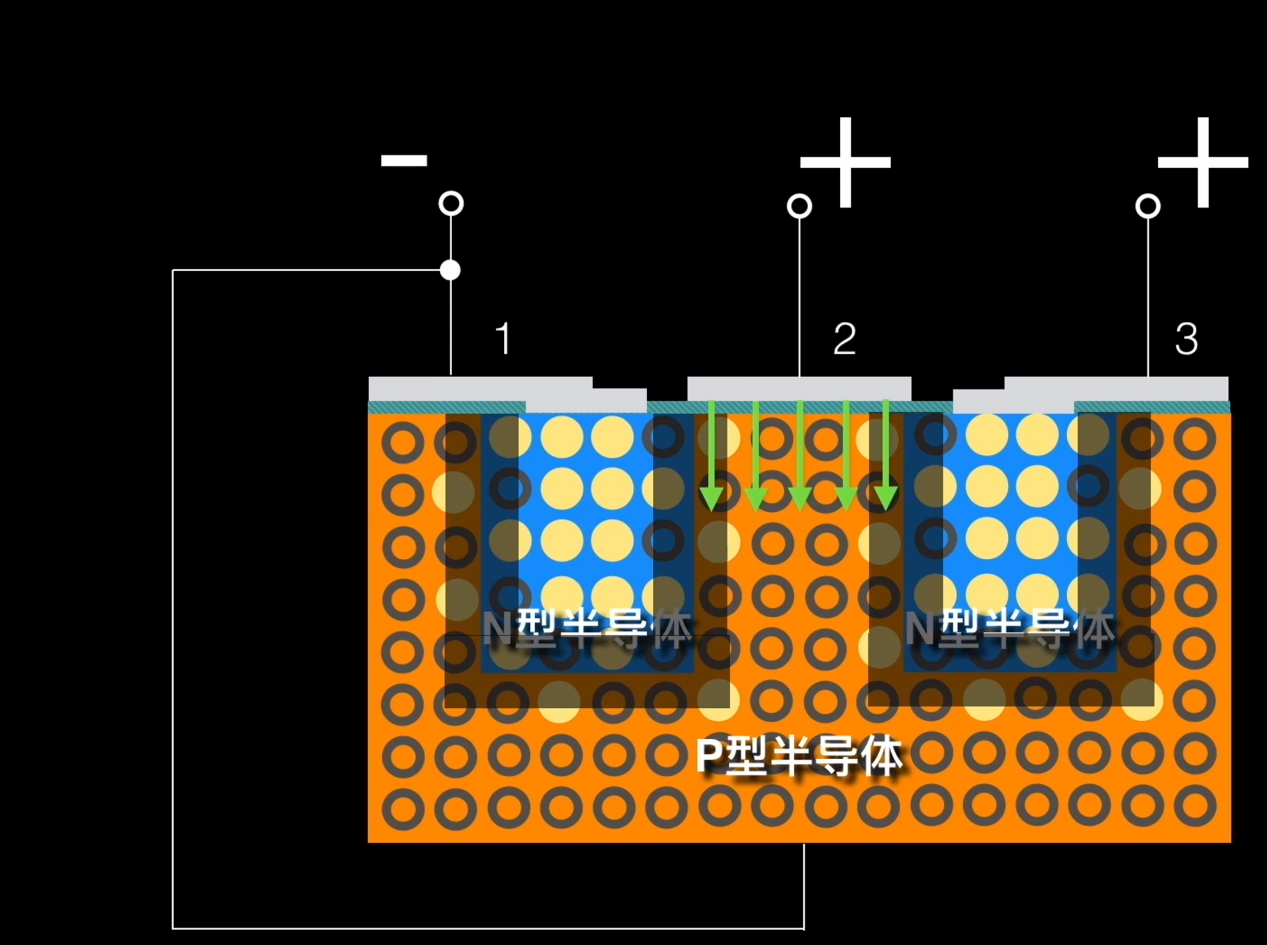

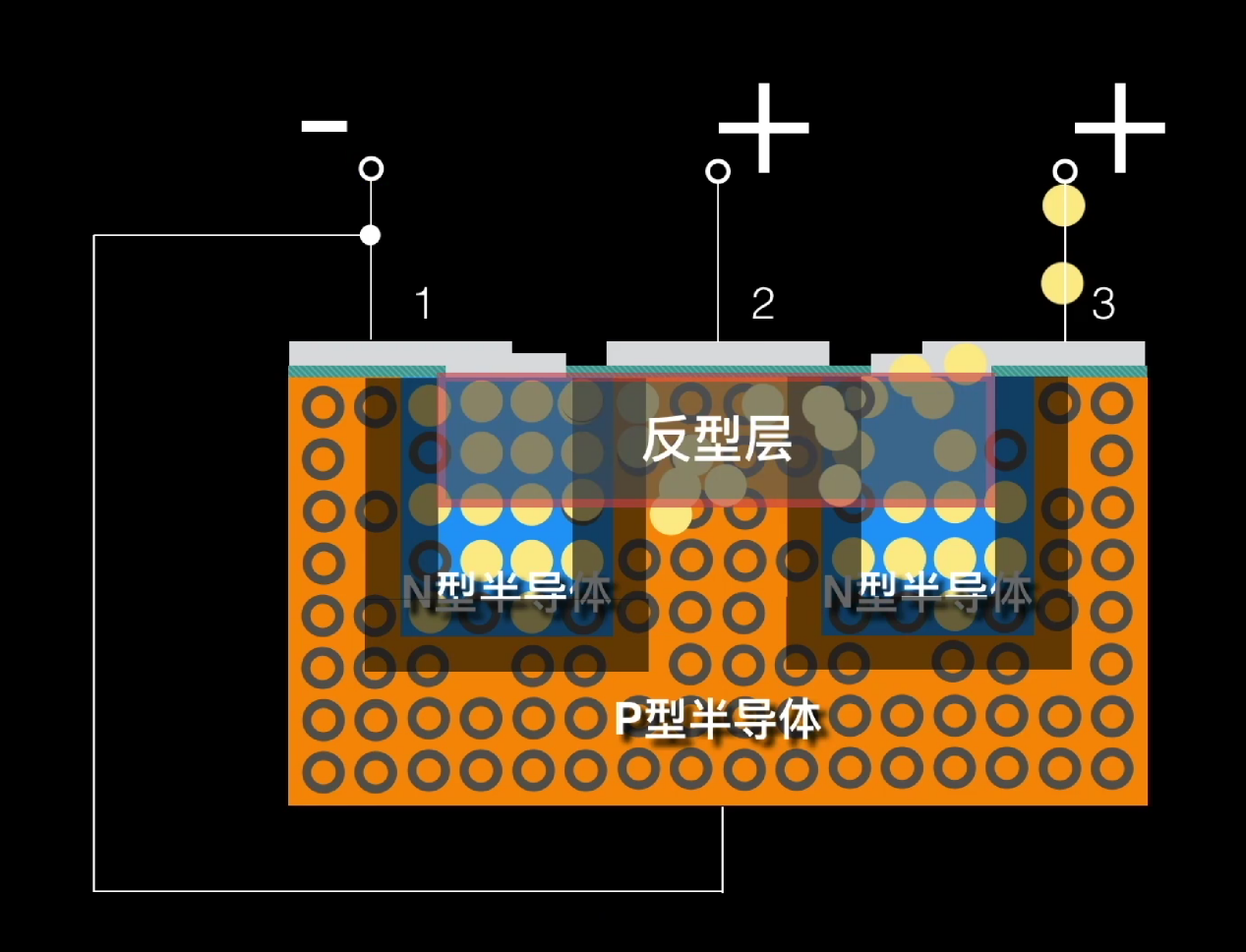

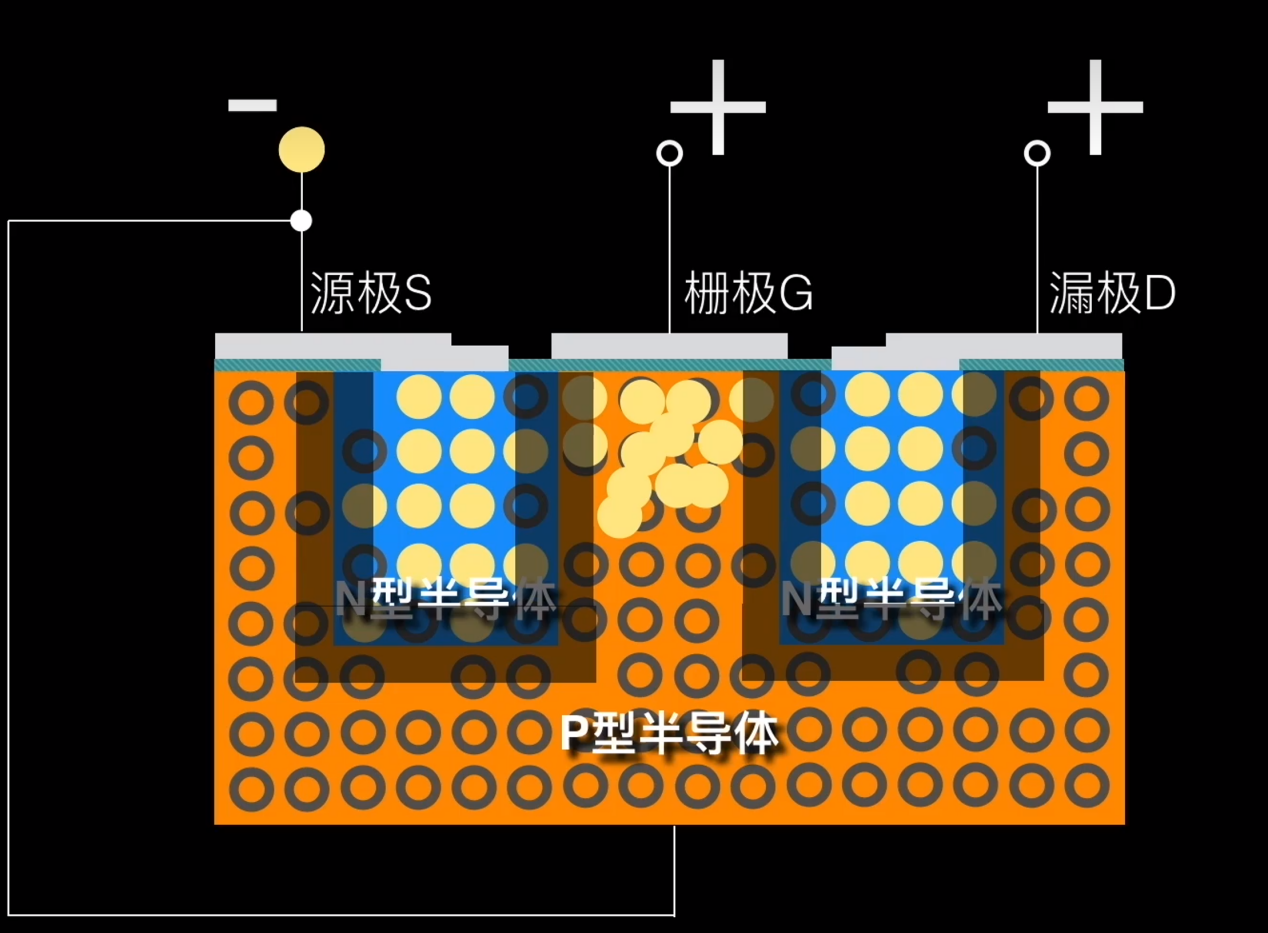

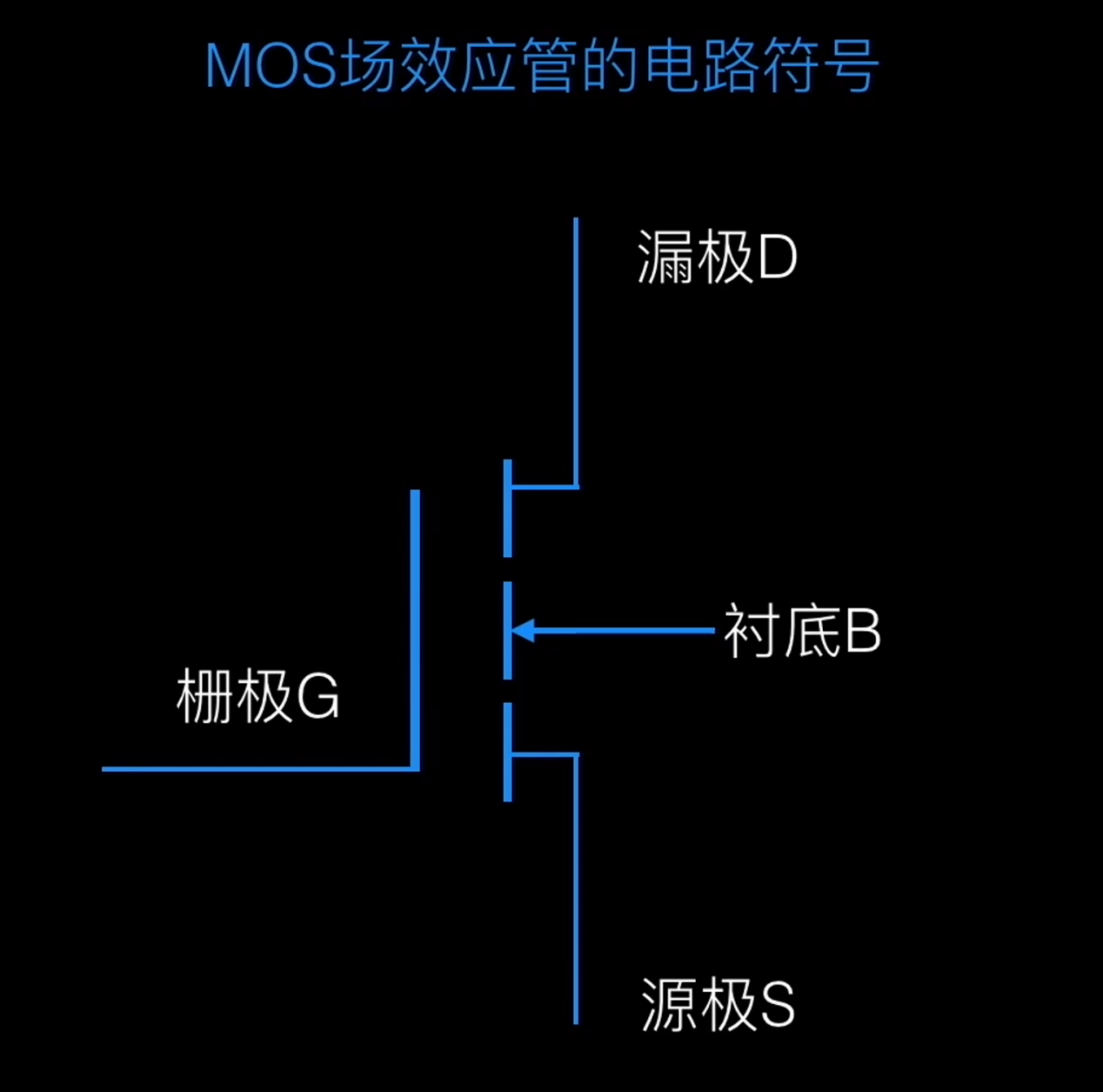

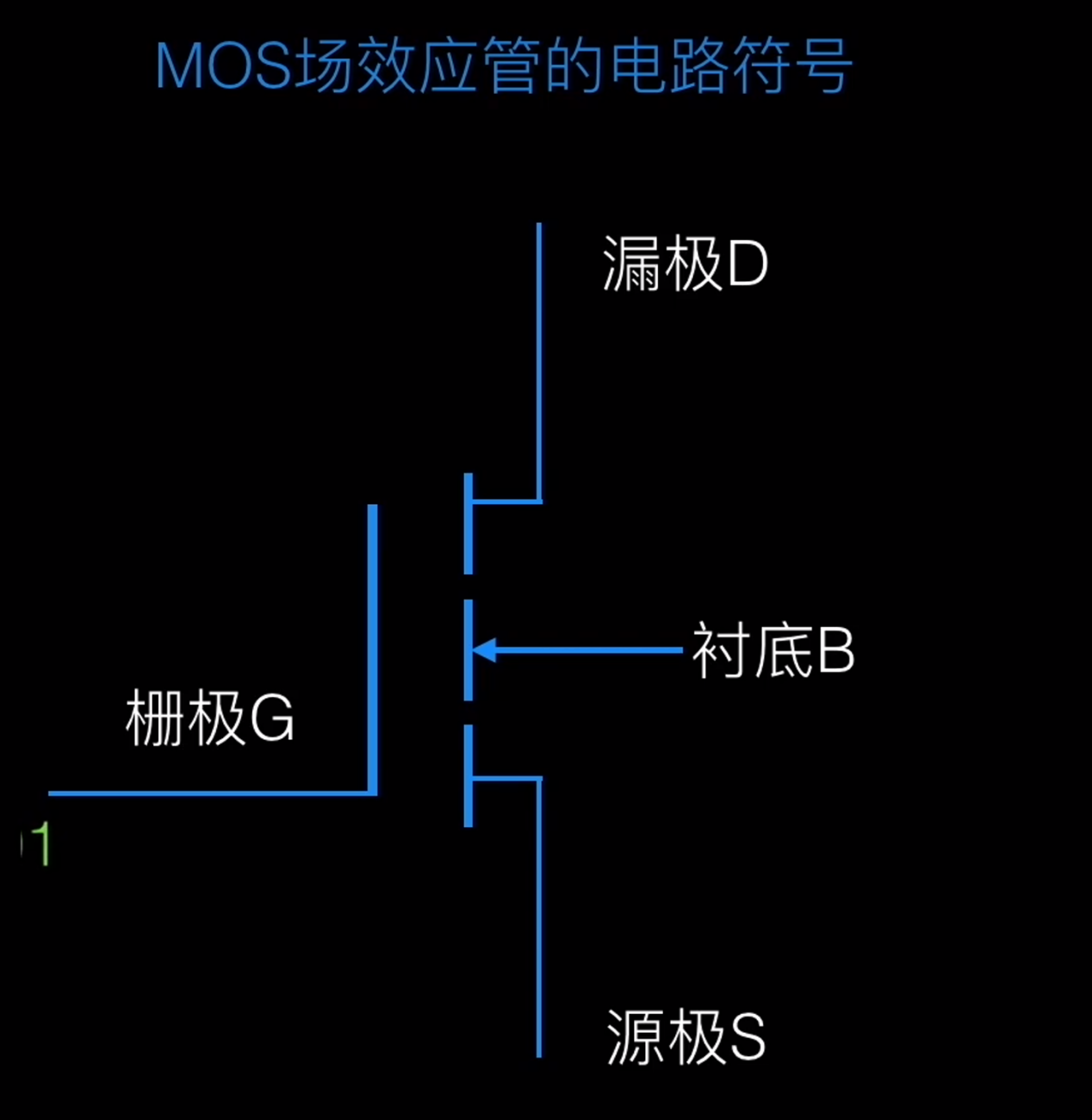

场效应管(以cmos为例):

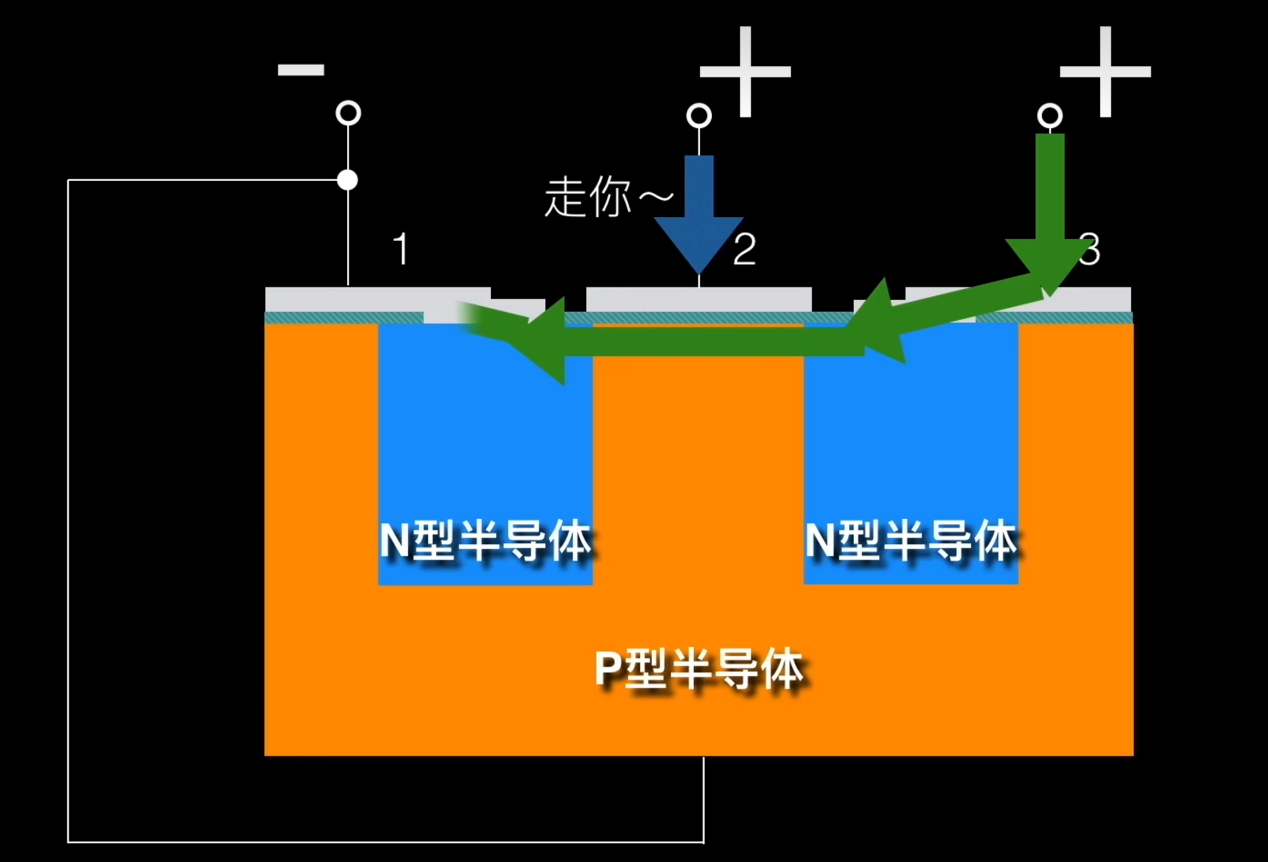

二号区域下面形成一个等效电容,在电场力的作用下,P型半导体的电子聚集在2号区域下,电子不断聚集就会向3号区反向扩散(这个区域叫反型层),3号链接的是正极,电子不断流入正极,1号区域链接负极,电子不断流入2号区形成电流回路

栅极的正负控制电流的通断;

将正电为1,负电为0 ,就是01控制着电路的通断,0和1就是计算机开始的地方

场效应管是各类门电路,集成电路的结构基础;

那么欢迎来到数字电路!

数字电路部分

组合逻辑电路

1854乔治·布尔创造布尔代数将逻辑推理符号化,

1938年香农在硕士论文中将布尔代数与电路结合。

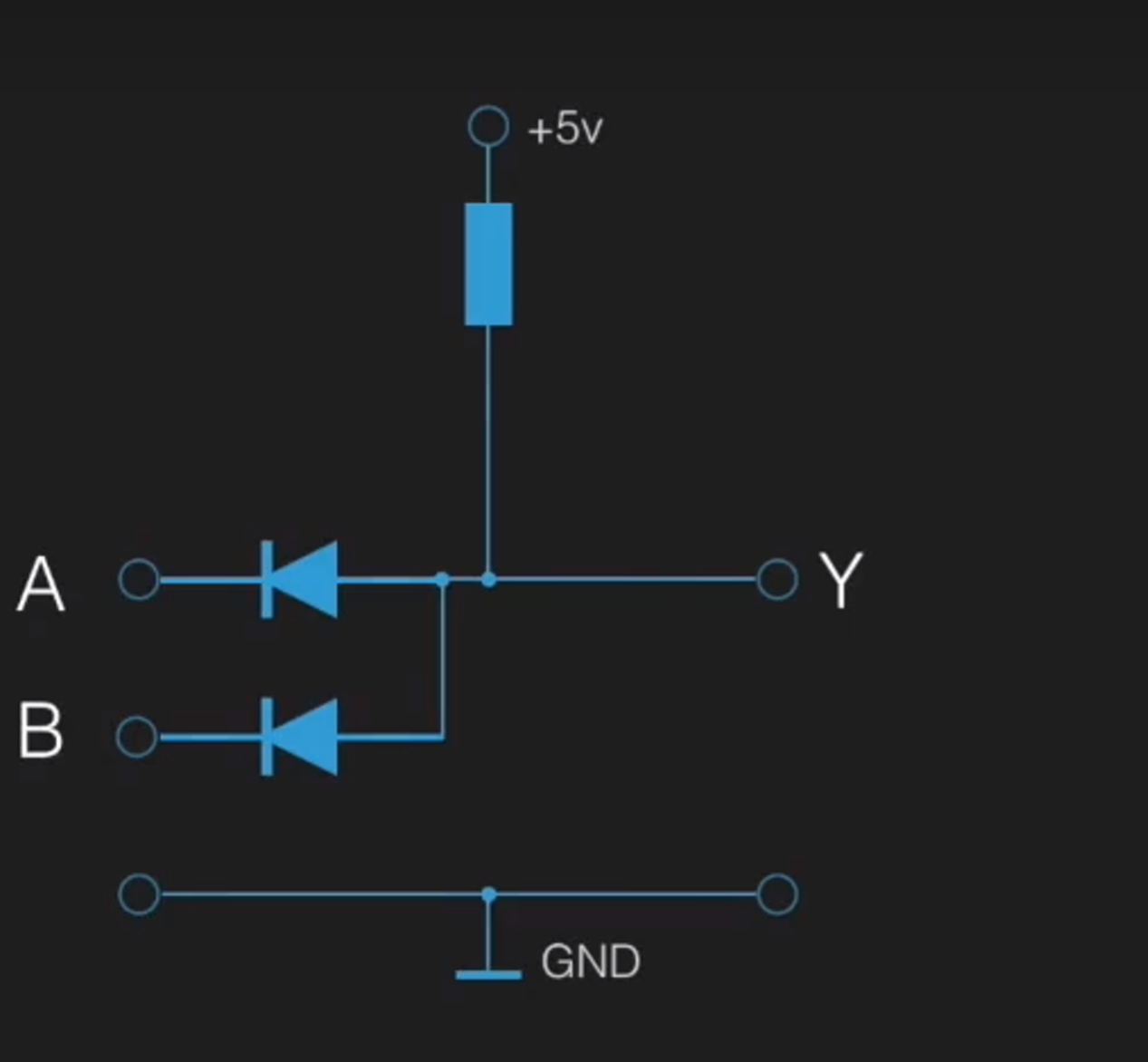

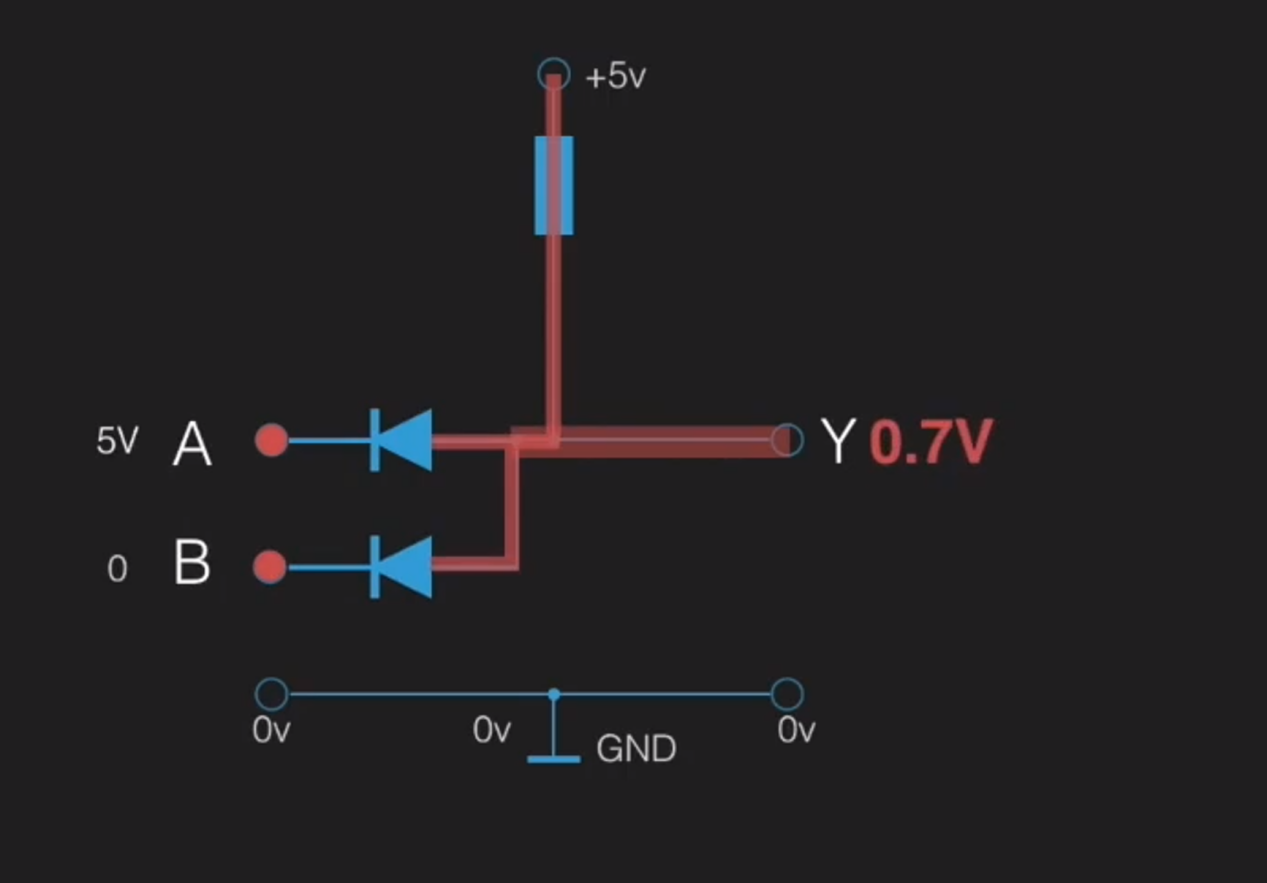

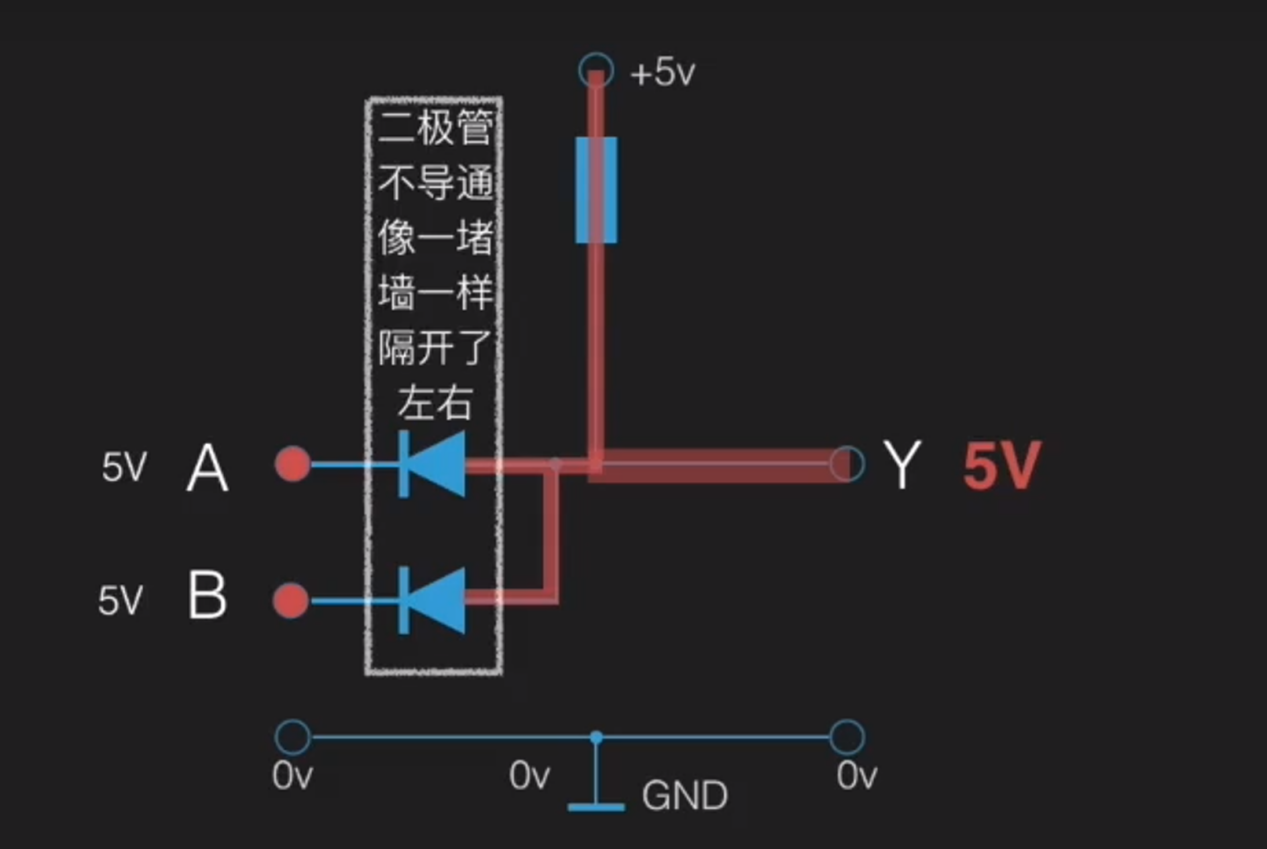

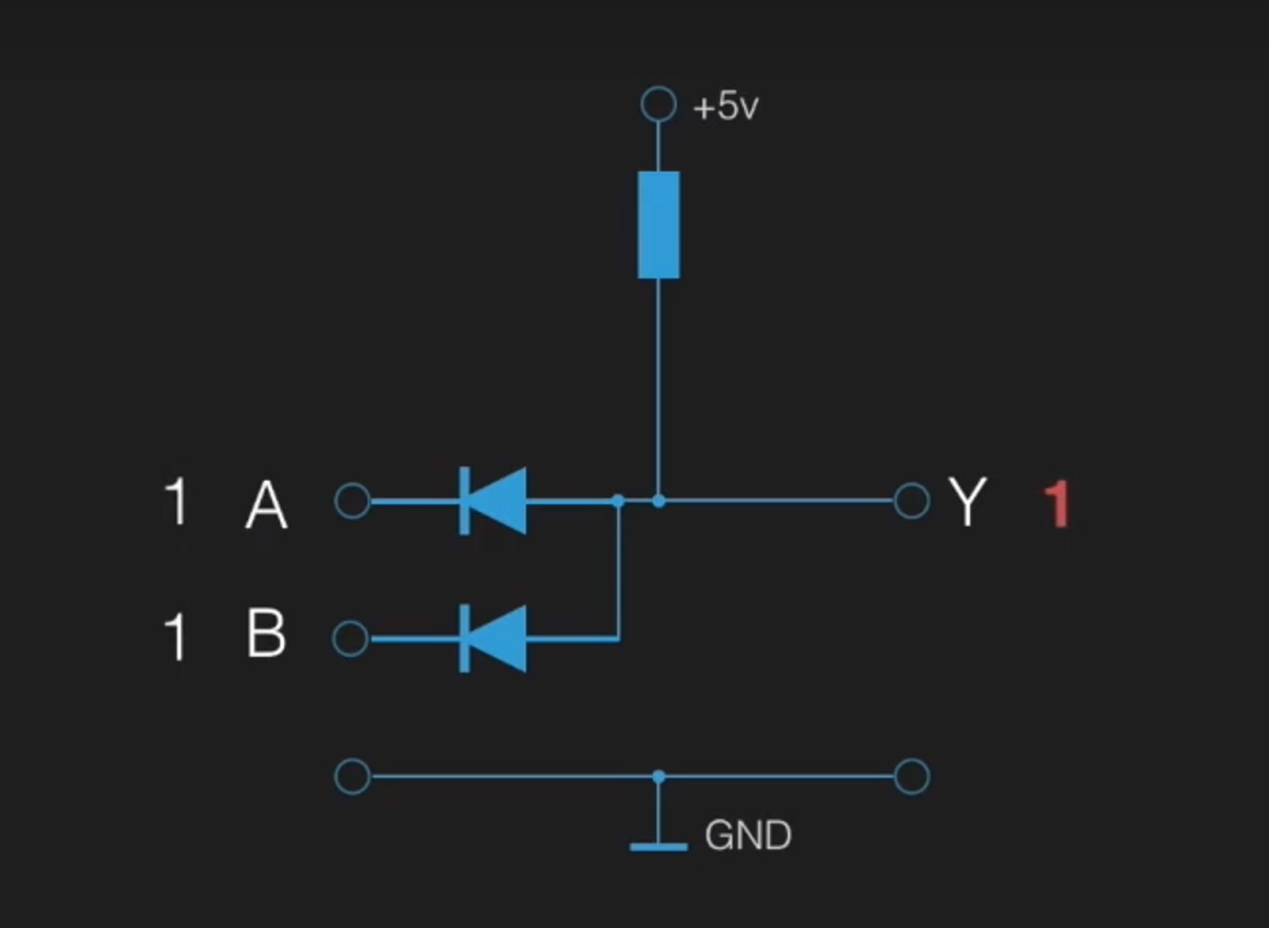

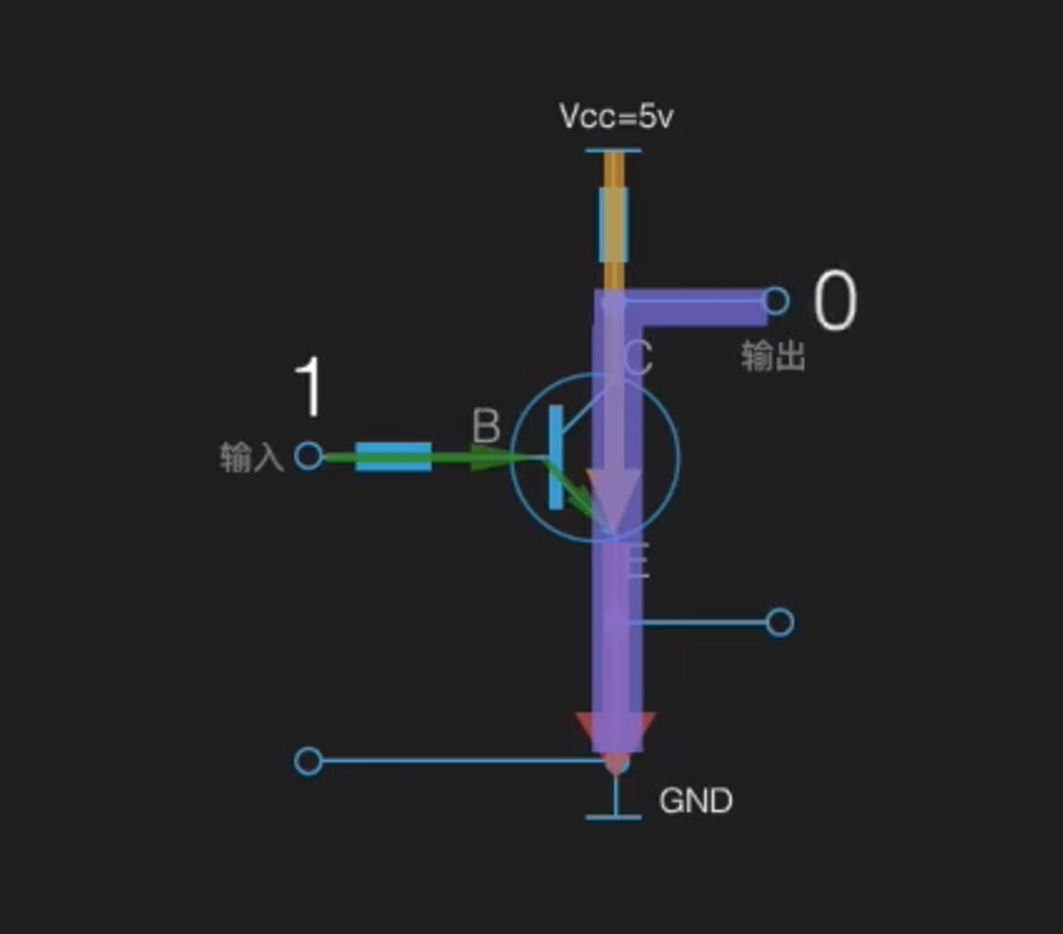

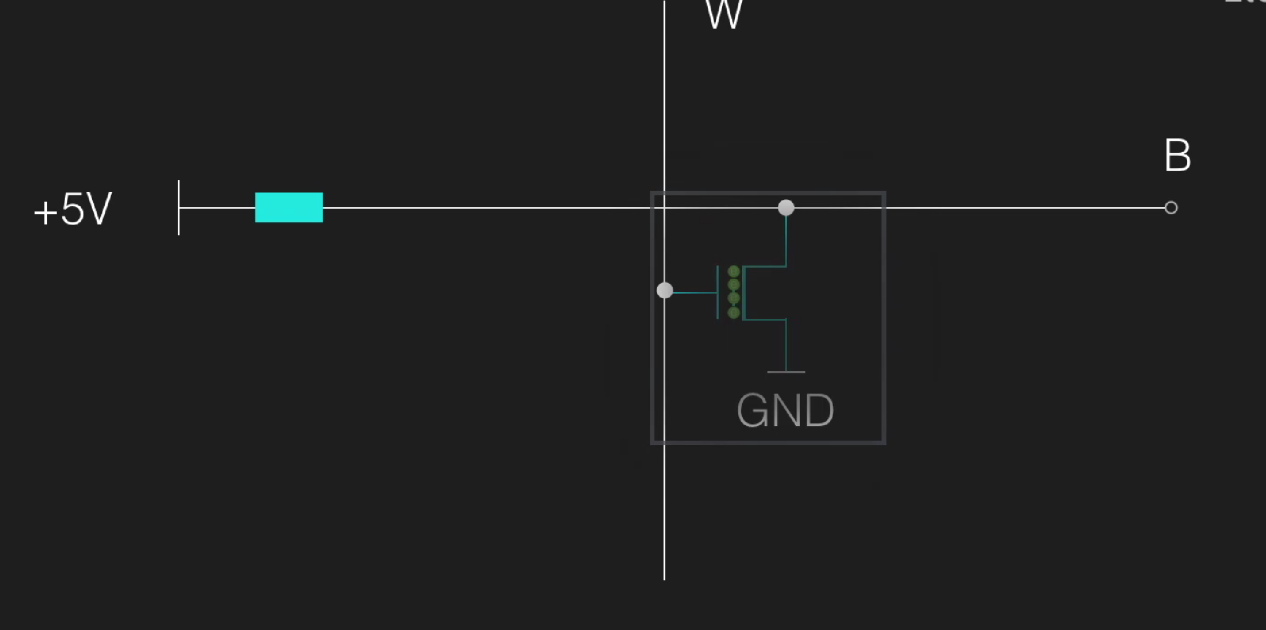

研究如图电路 输出端Y的电压

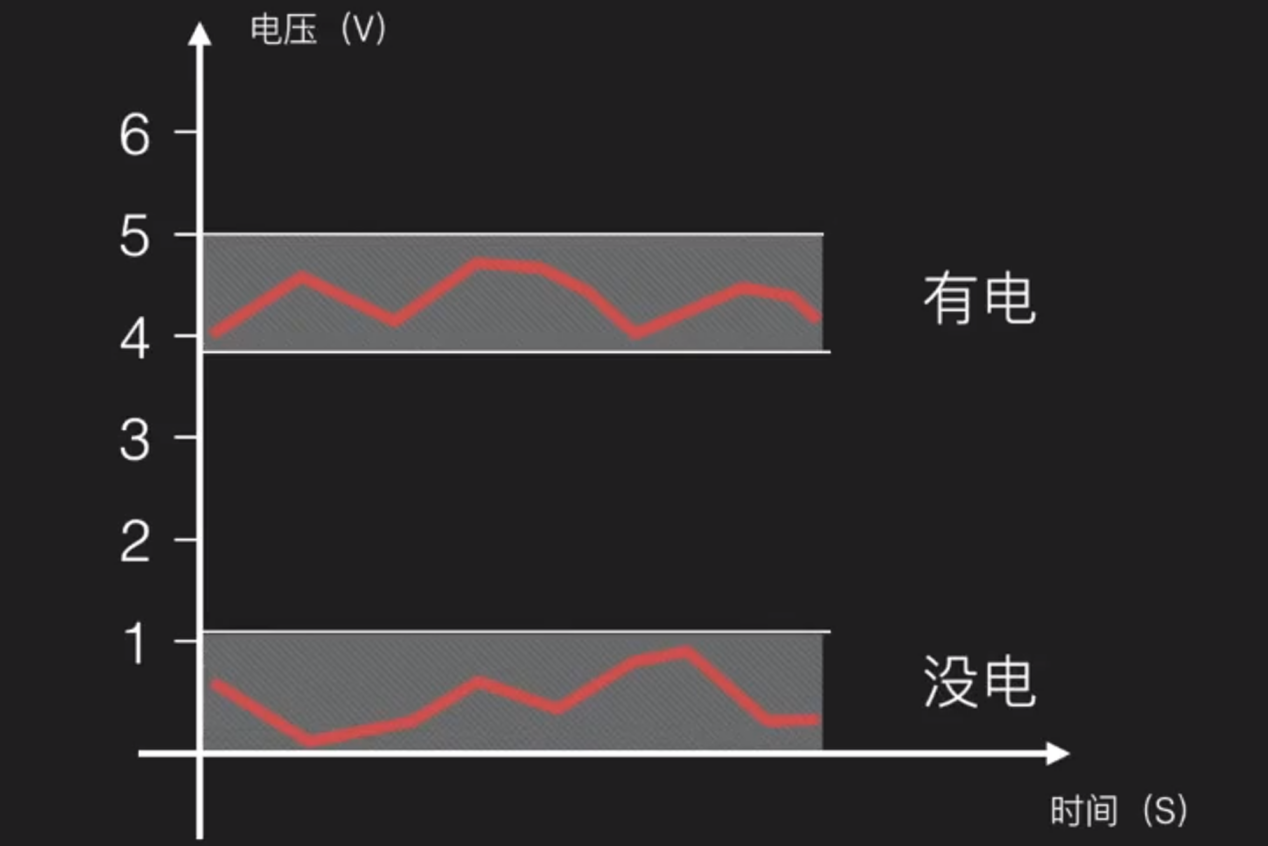

在数字电路中对电压的具体值没有要求,只区分高低电平。

该电路就是一个与门电路

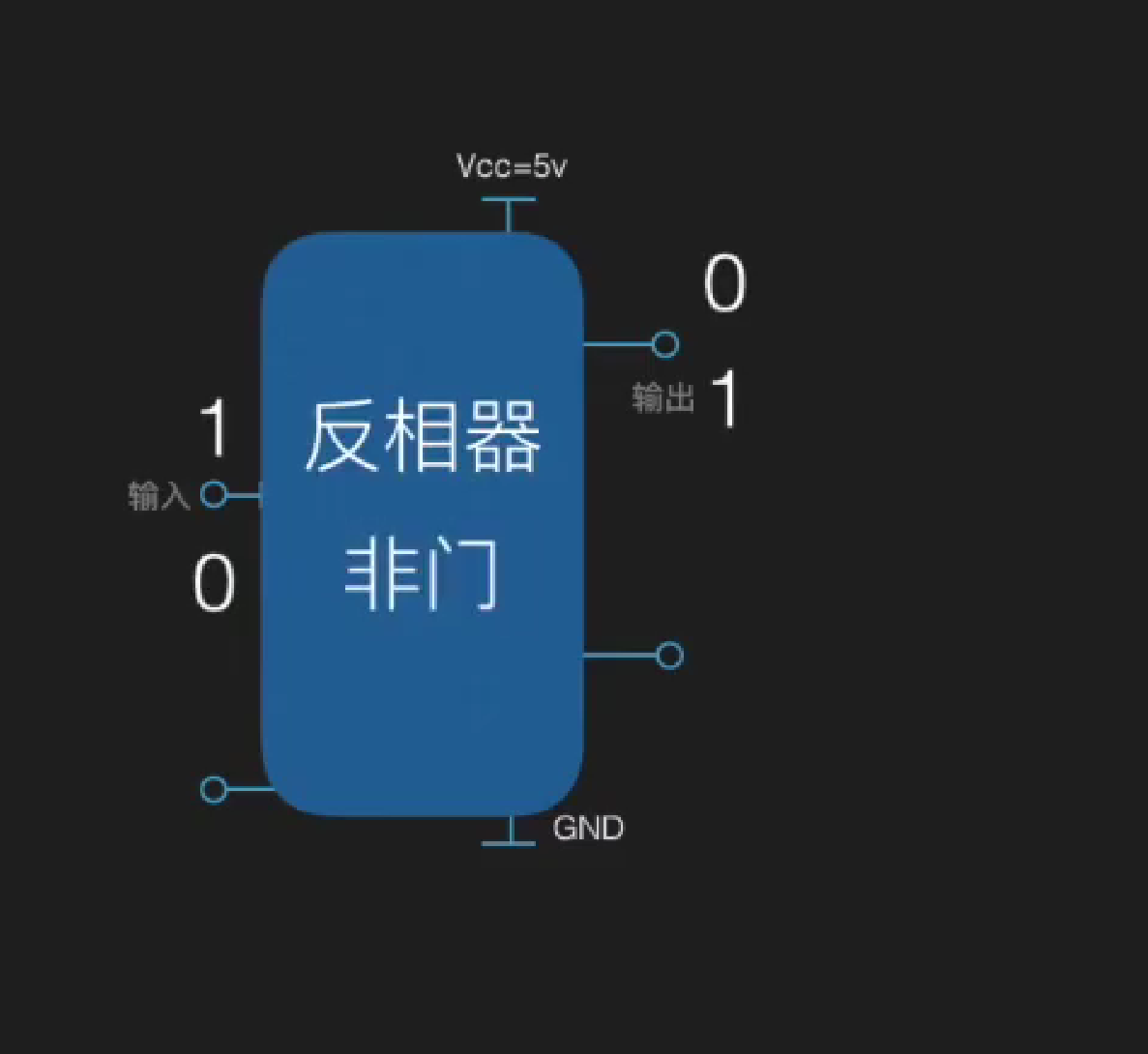

分析该电路,当输入为1时输出为0,相当于一个非门,也可以认为一个反相器

这些门电路封装一般都封装起来使用如经典的74系列芯片

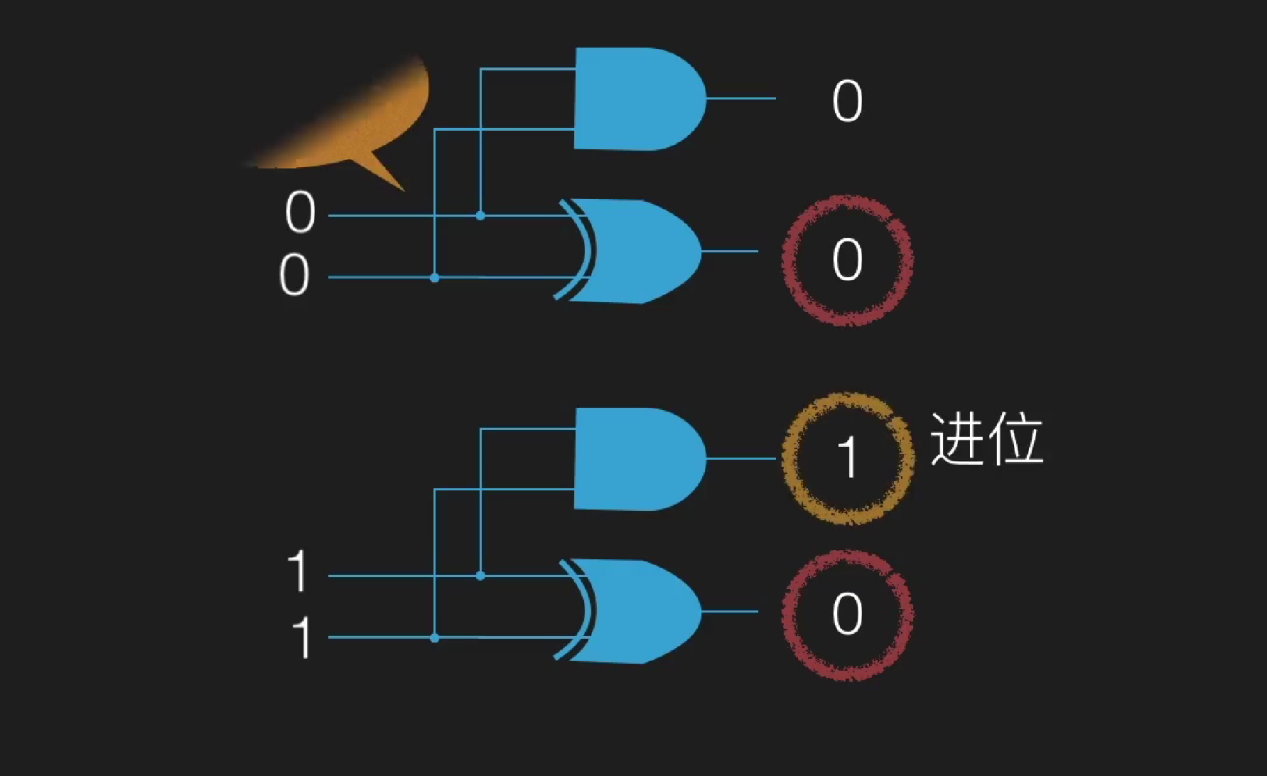

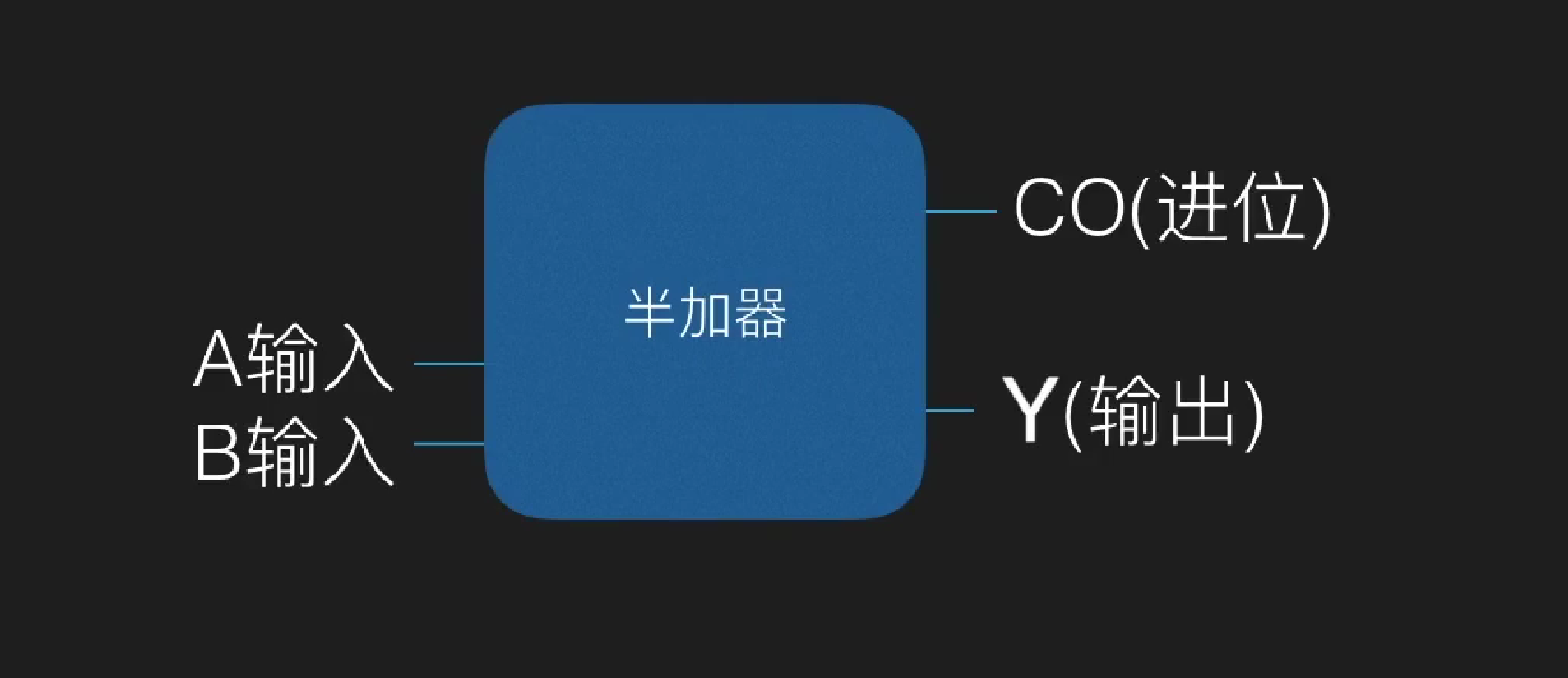

半加器

电路设计的方法:明确需求 画真值表 写出输出方程 化简(公式或者卡诺图)

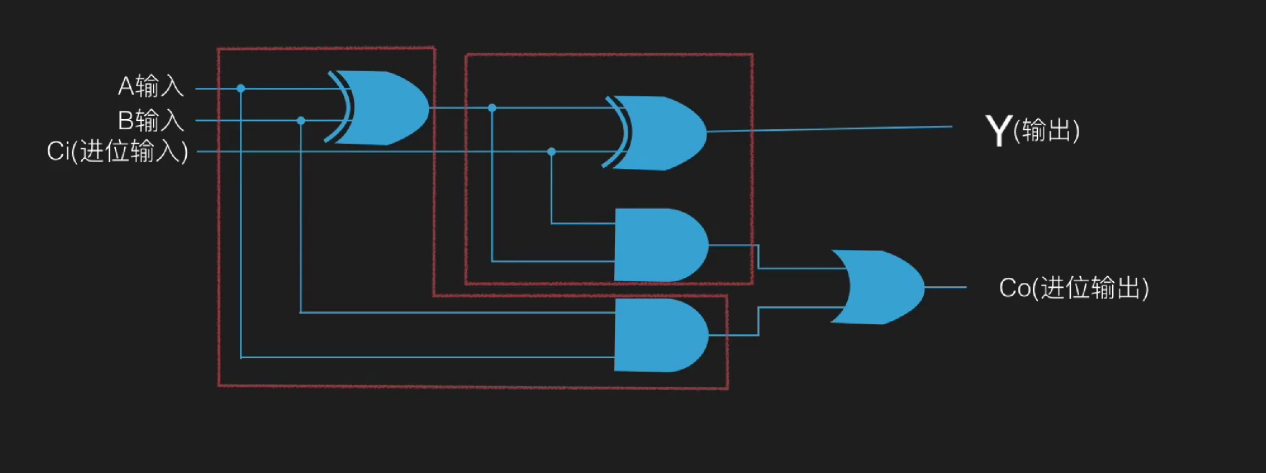

全加器

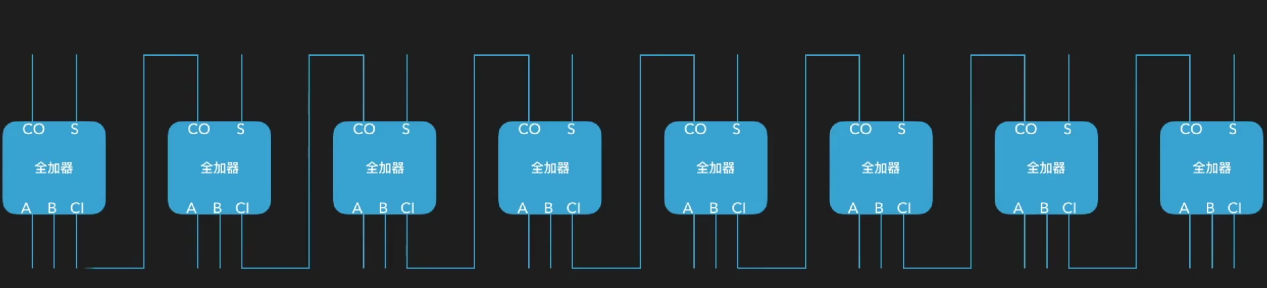

8个全加器相互组合就可以计算8位二进制的运算

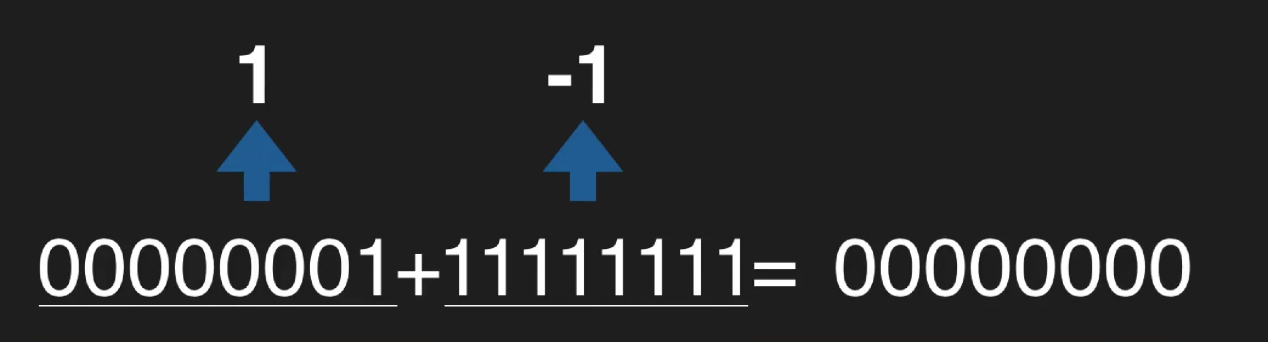

那么有减法器吗,显然是可以设计出来的,但是有更好的解决方案,所以提出补码的概念

补码表示法在计算机科学中有许多优势

-

简化硬件设计:补码使得加法器电路可以同时用于执行加法和减法操作。这是因为补码允许将减法操作转换为加法操作加上求补操作。这减少了处理器中所需的硬件复杂性,并且提高了效率。

-

零的唯一表示:在补码中,零只有一种表示形式(例如,8位系统中的0表示为 00000000),这避免了原码或反码中存在的零的两种表示形式(正零和负零)的问题。

-

溢出处理简单:当两个补码数相加导致溢出时,结果依然是正确的模数结果。例如,在8位系统中,如果两个正数相加的结果超过了

11111111(十进制255),或者两个负数相加的结果低于 00000000(十进制0),结果会自动“环绕”,并且可以继续用作后续计算的一部分。 -

便于实现:补码的编码规则简单明了,易于硬件和软件实现。对于负数,只需要找到该数的绝对值的原码,然后对其按位取反并加一即可得到它的补码。

-

自然排序:在补码表示下,数值按照它们的二进制代码自然排序,这意味着你可以直接比较两个补码数的大小,而不需要考虑符号位。

-

与无符号整数兼容:补码的表示方式使得有符号整数和无符号整数在内存中的表示是一样的,这有助于简化数据处理和存储。

在计算机领域中我们还需要其他的原件:

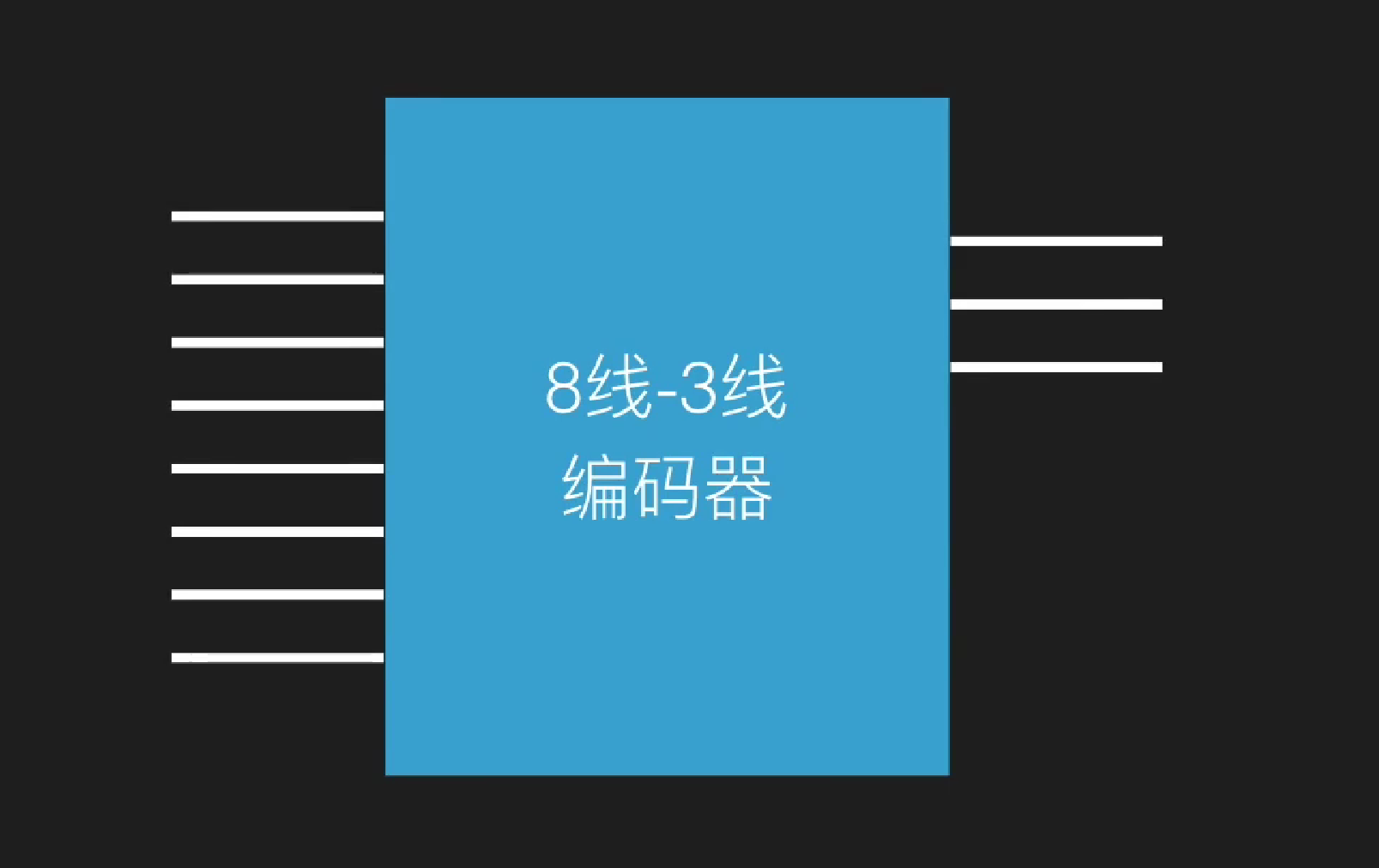

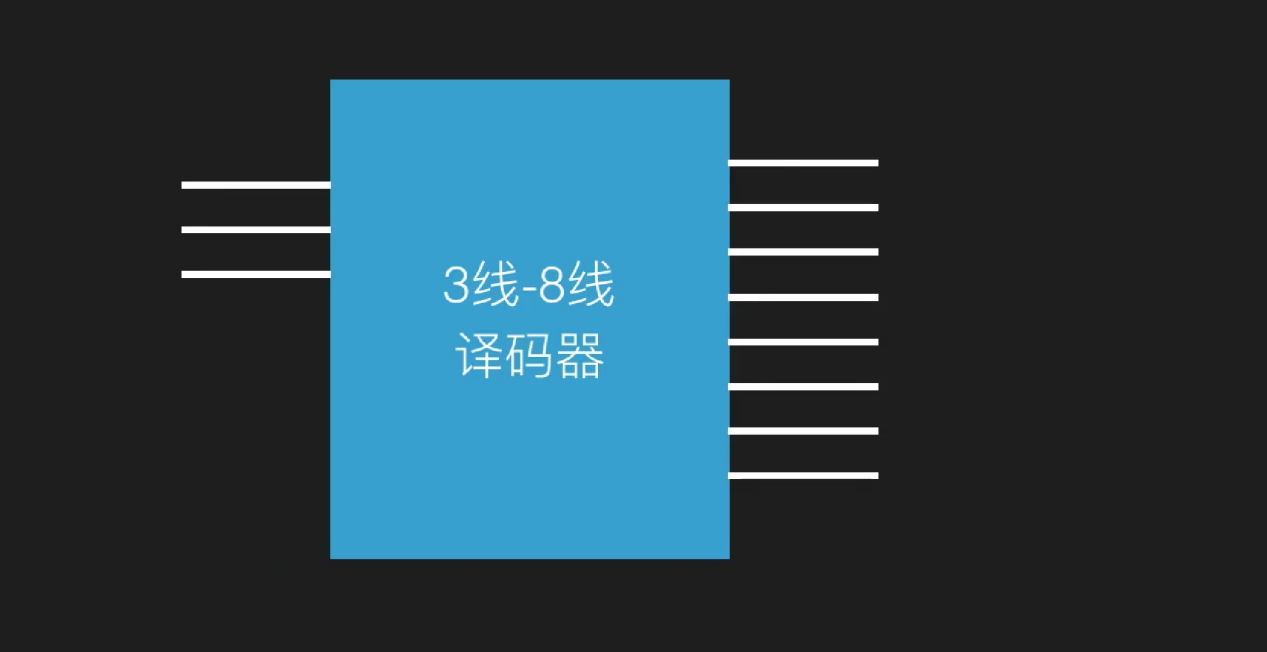

把多路信号转变为二进制编码;

二进制转换为8路信号;

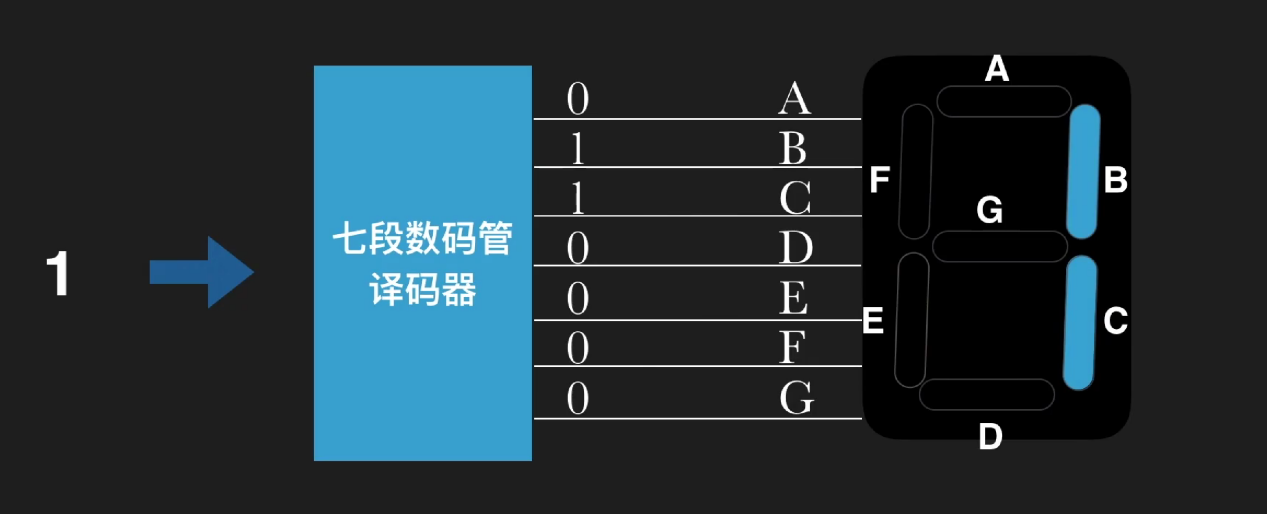

在工控领域广泛使用的7447数码管

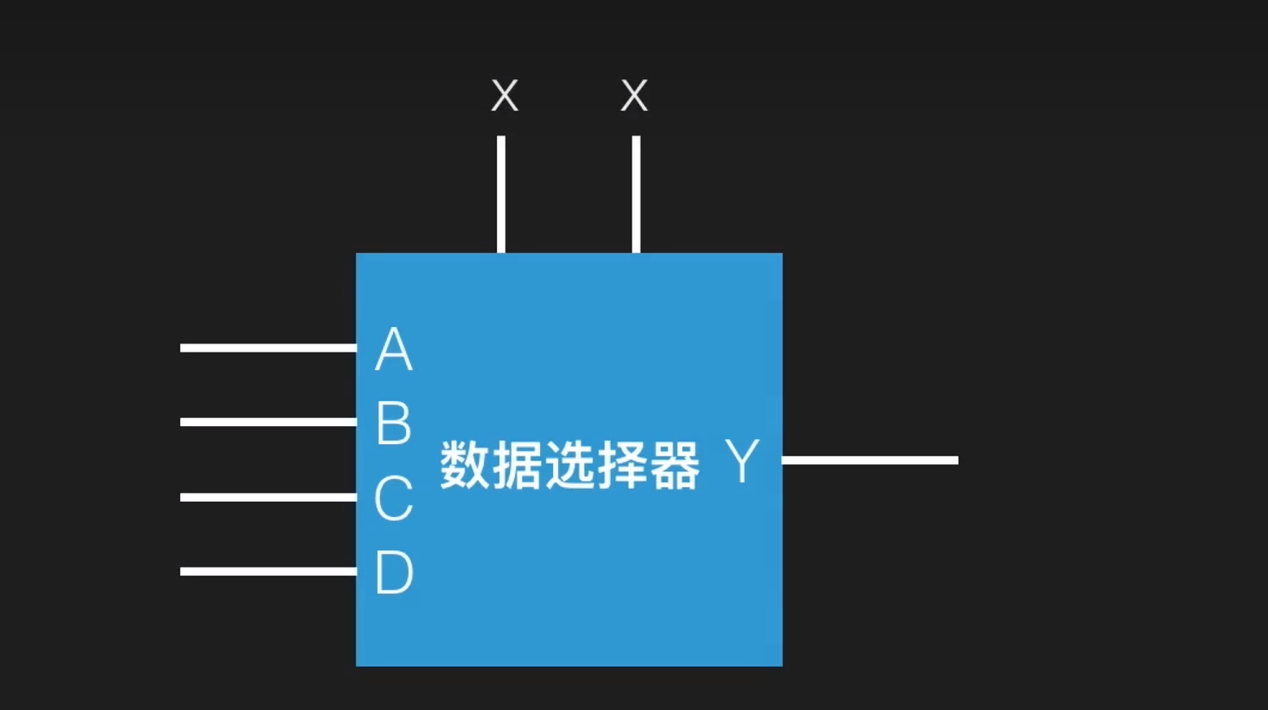

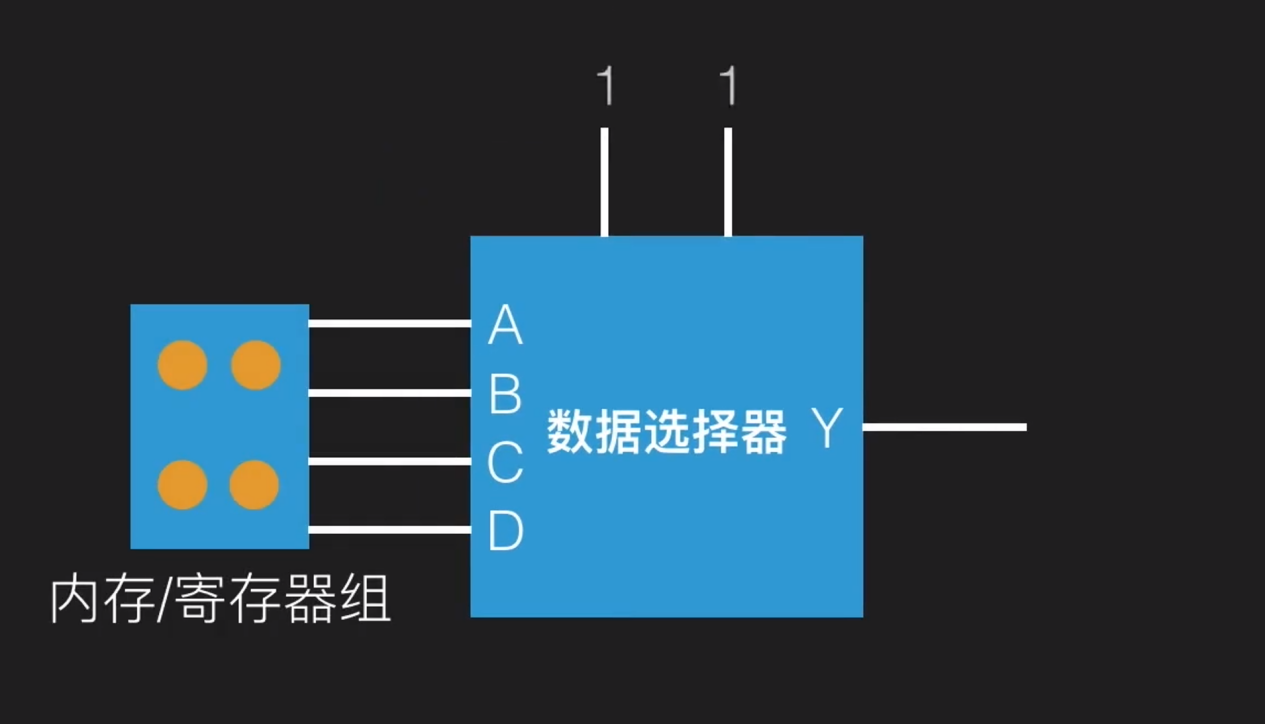

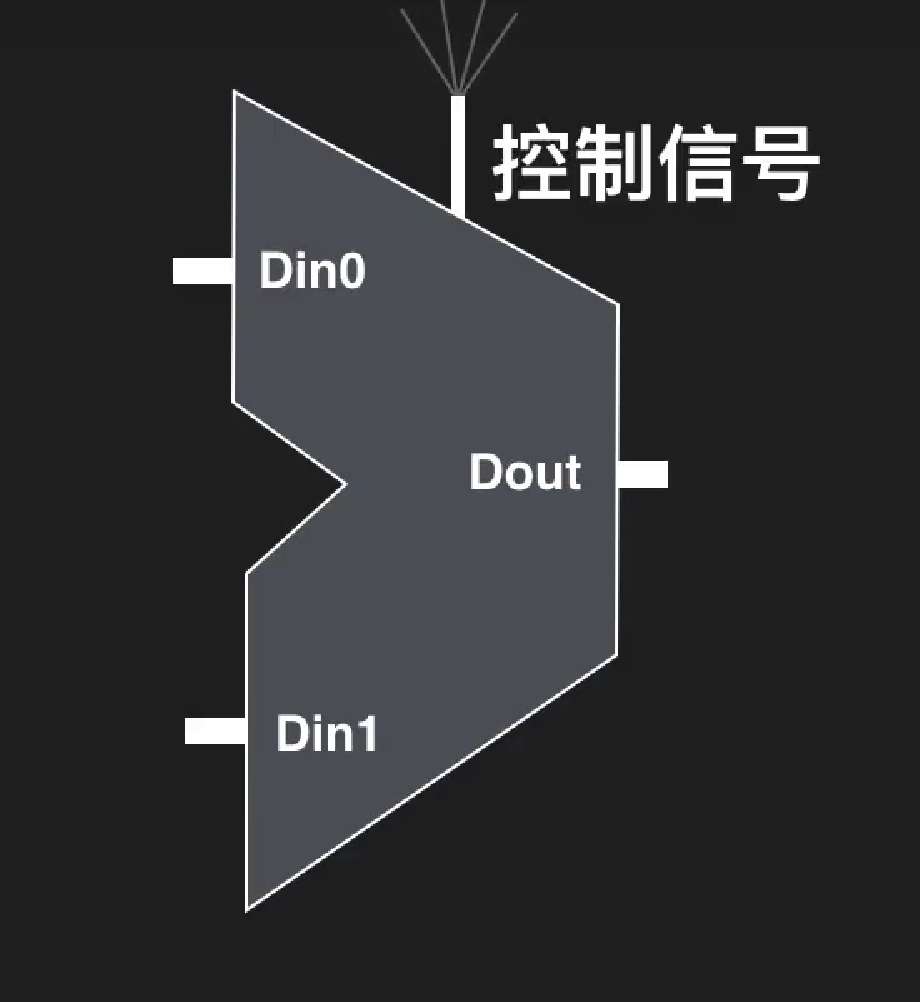

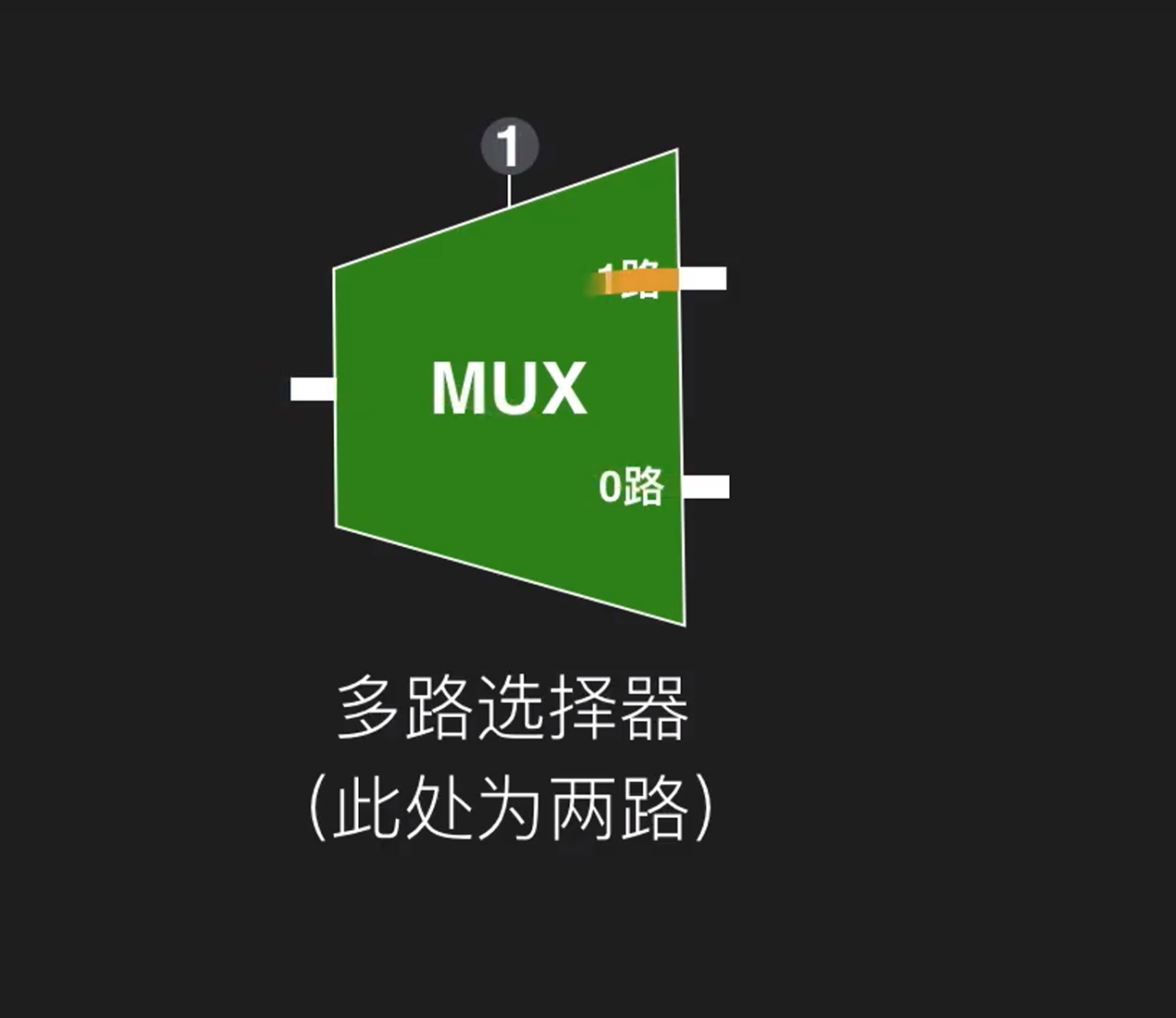

数据选择器,通过输入xx的值选择Y的输出,如xx=00时,输出A路的值,在计算机中可以用它完成内存寄存器的寻址功能

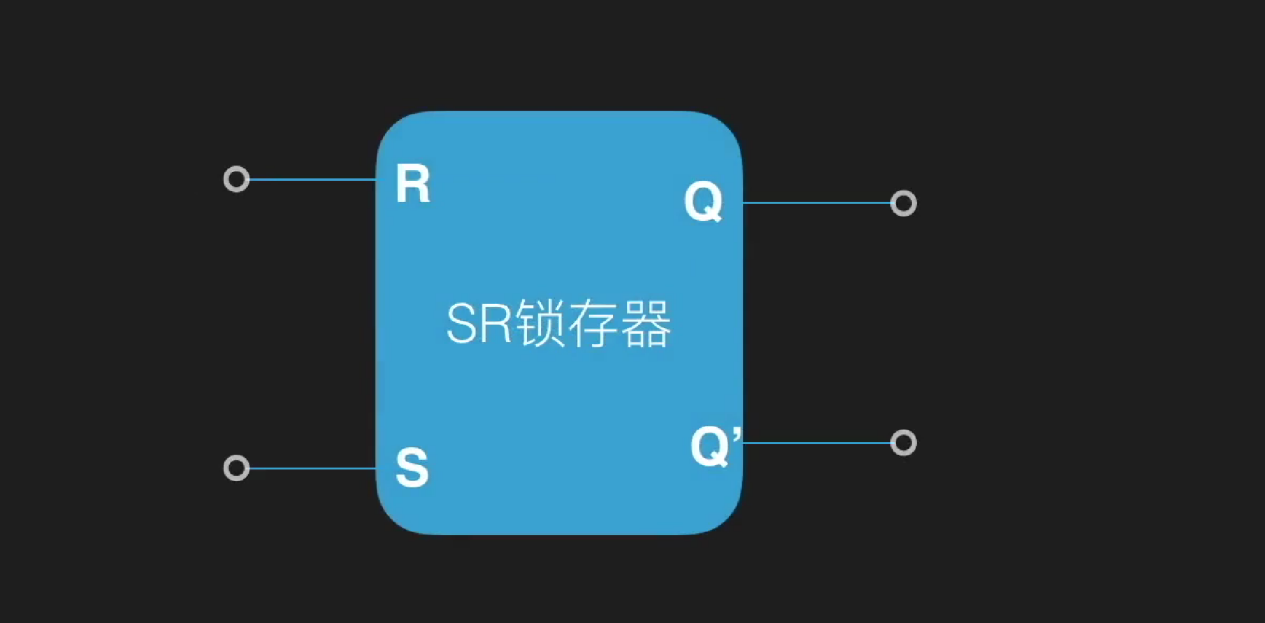

时序逻辑电路

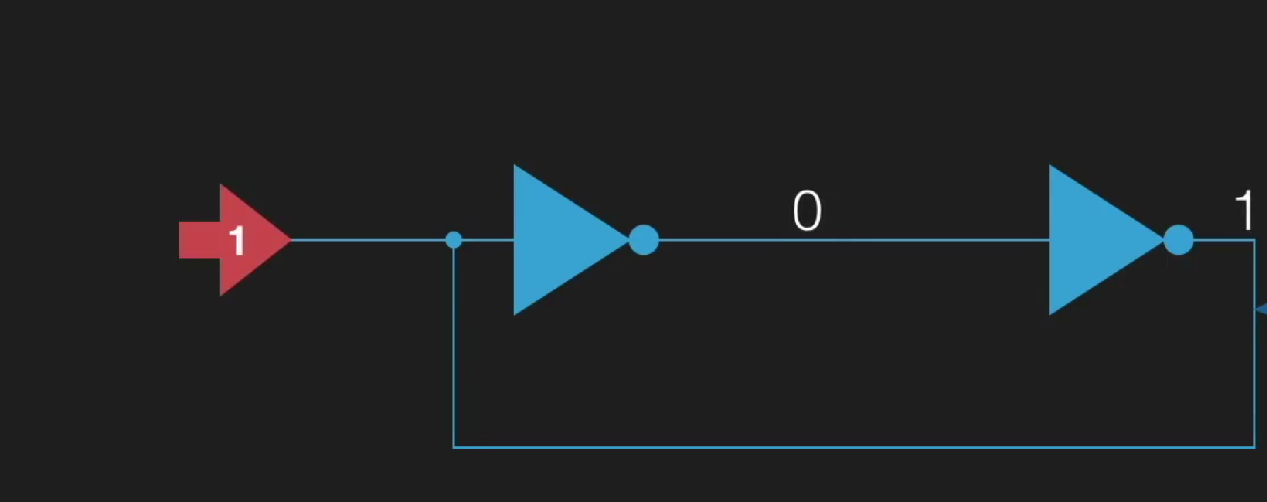

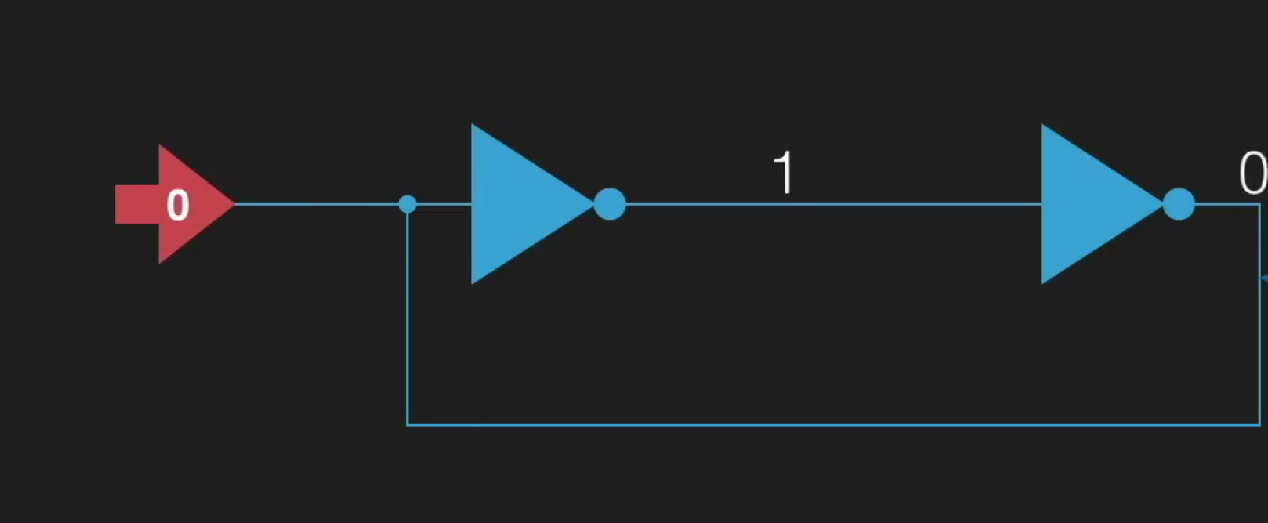

两个非门连接,不论输入0还是1都是稳定状态

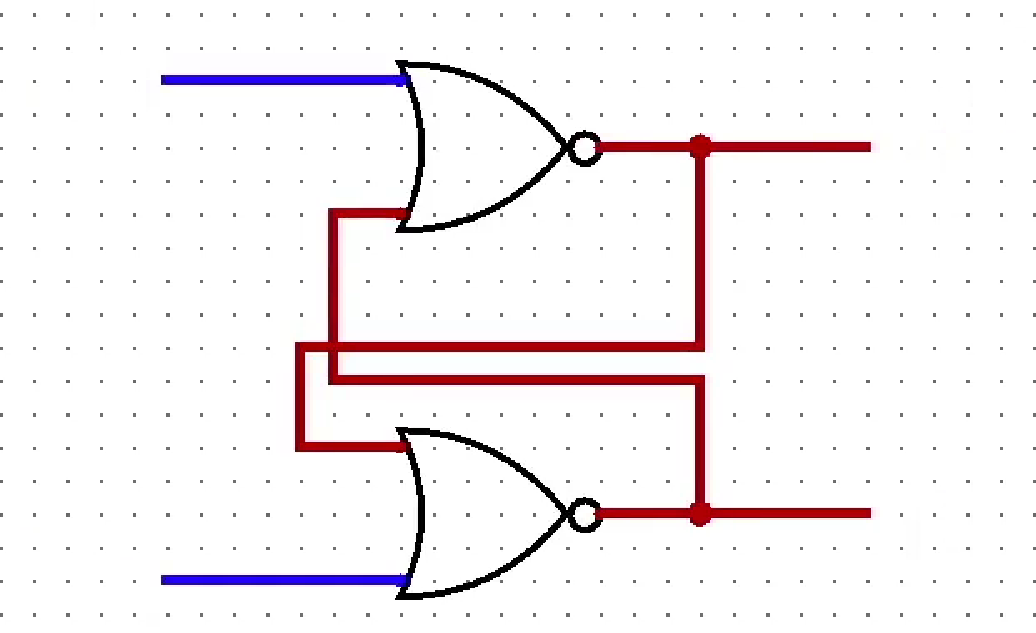

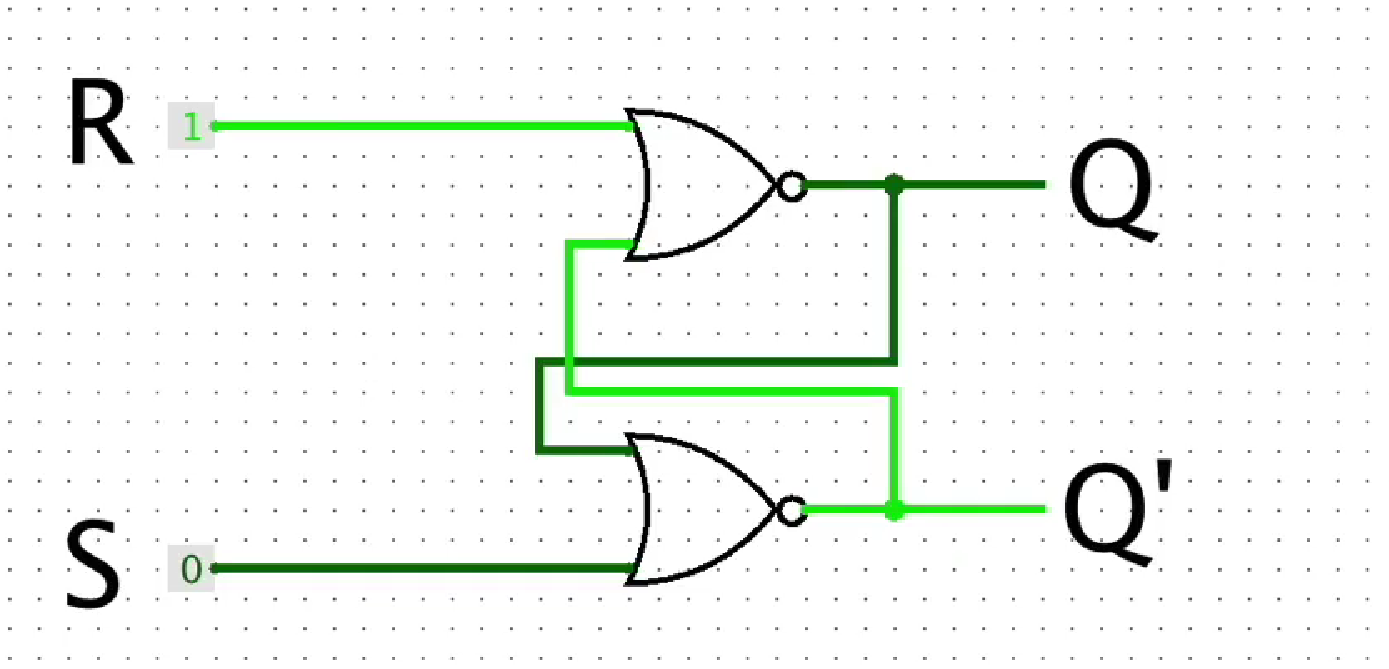

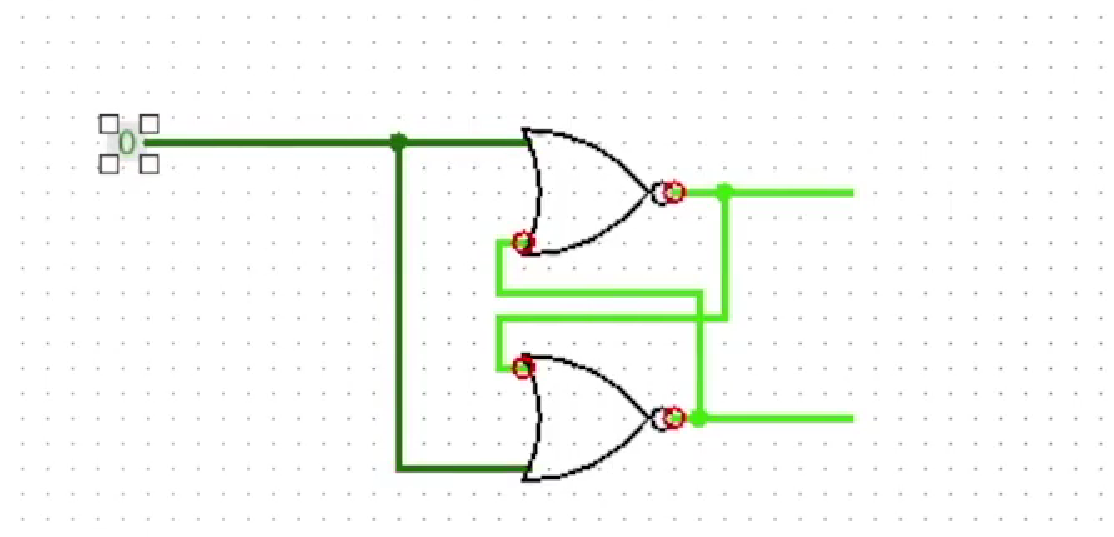

连接两个或非门

发现输入不完全由我们确定。

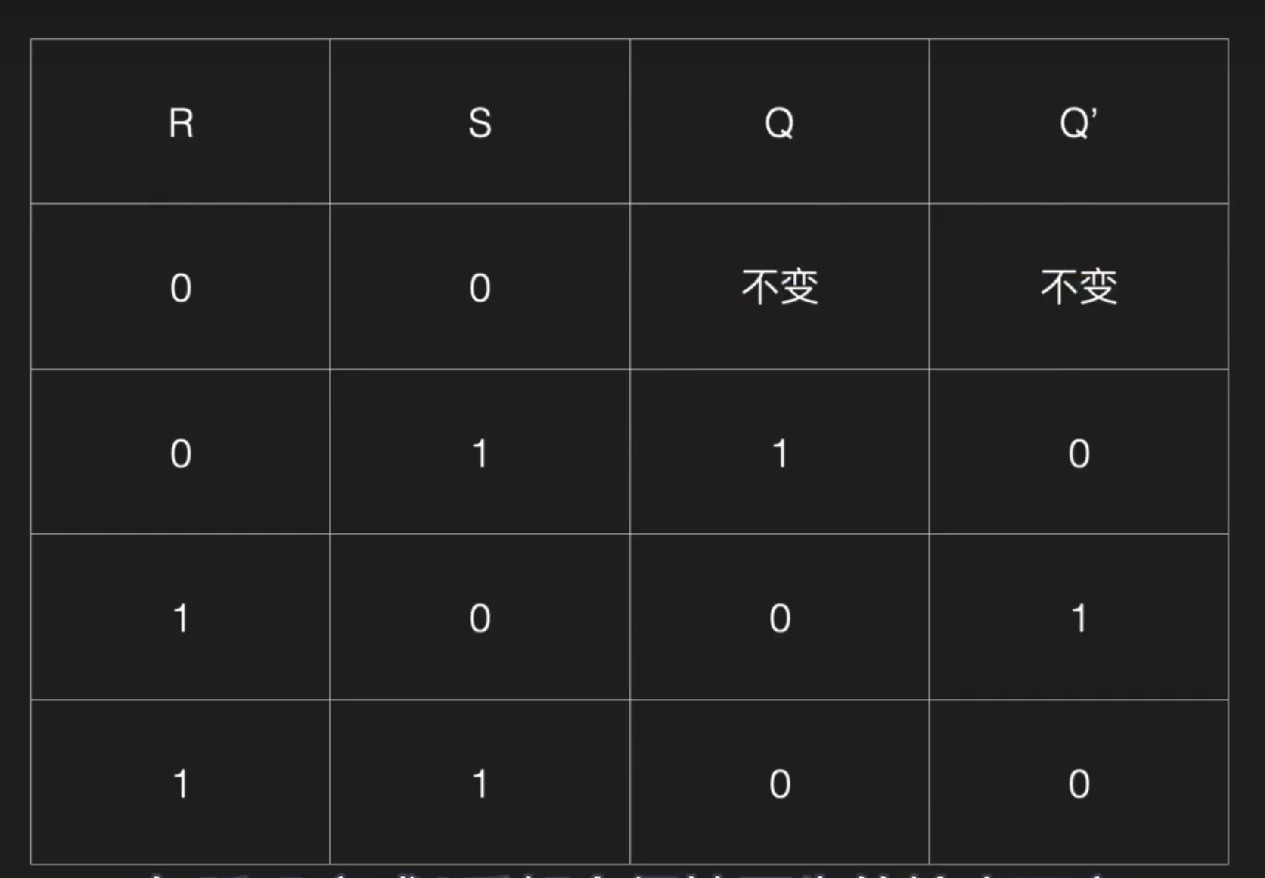

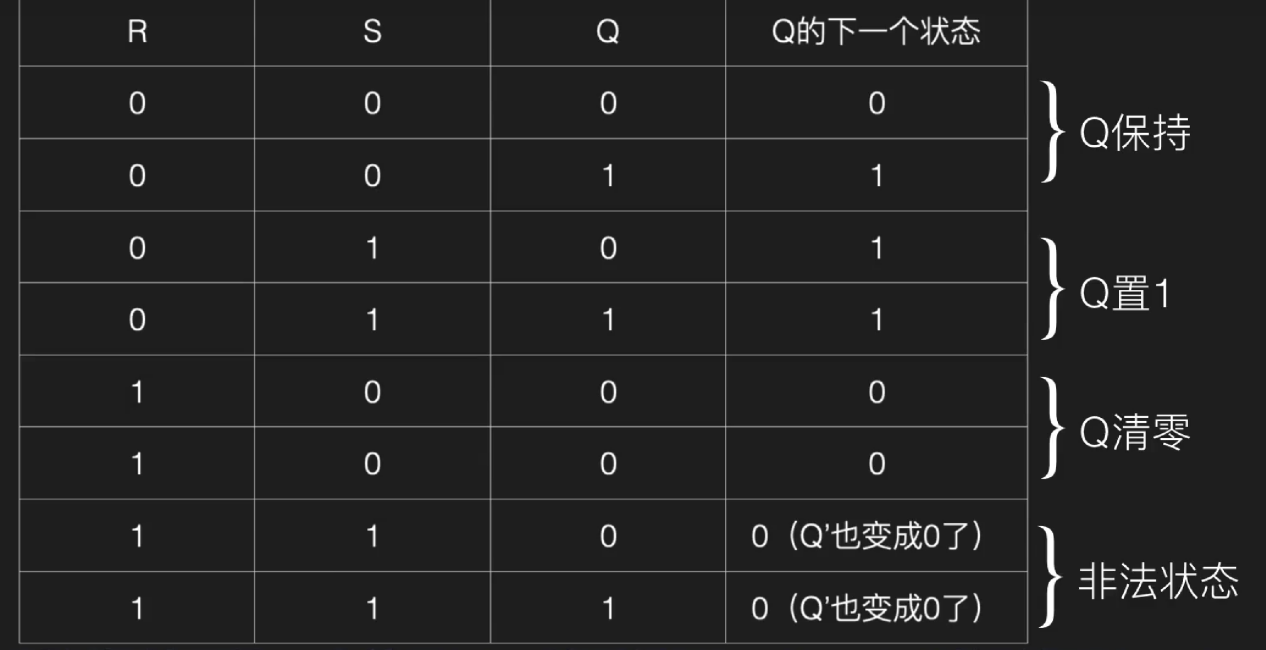

输出不变,给输入,输出端取名

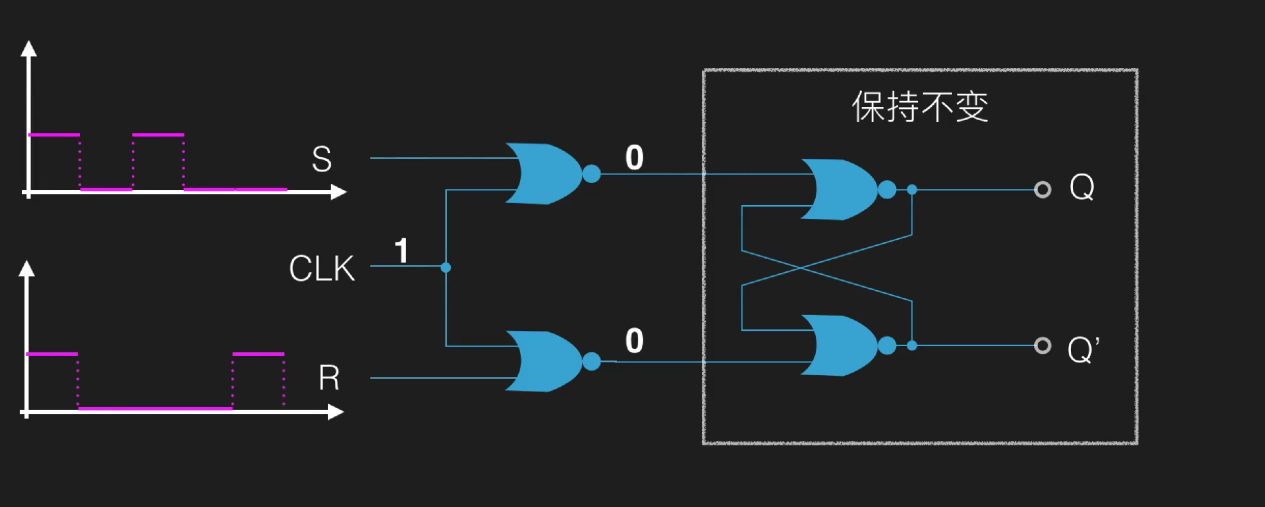

分析得出当R =0 S=0时,保持上一个输出不变。

当R=1 S=0 时,Q=1,R=S=0 Q不变 可以认为存入了一位数据,

同样的 当R=0 S=1 时,Q=0,R=S=0 Q不变

现在讨论R=S=1,相当于同时撤离两个信号,在现实中由于电路的响应不可能达到决定同时,这与电路在制作时的微小误差有关,所以结果是随机的。下图是在理想状态下模拟:

Logism显示震荡发生

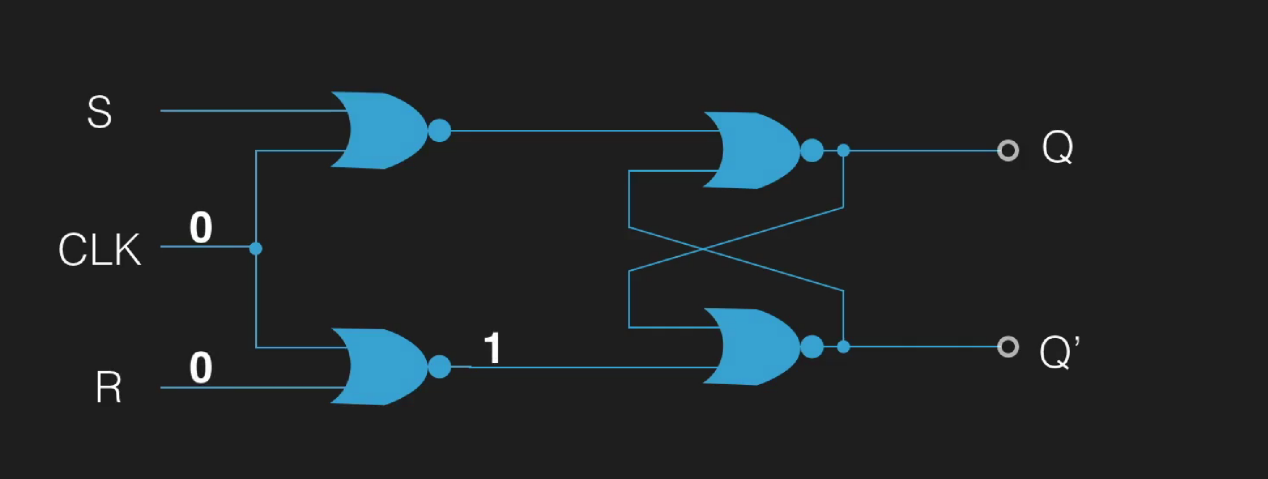

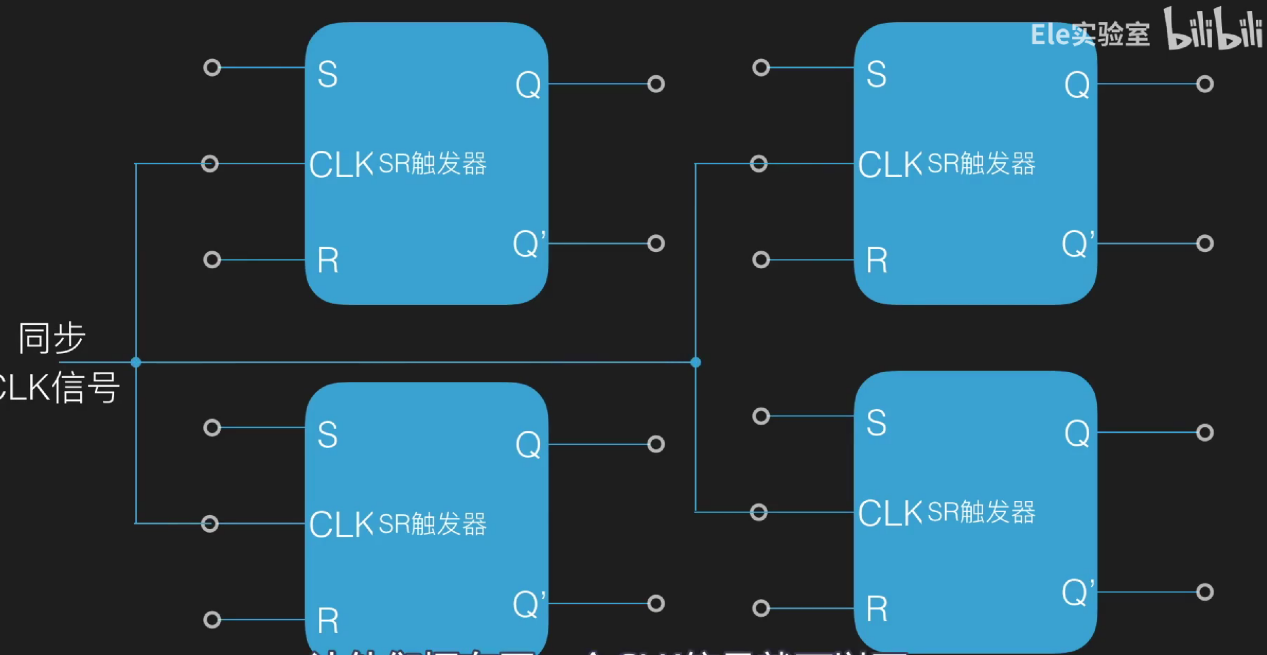

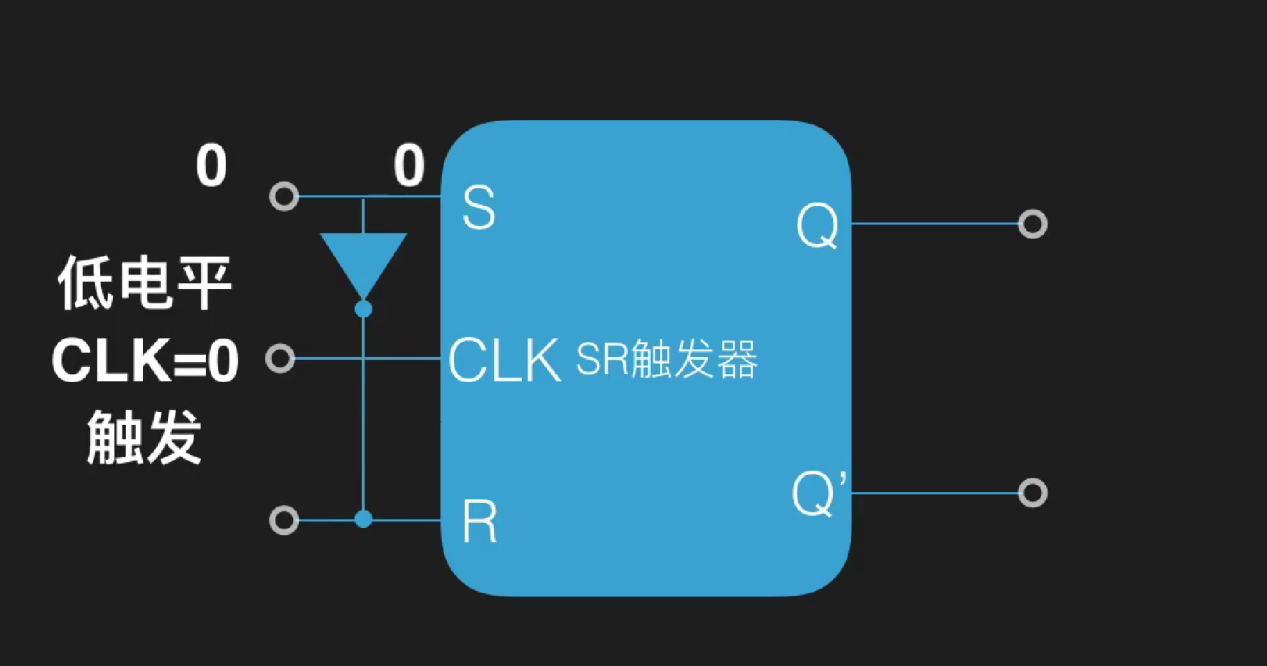

同步触发器

让多个触发器都链接同一个CLK,就可以同时写入

R与S之间加一个非门就可以只用一个信号完成赋值,也避免了非法输入

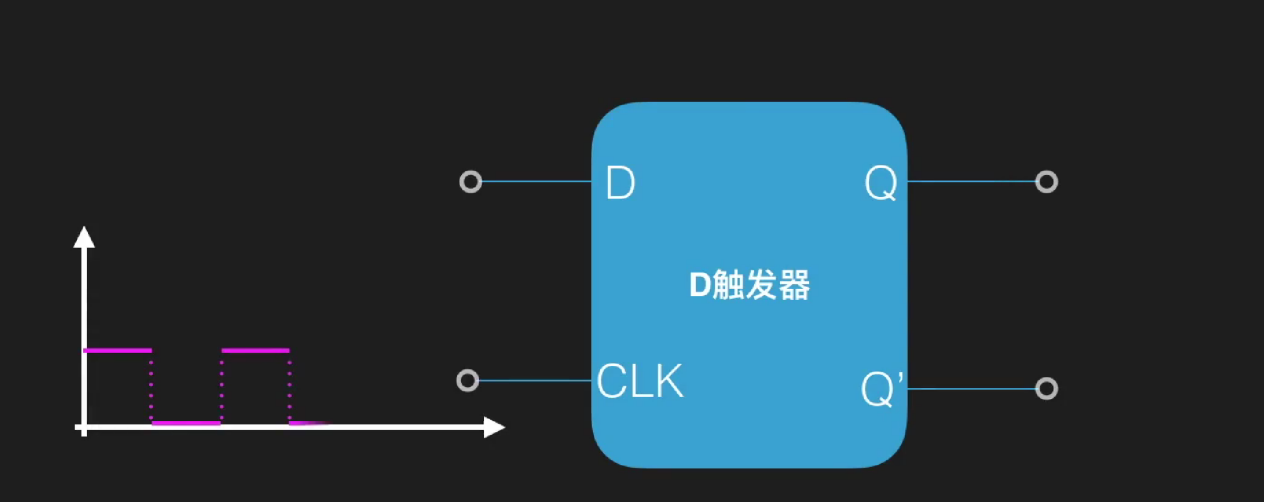

这就是D触发器

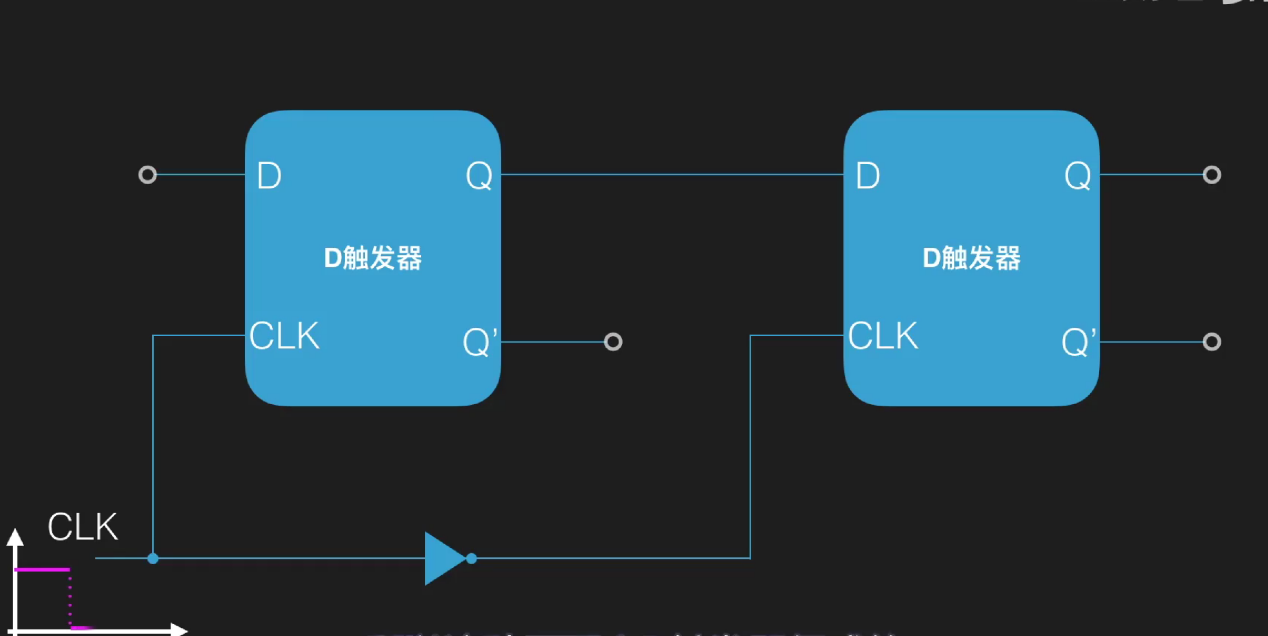

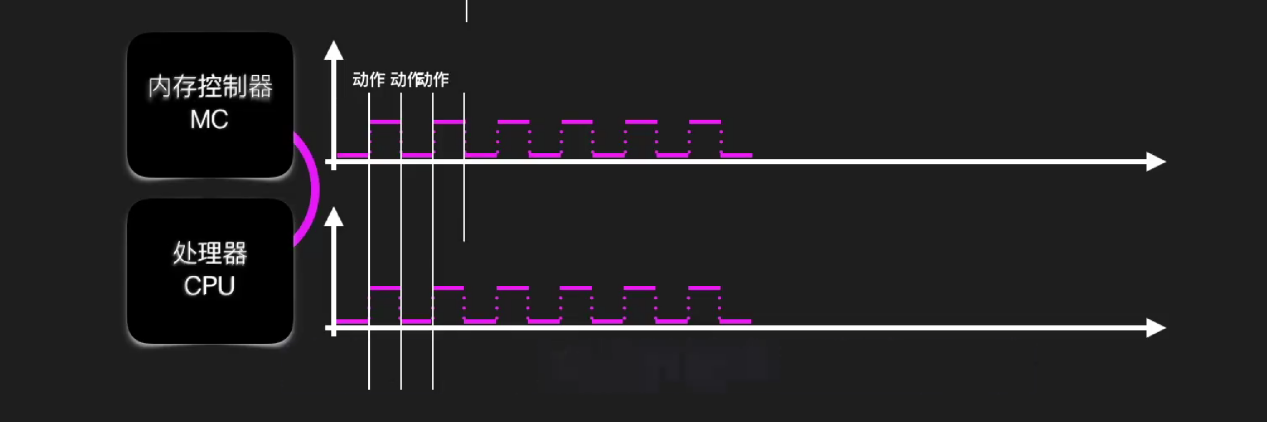

只有电平变化时才发生一次动作成为脉冲触发器或叫边缘触发器

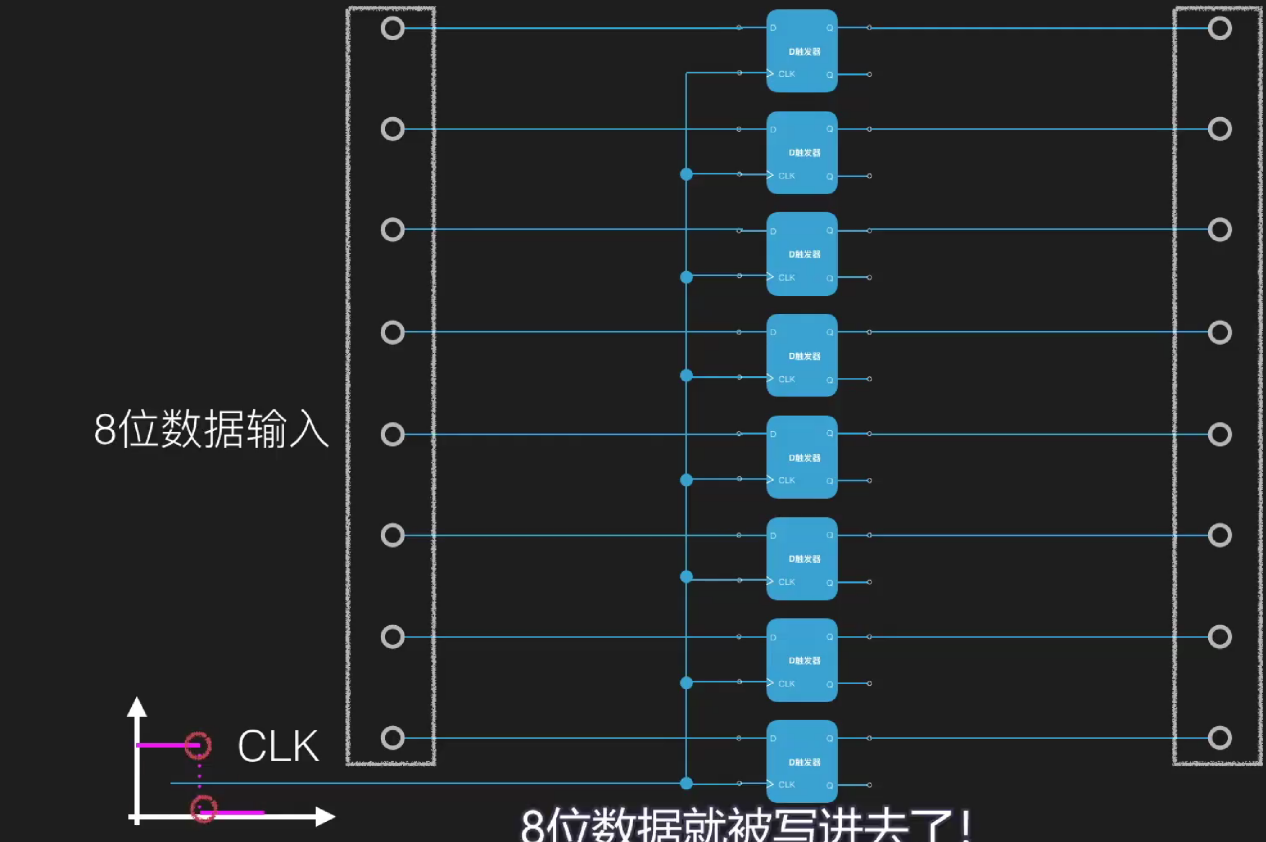

触发器的应用:寄存器

当clk下降沿到来数据被写入

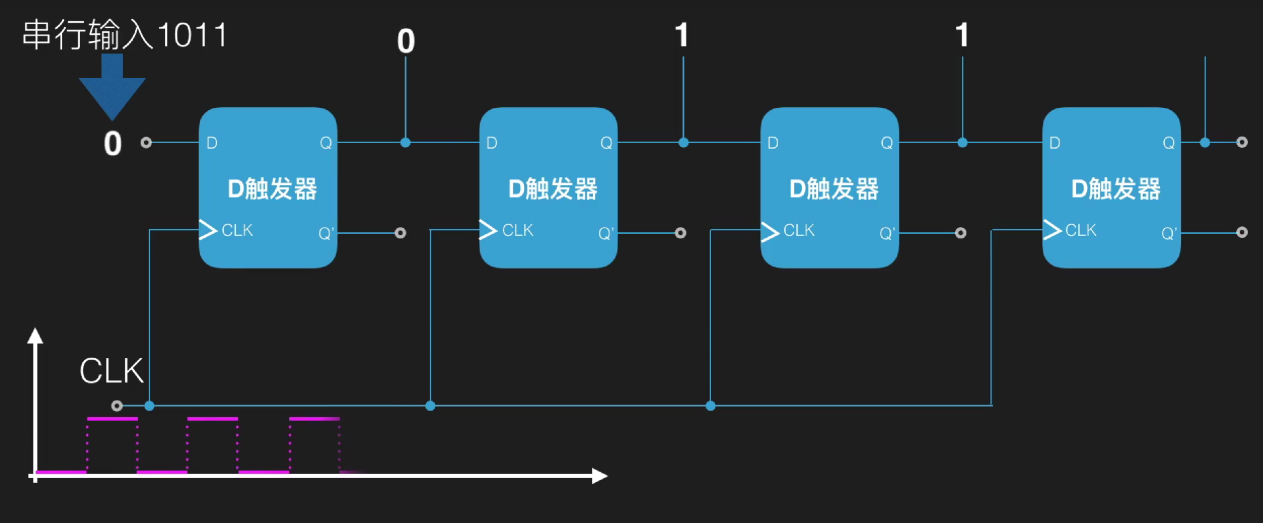

移位寄存器:

节省了硬件空间,八位并行可以改为以为串行,在计算机中移位是乘法的重要的作用;

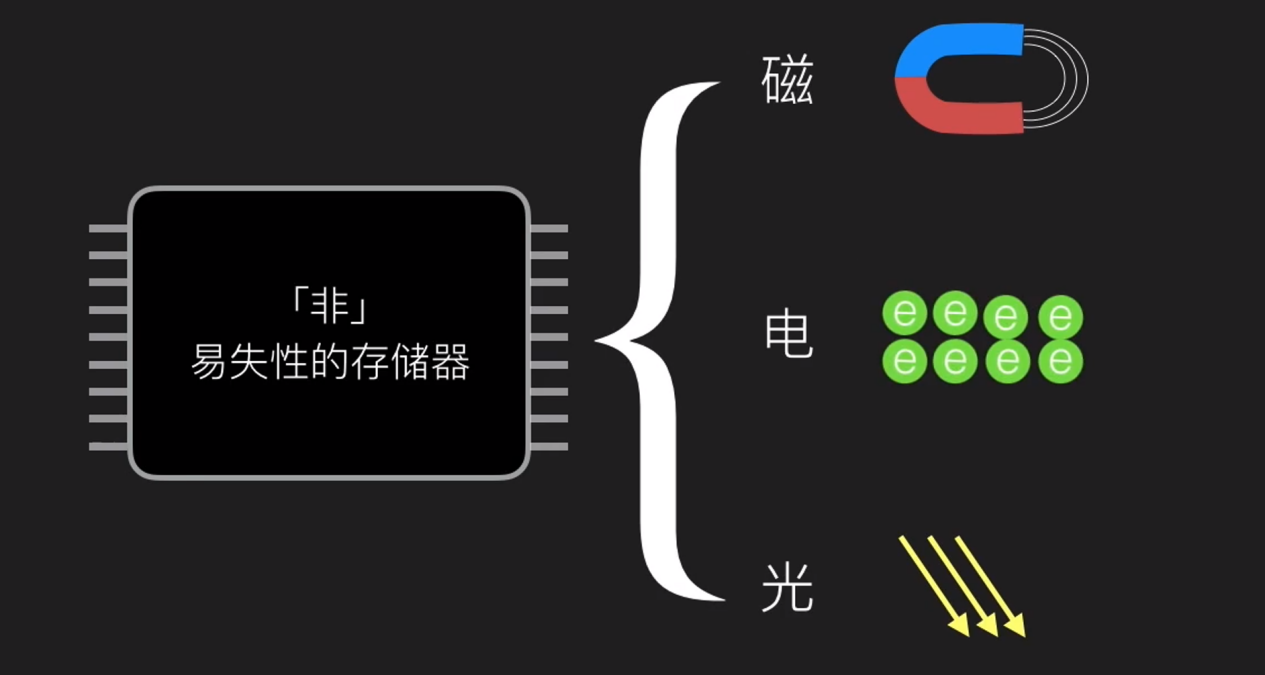

存储器

非易失性存储器:

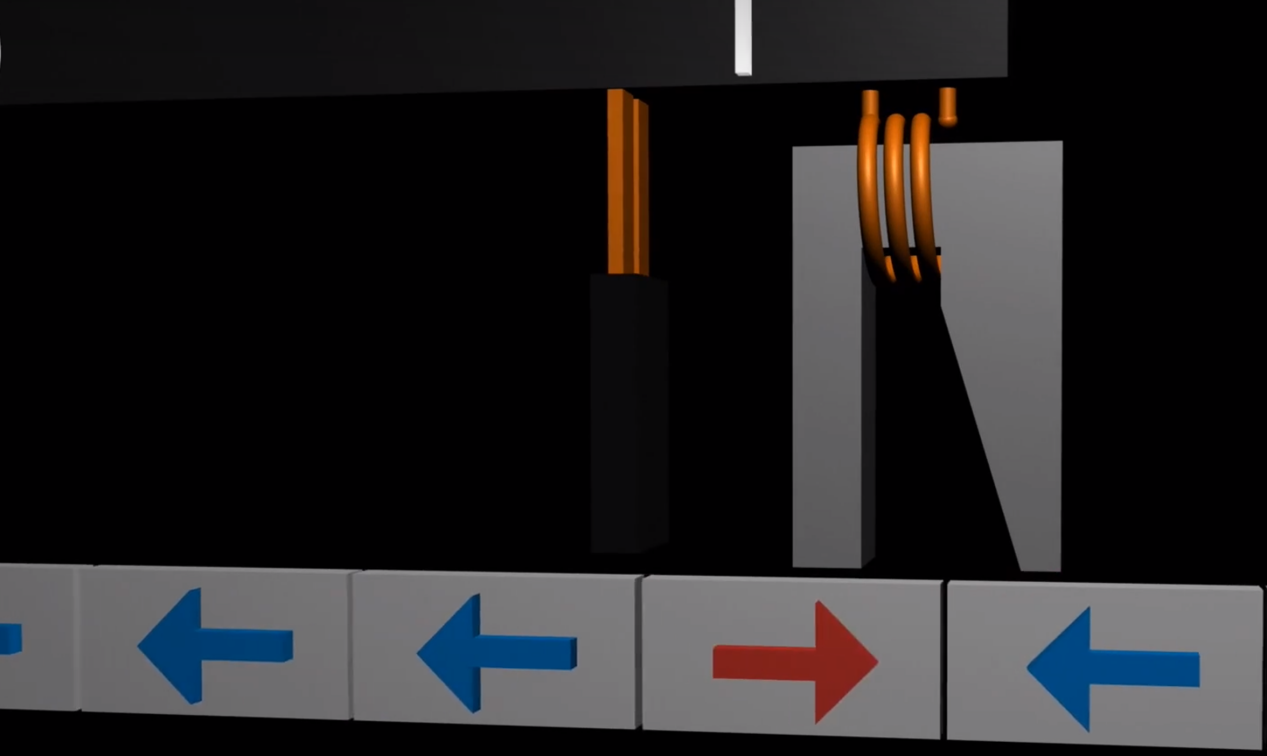

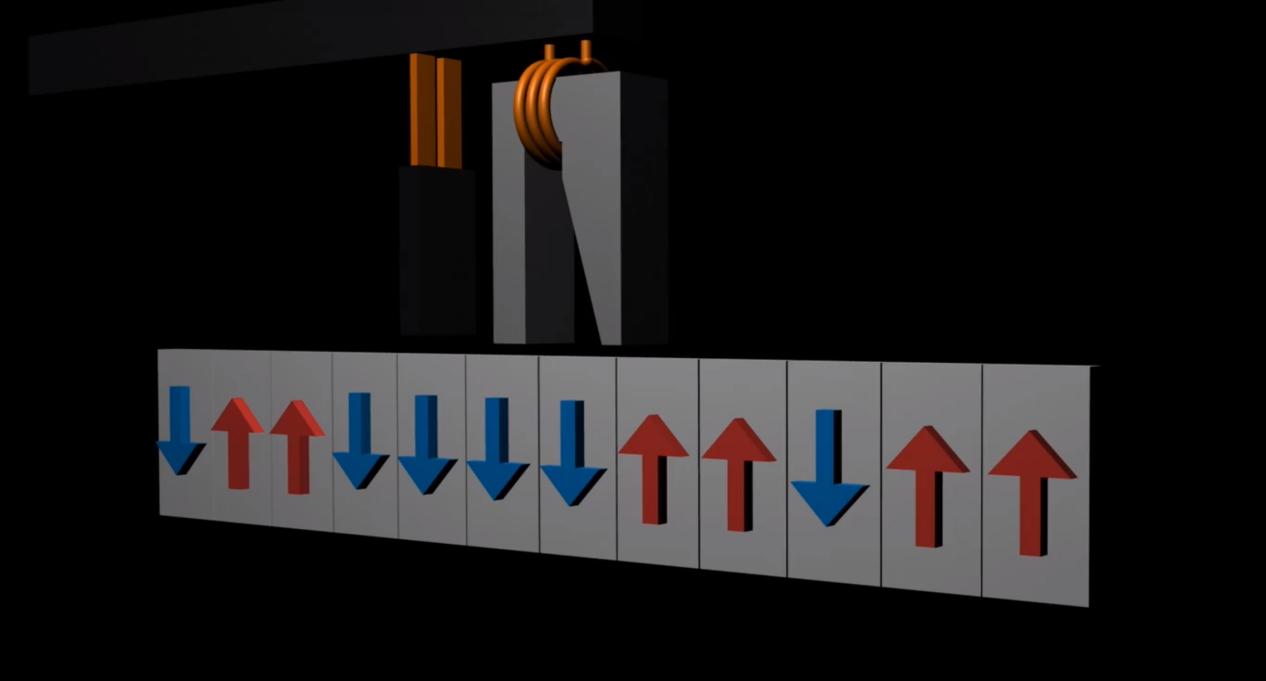

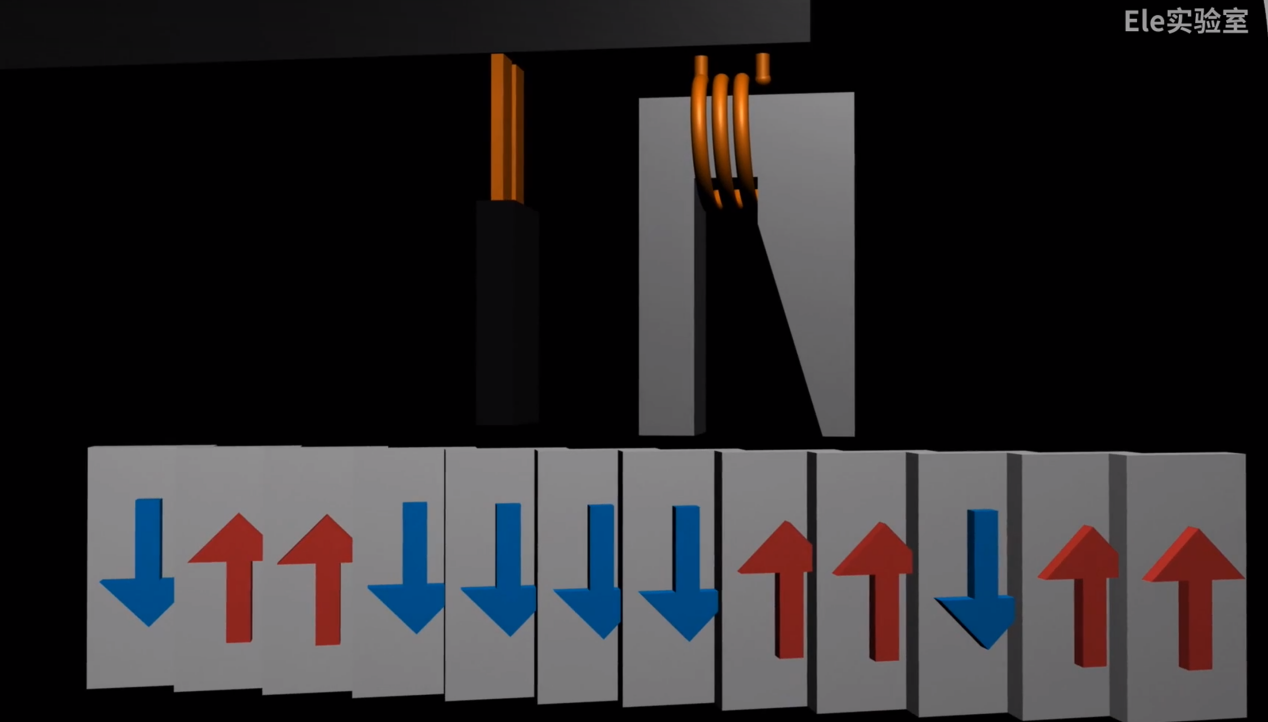

磁盘的写入:

电信号改变磁盘微粒的极性实现写入,读取则是由极性转换成电信号

提高了存储密度

叠瓦式:写入时容易影响附近的磁密度,所以会利用缓存来暂时存储不应该被修改的数据;

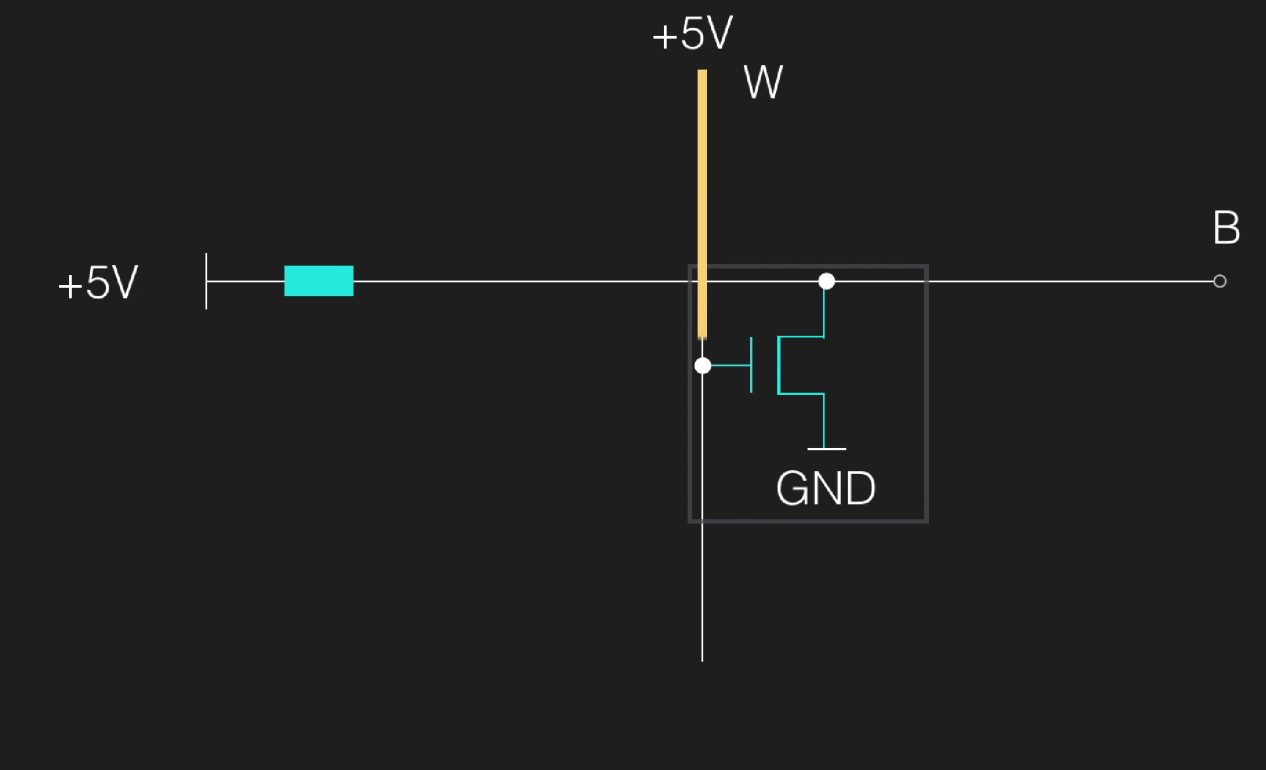

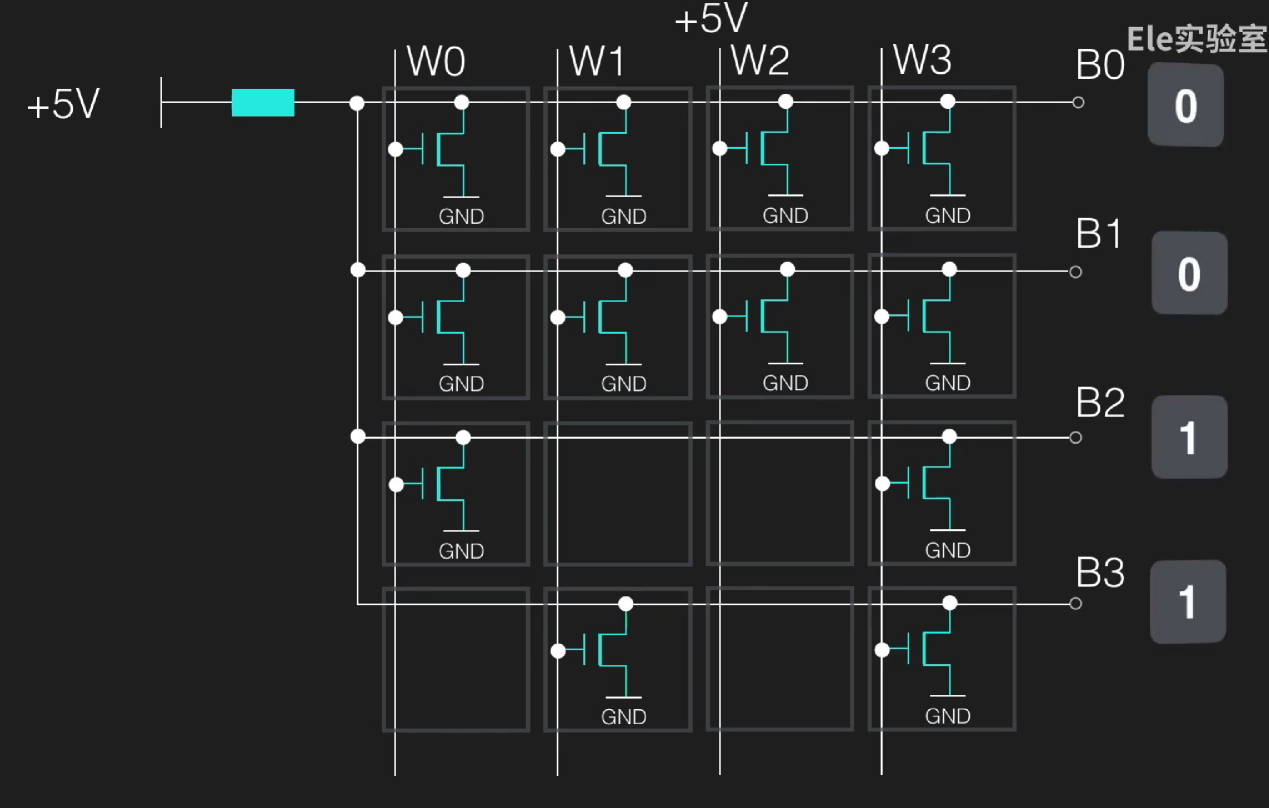

还记得cmos管吗?W导通时,cmos导通,电流流向GND;当W不导通时,B导通;起到存储一位比特的目的

这就是掩膜rom

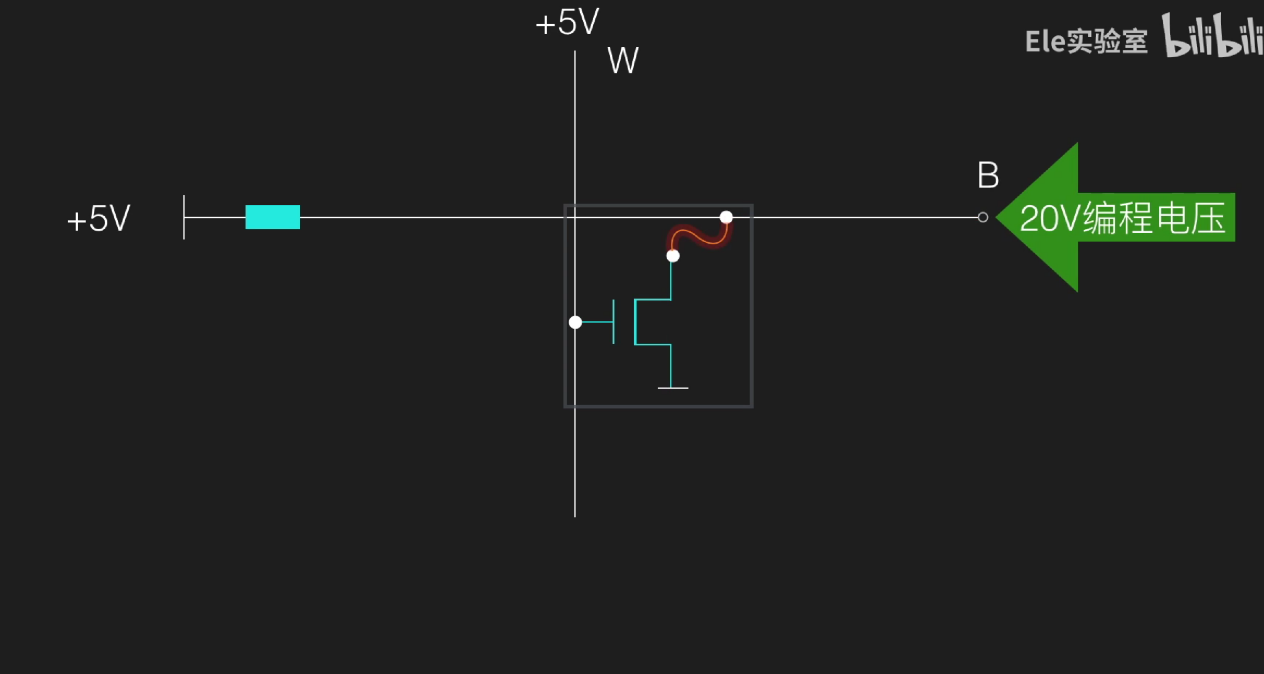

在CMOS间加入一个低熔点的导线,写入时加高压,导丝熔断这就是PROM(可编程ROM)这就是烧录一词的由来;

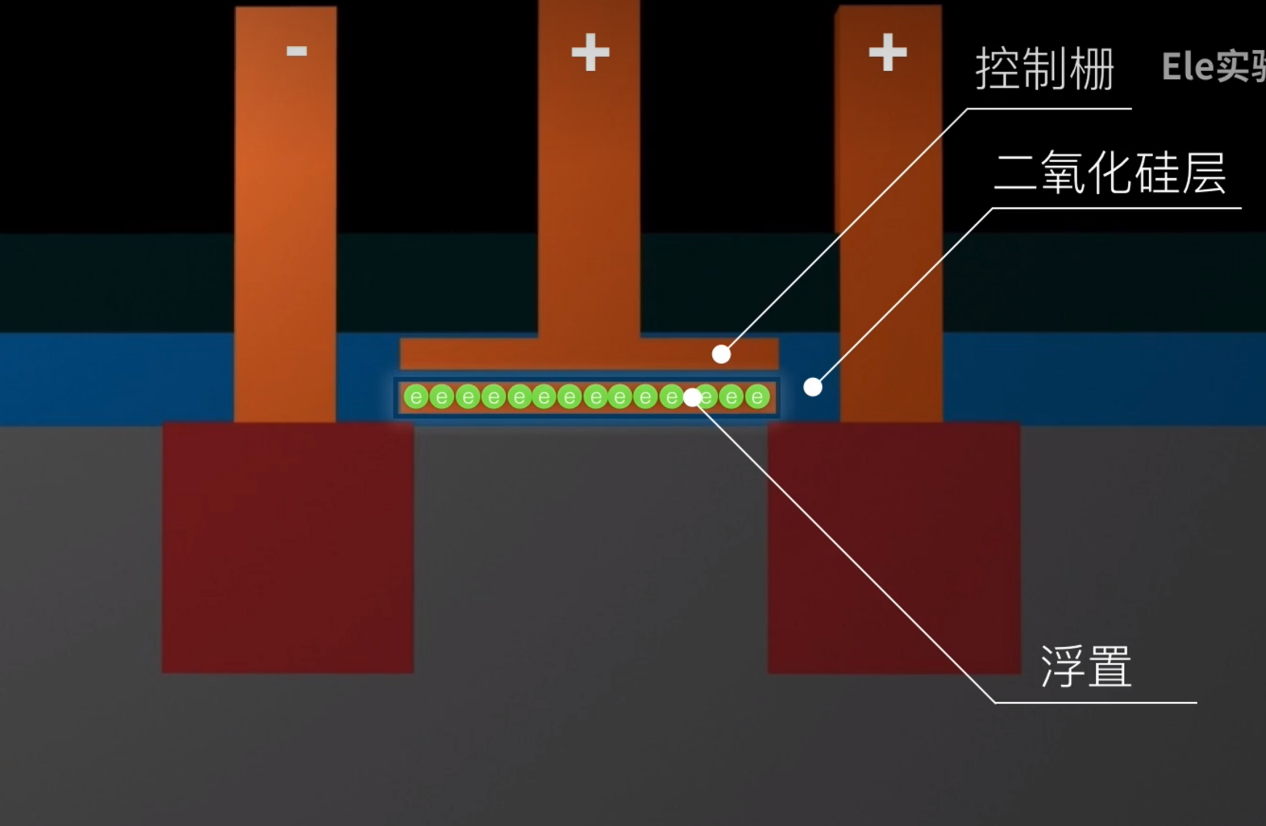

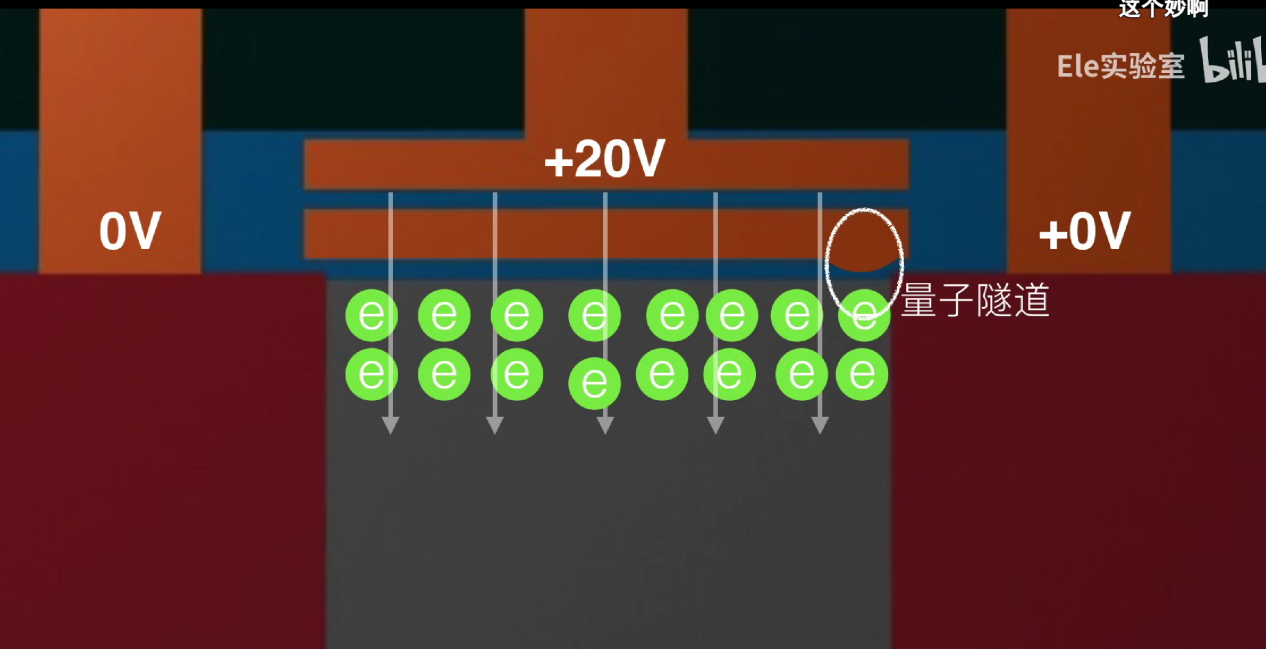

在原有cmos管上再加入一个浮置栅,浮置栅代电子是,控制栅产生的电场被消除,管子断开,而浮置栅处于二氧化硅中,电子不会离开;可以起到有目的存储的作用

穿透过程用热电子击穿

擦除使用紫外线

这就是Erasable Programmable Read-Only Memory(EPROM)

现在的ROM利用电搽除(EEPROM)

颗粒分类:

-

SLC (Single-Level Cell):

-

每个存储单元只能存储1位数据(二进制位)。

-

特点是速度快、寿命长,具有更高的稳定性和更低的错误率。

-

因此,SLC NAND 通常用于高性能的企业级应用。

-

由于成本较高,现在比较少见于消费市场。

-

-

MLC (Multi-Level Cell):

-

每个存储单元可以存储2位数据。

-

相比SLC,它的容量加倍,但速度稍慢,寿命也较短。

-

MLC NAND 提供了一个较好的性价比平衡点,常用于高端消费者SSD和一些企业应用中。

-

-

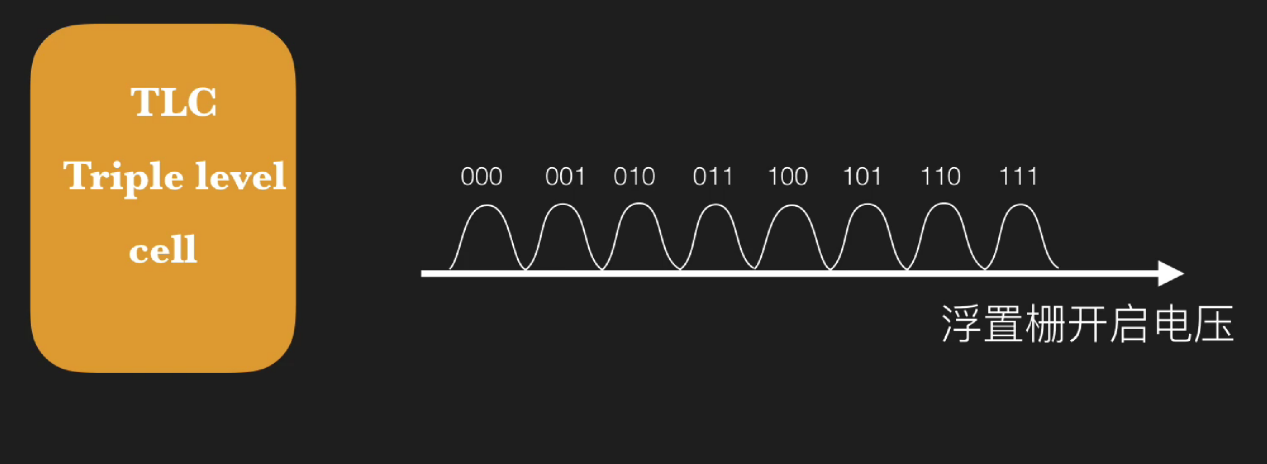

TLC (Triple-Level Cell):

-

每个存储单元可以存储3位数据。

-

这种类型的NAND提供了更大的容量,但是其写入速度、擦写周期寿命都低于MLC。

-

TLC NAND 成本较低,因此广泛应用于消费级SSD和其他大容量存储设备。

-

-

QLC (Quad-Level Cell):

-

每个存储单元可以存储4位数据。

-

它提供了最大的存储密度,但同时拥有最短的使用寿命和最低的写入速度。

-

QLC NAND 主要用于对成本敏感的大容量存储解决方案,如高密度SSD或数据中心中的冷数据存储。

-

本质是开启电压分为不同精度,如slc只分为开启和断开就只能存储一位,TLC如下图

RAM

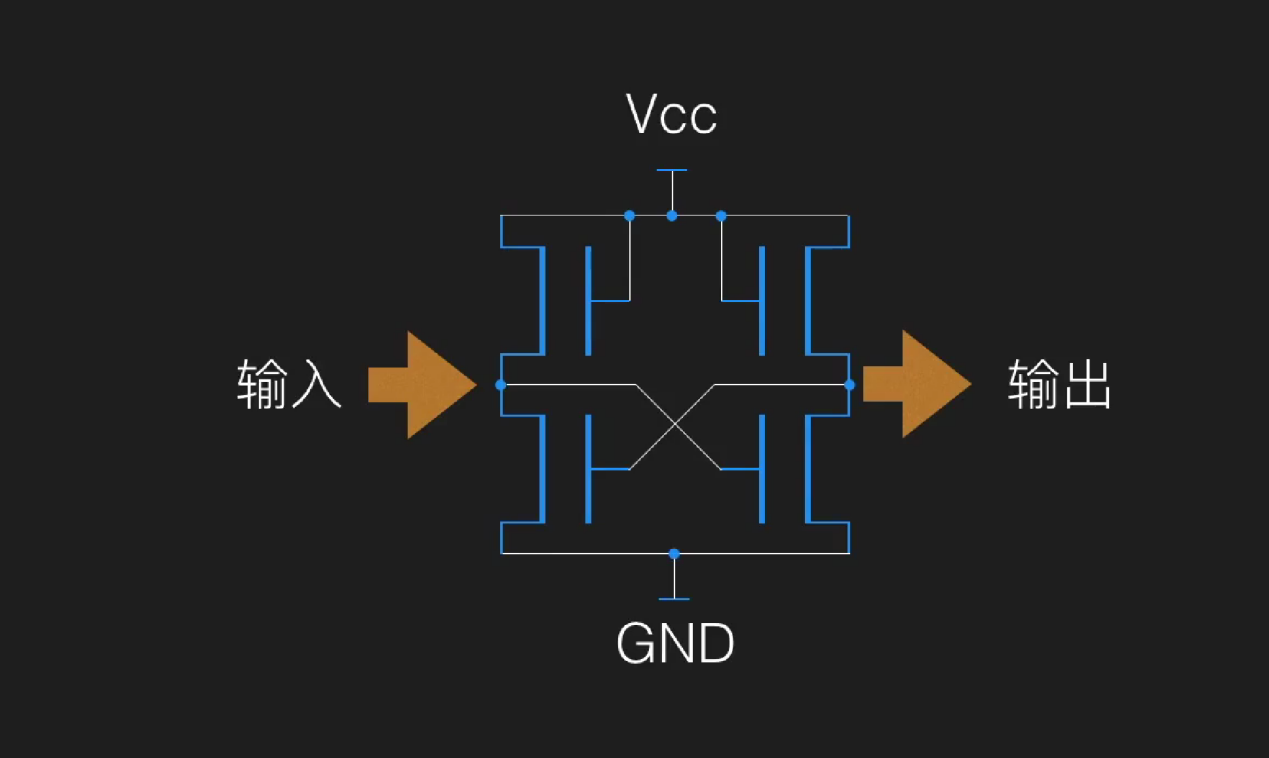

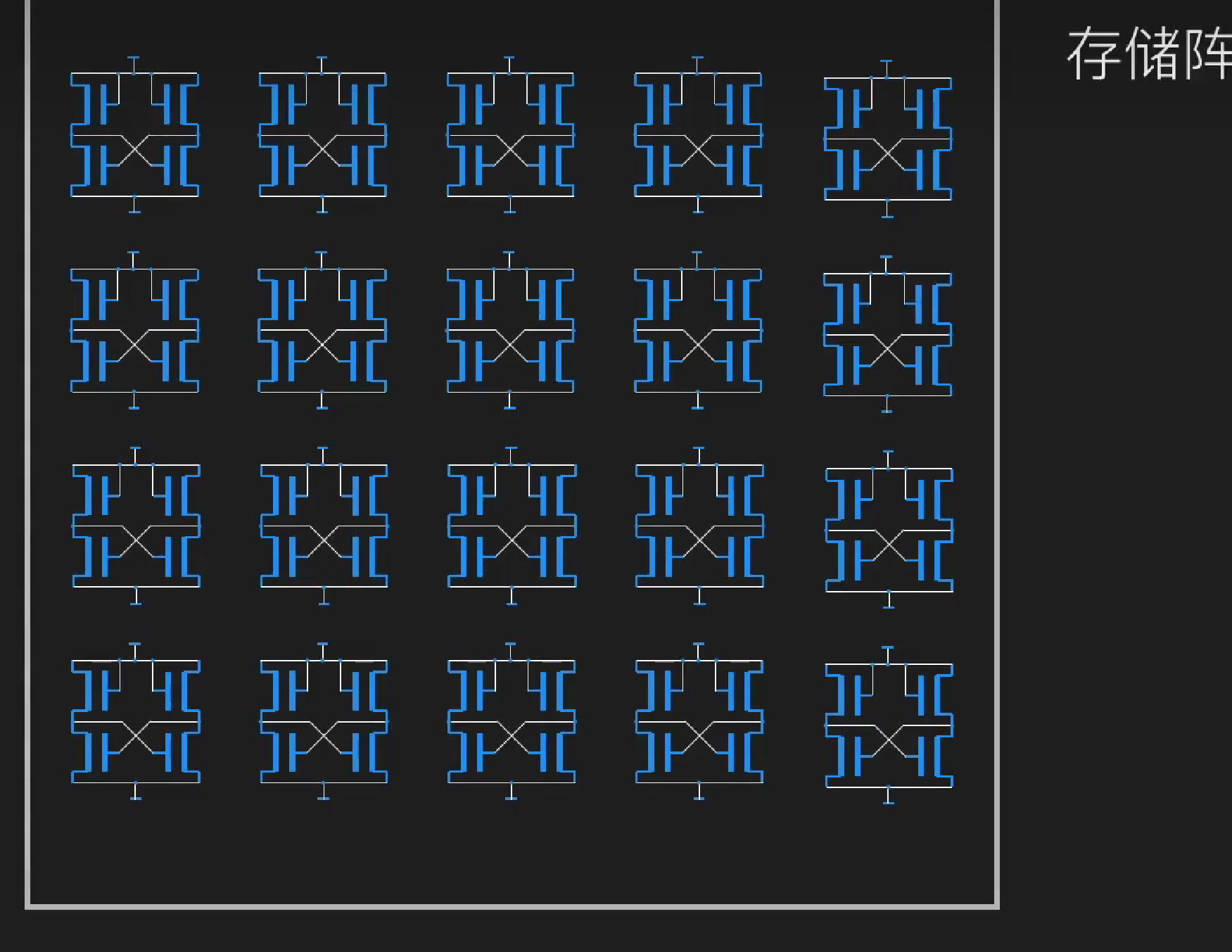

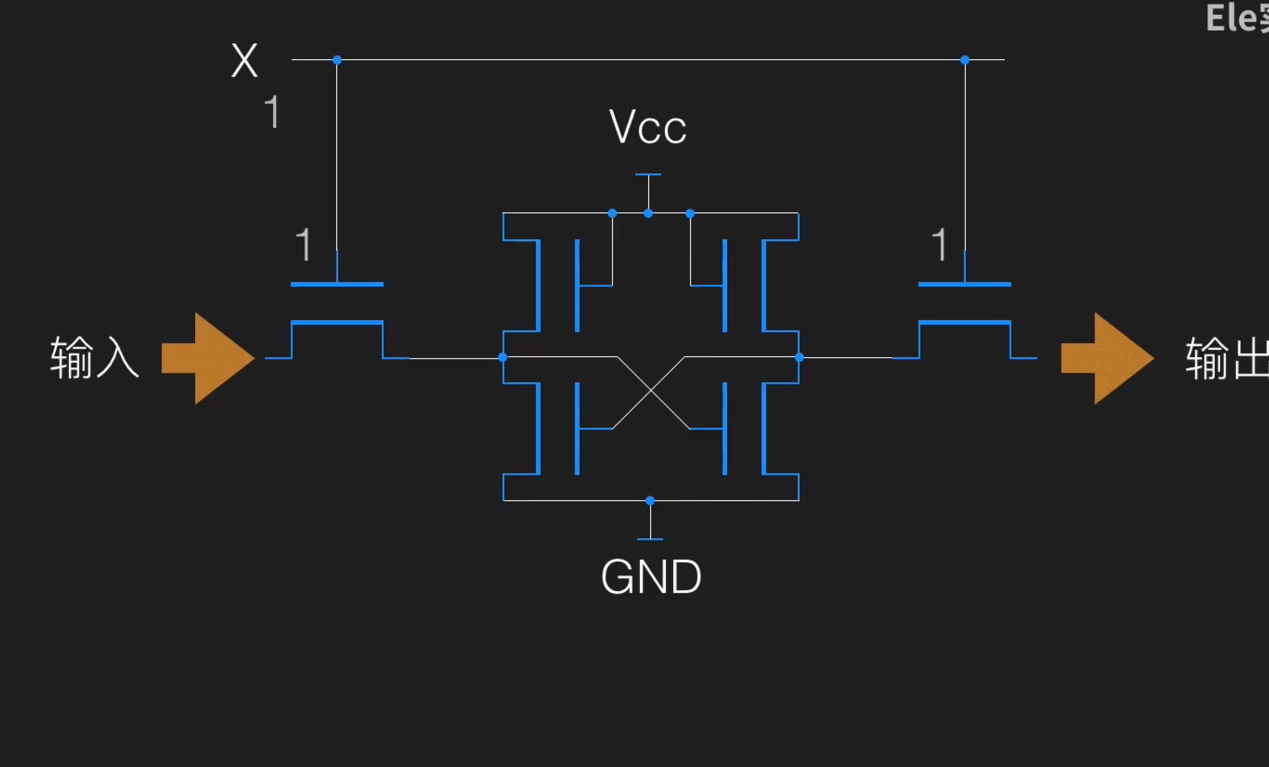

4个mos管组成的 一位存储器;

存储单元;

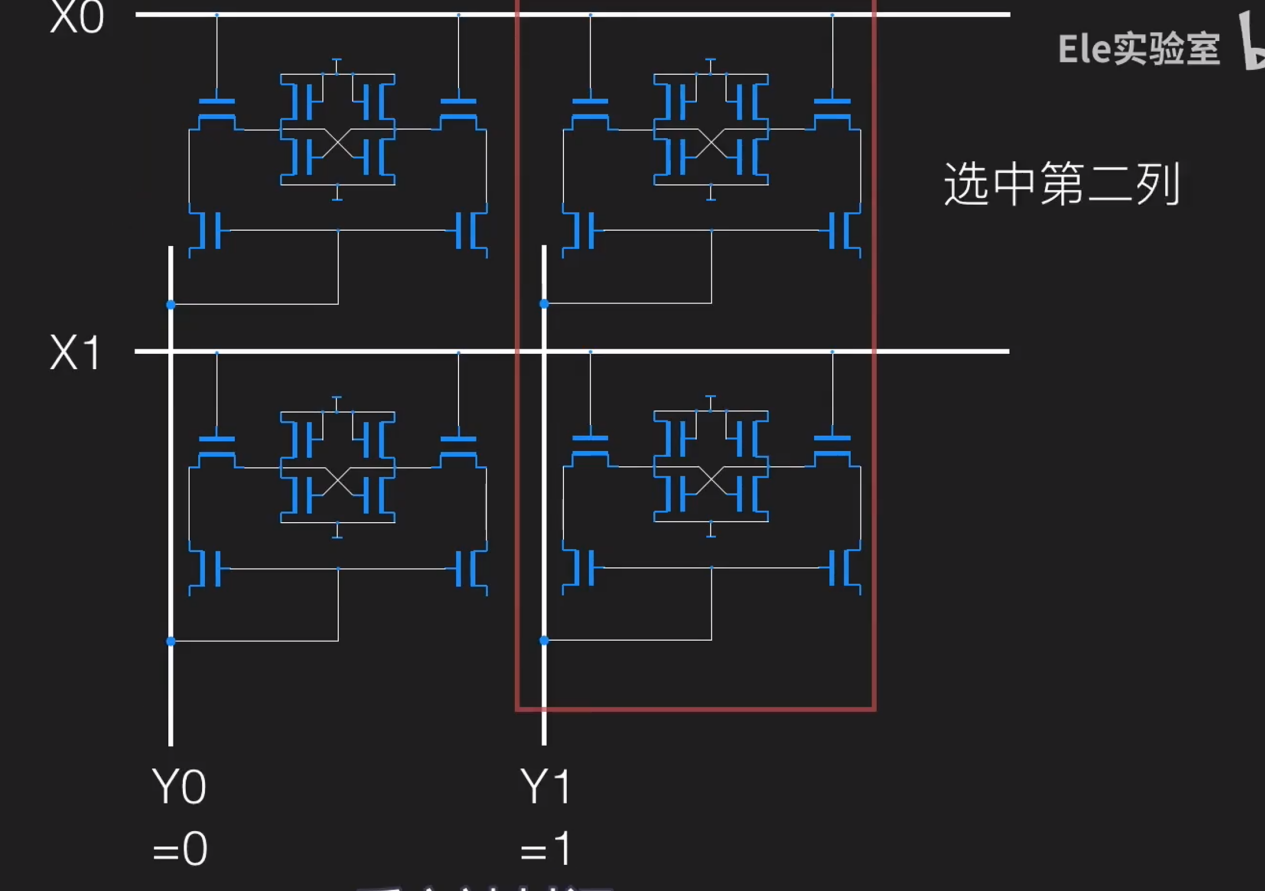

等于1导通,0时断开,在内存中选择xy线确定内存单元

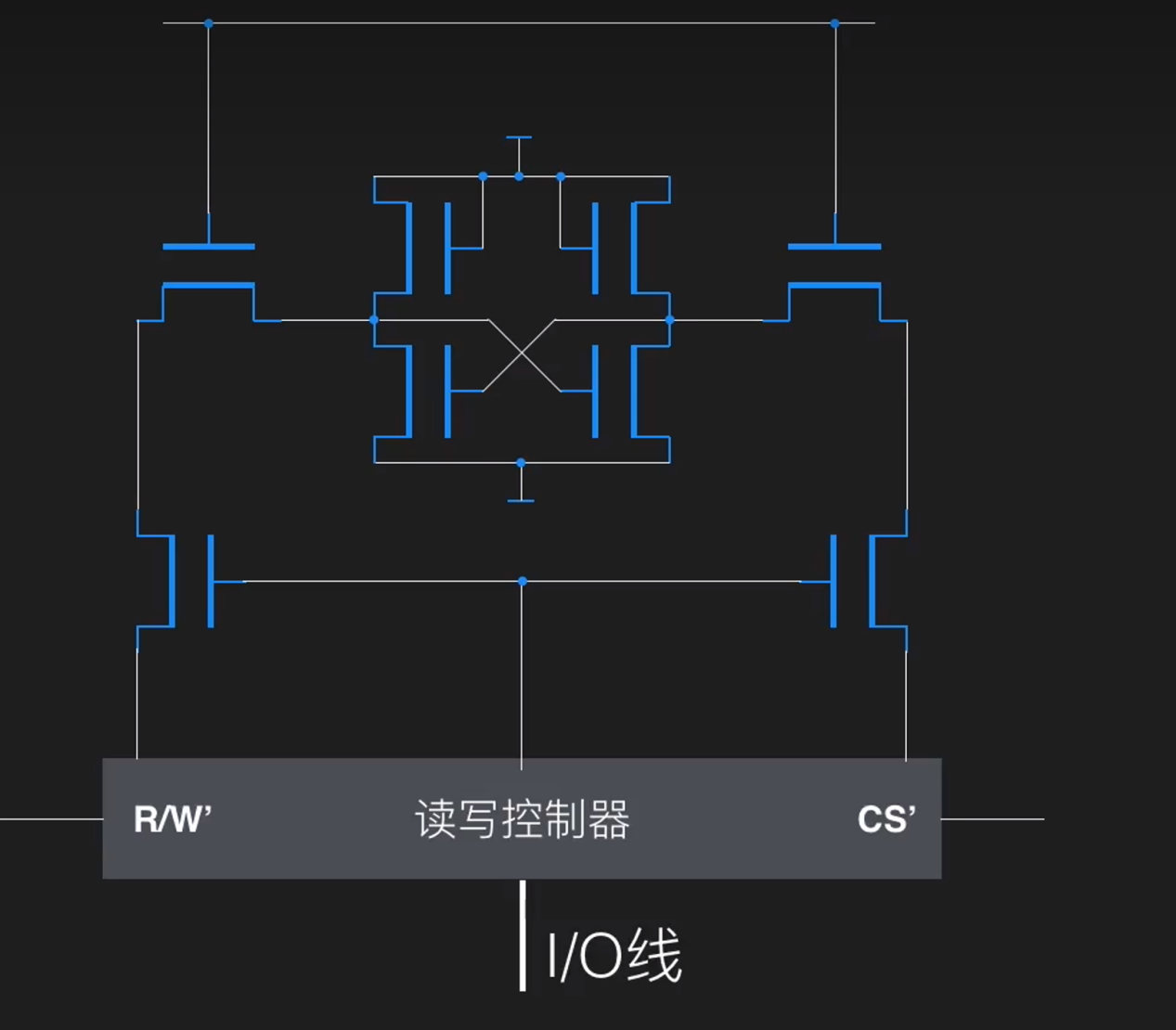

读写控制器 cs’=0 可读可写,=1时被锁死(应用于高速缓存)

X=1时,mos导通可以控制电容的充电与放电(数据的写入)x=0,电容被封锁数据就被保存;

读取时,x=1,电容数据流向左侧的电容,被读取但右侧电容电荷流失,所以需要定期刷新(所以称为动态RAM DRAM,前者称为SRAM,静态RAM)补充电荷,读取时还需要放大微弱的电流信号所以,外围电路更加复杂。

DDR

在同步脉冲信号工作的RAM称为 SDRAM(在异步脉冲信号工作的RAM称为 ADRAM)是现在的主流,一开始只有上升沿是驱动信号,在上升和下降沿都可以工作称为 double date rate (DDR)不同改进就是不同的ddr型号

计算机组成原理

冯诺依曼和哈弗

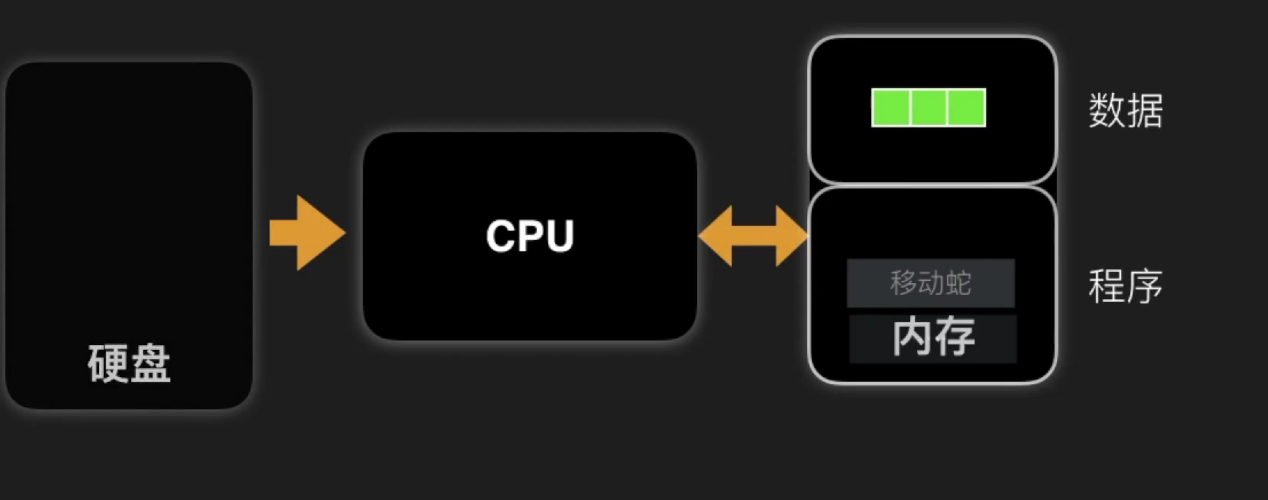

冯诺依曼架构:不区分程序和数据,灵活性高,调用程序时ROM中程序调入到RAM

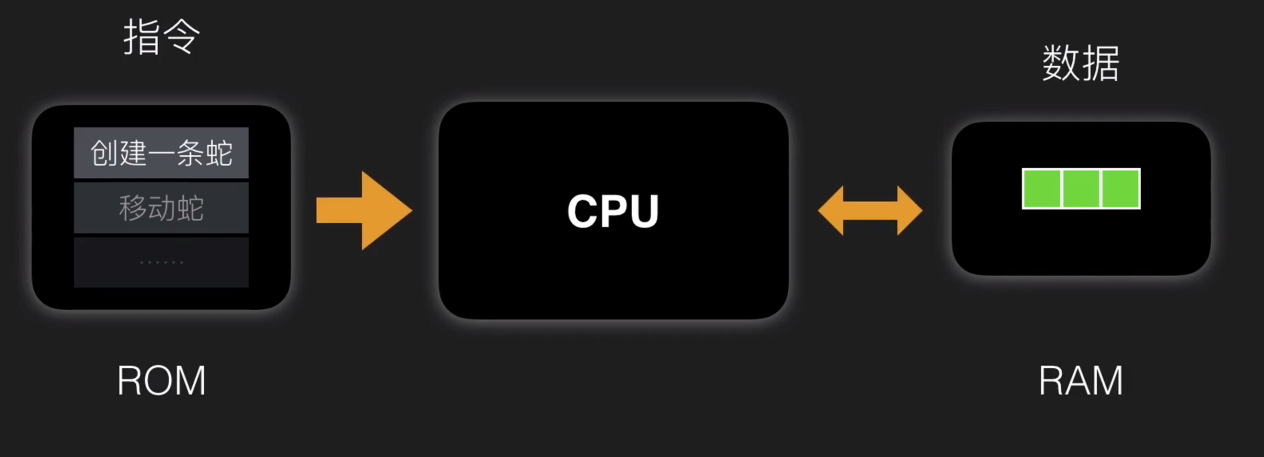

哈佛架构:简单,一般用于嵌入式设备

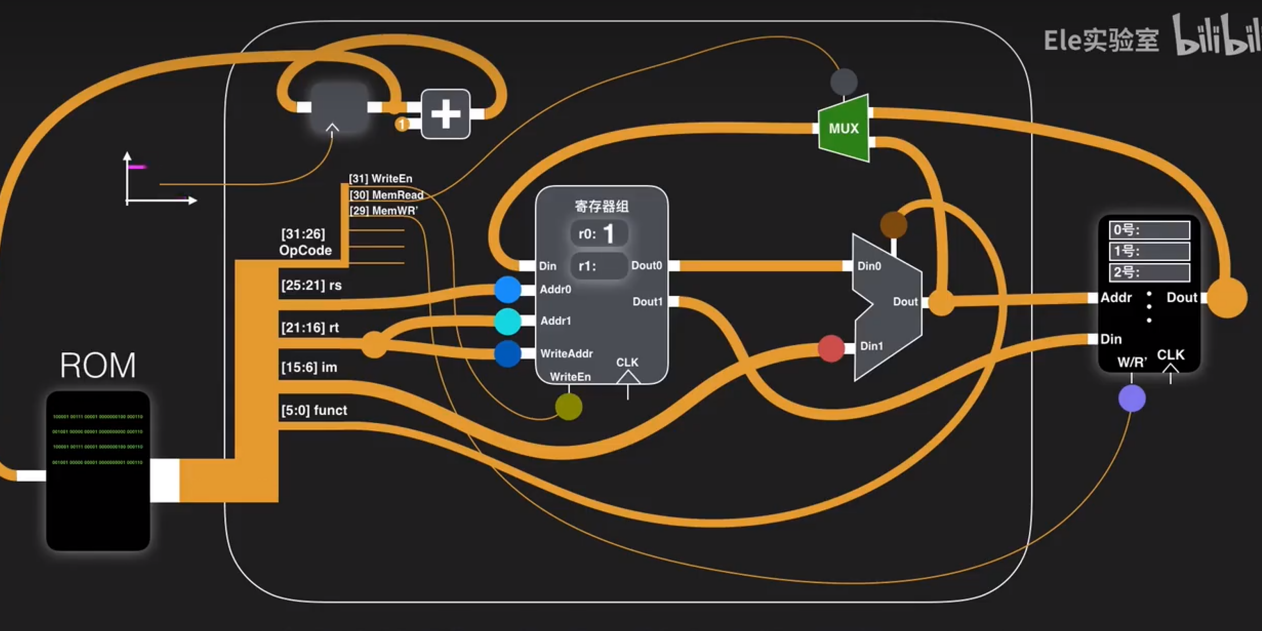

下面我们来设计基于哈佛架构的8位计算机:

ROM存储器

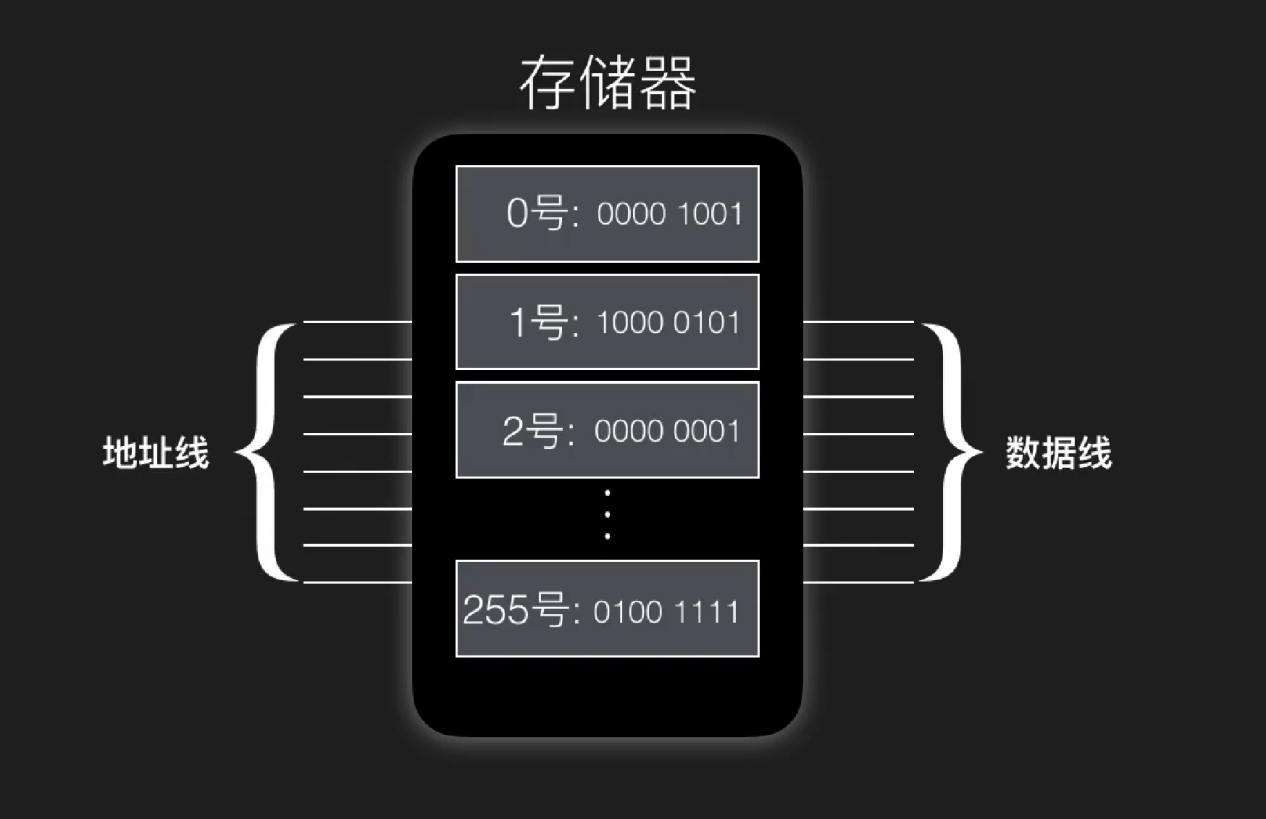

想像存储器是一个抽屉,每一格可以存储8位数据;地址线就是2的8次方(00000000到11111111),数据线就是2的3次方(比如想知道某个格子的数据就让地址线等于几)

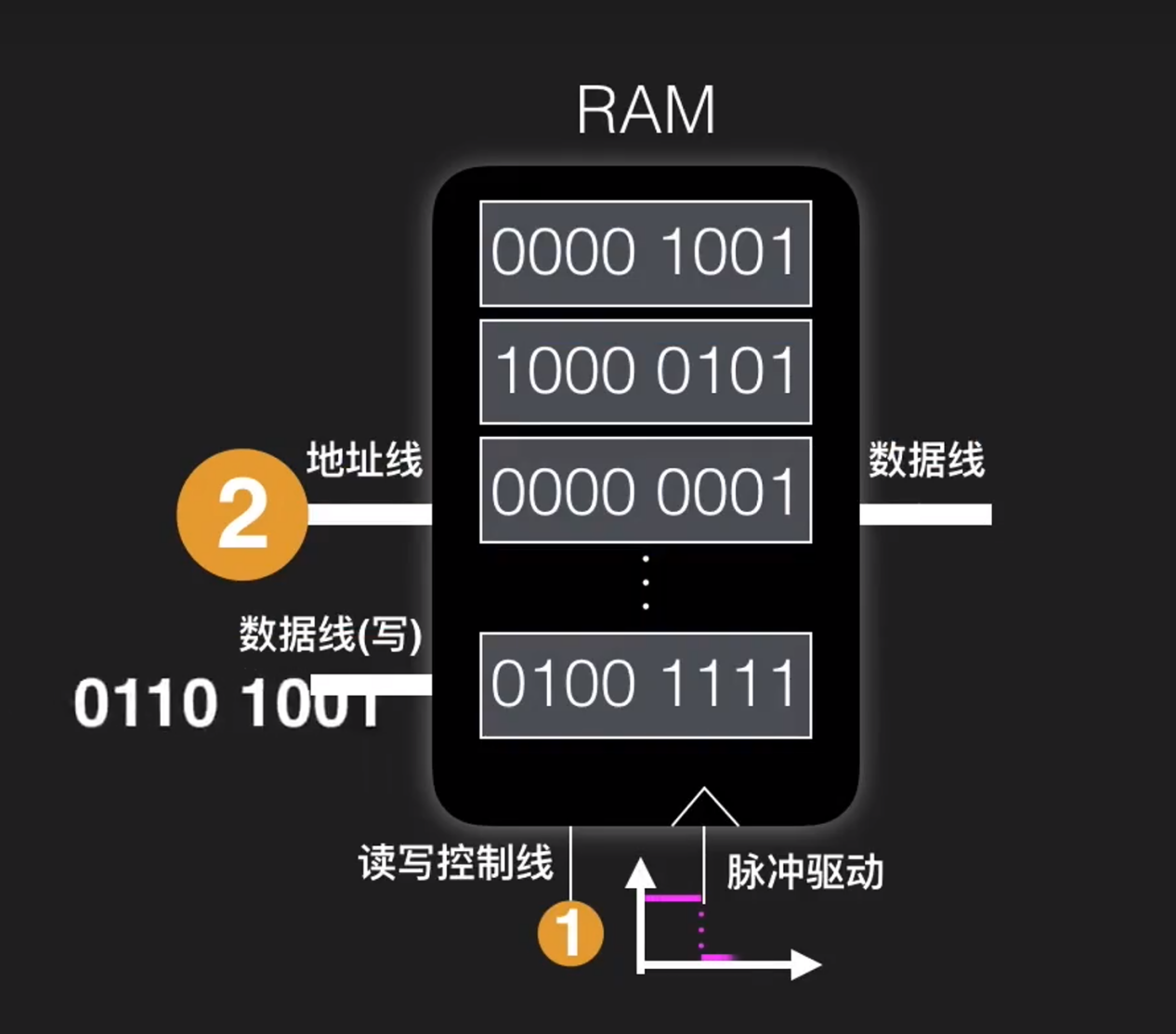

RAM

多一个读写控制线

读写控制线=0,读模式

写时 读写控制线=1 当有一个脉冲信号时,写入数据;

CPU:

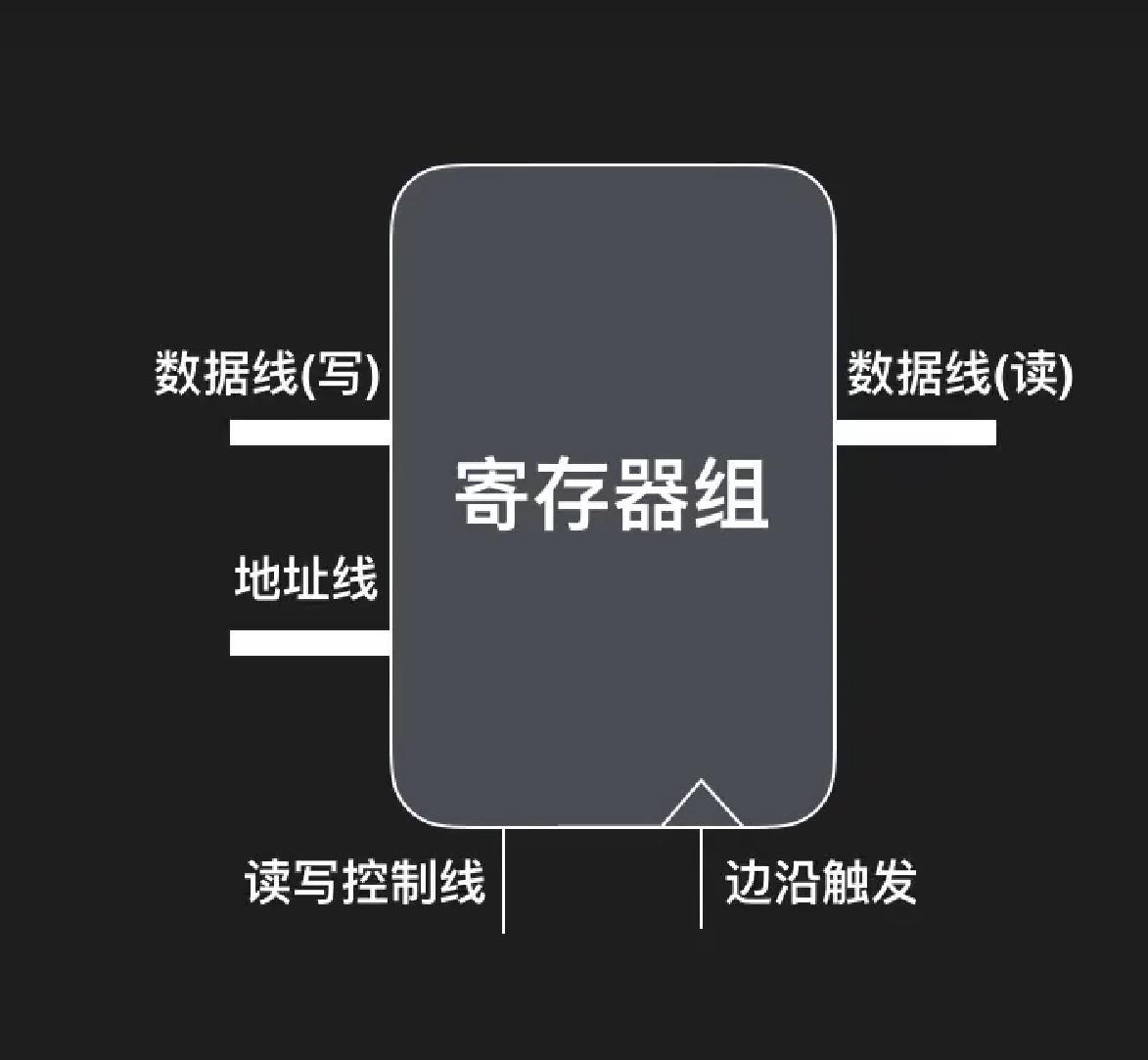

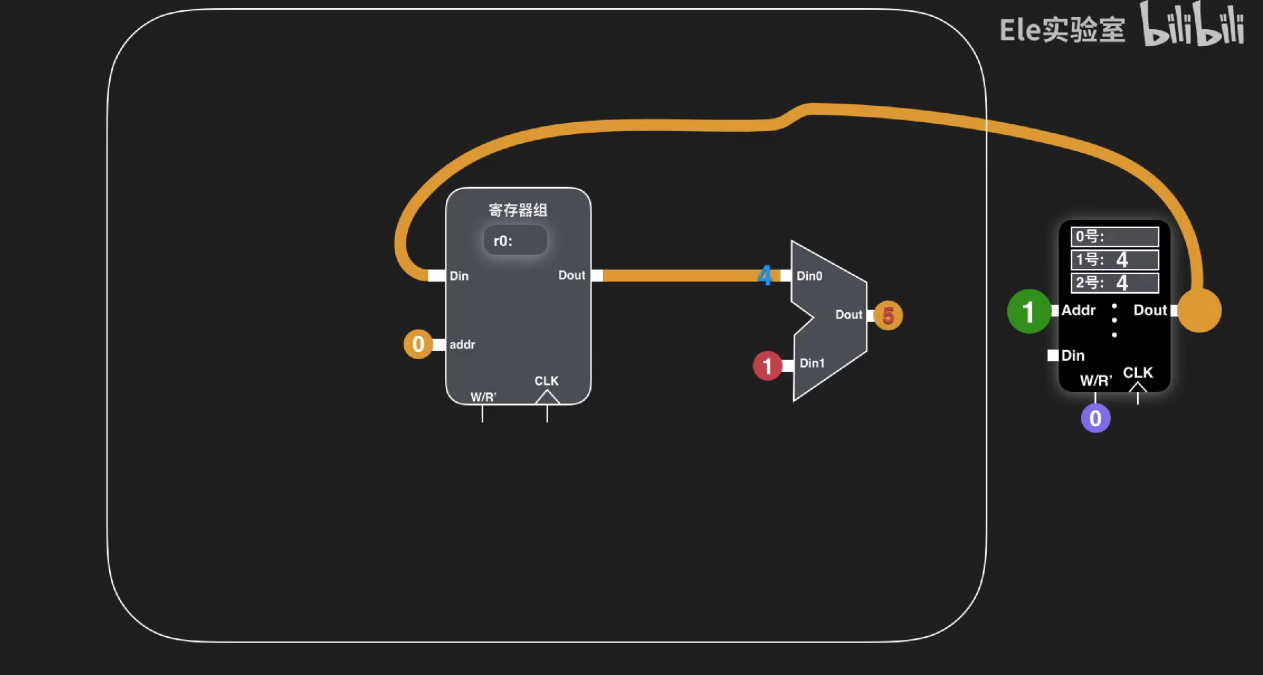

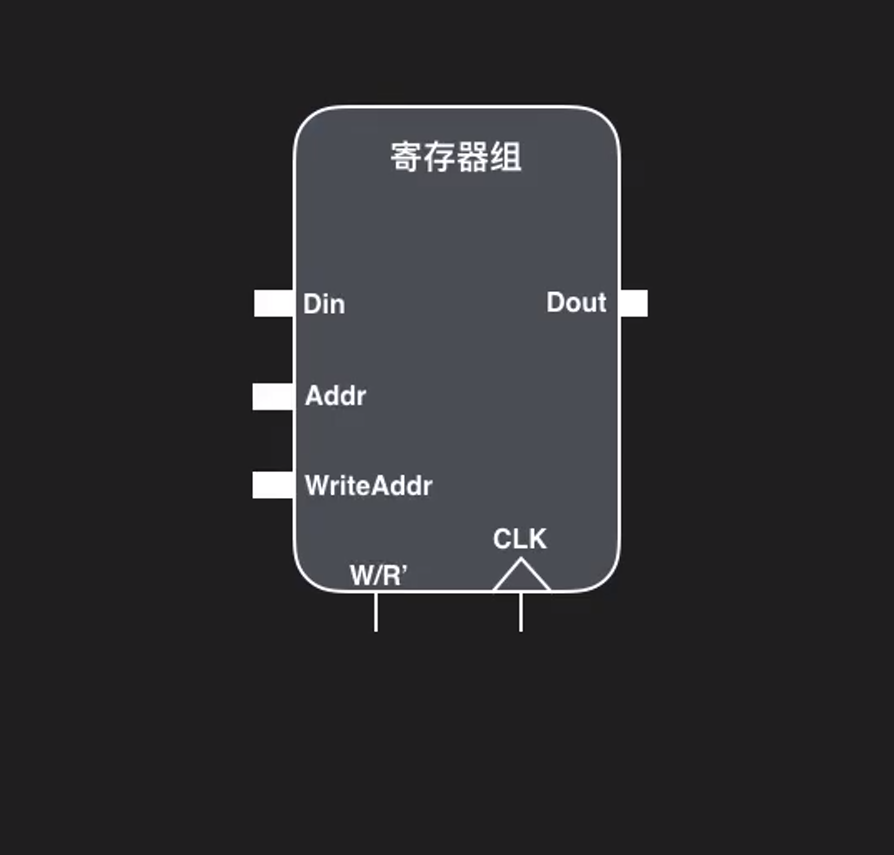

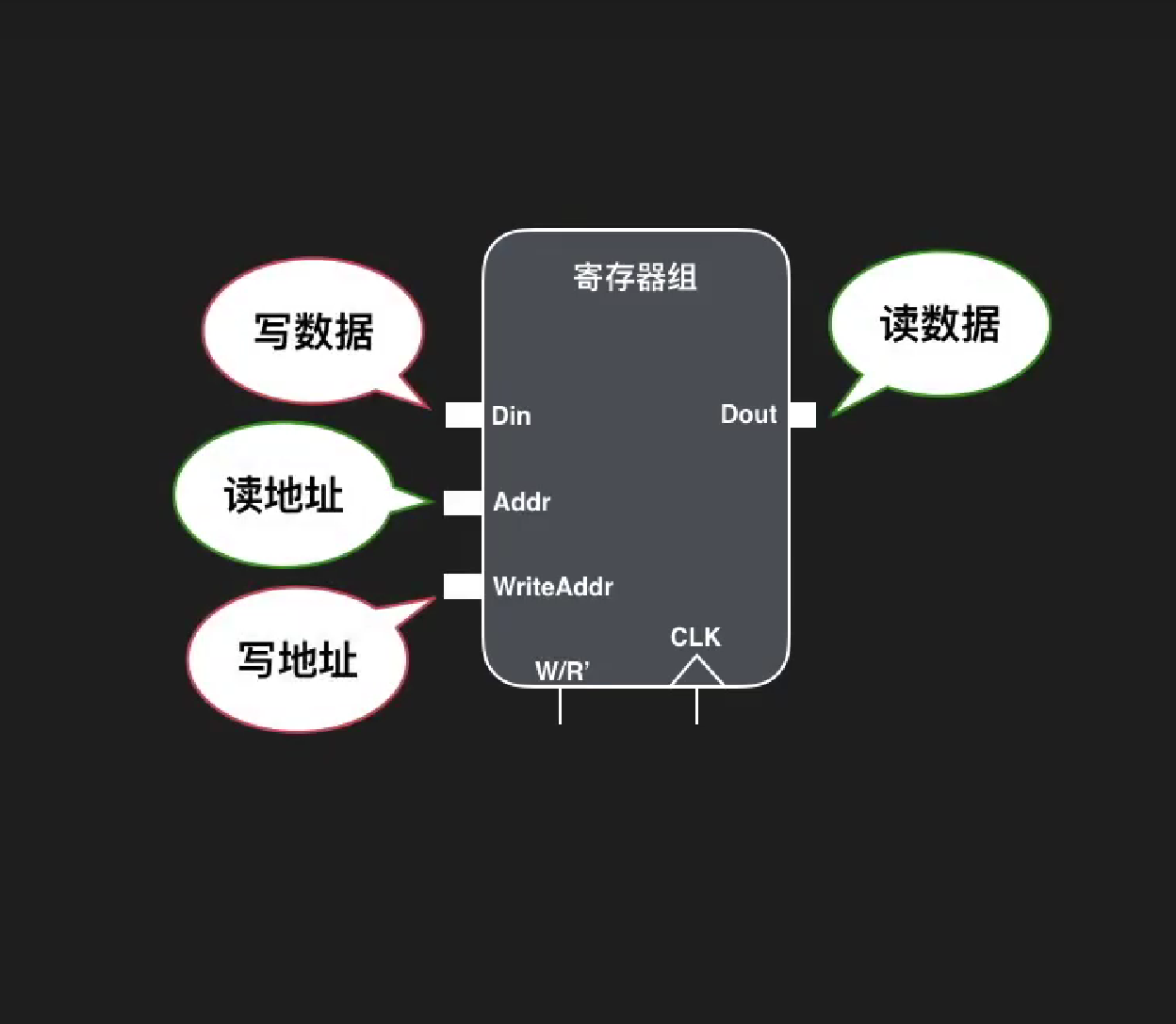

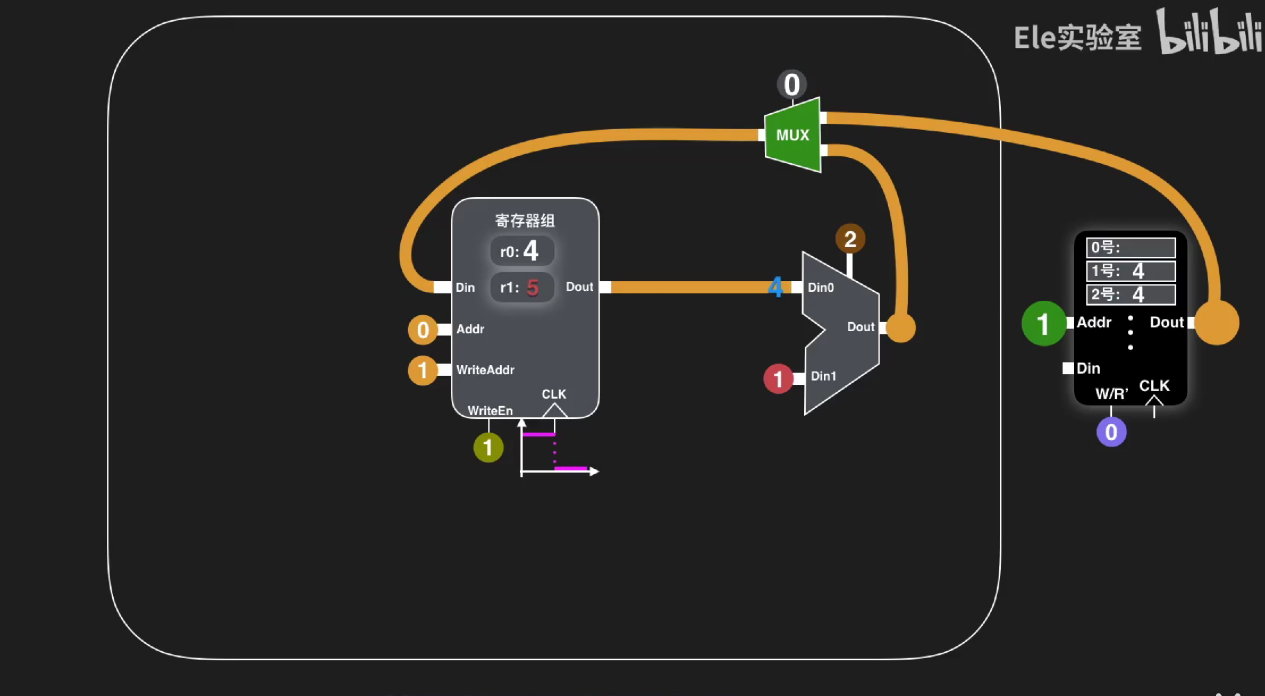

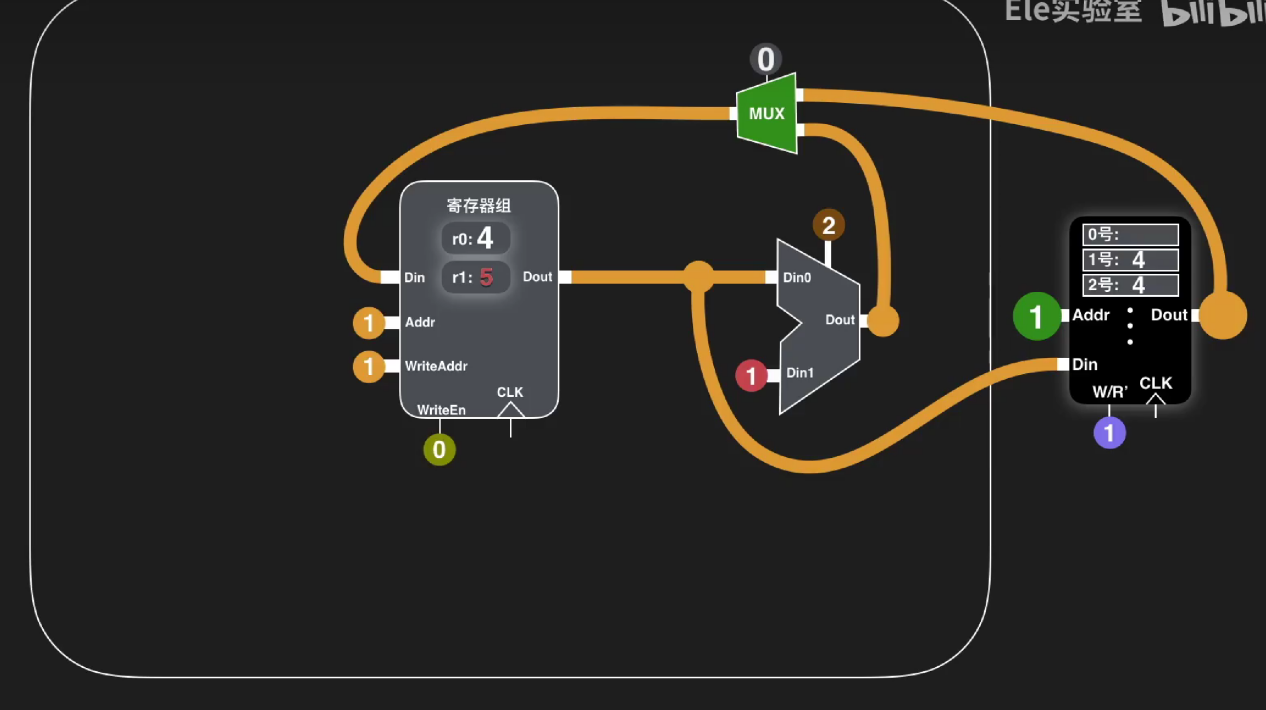

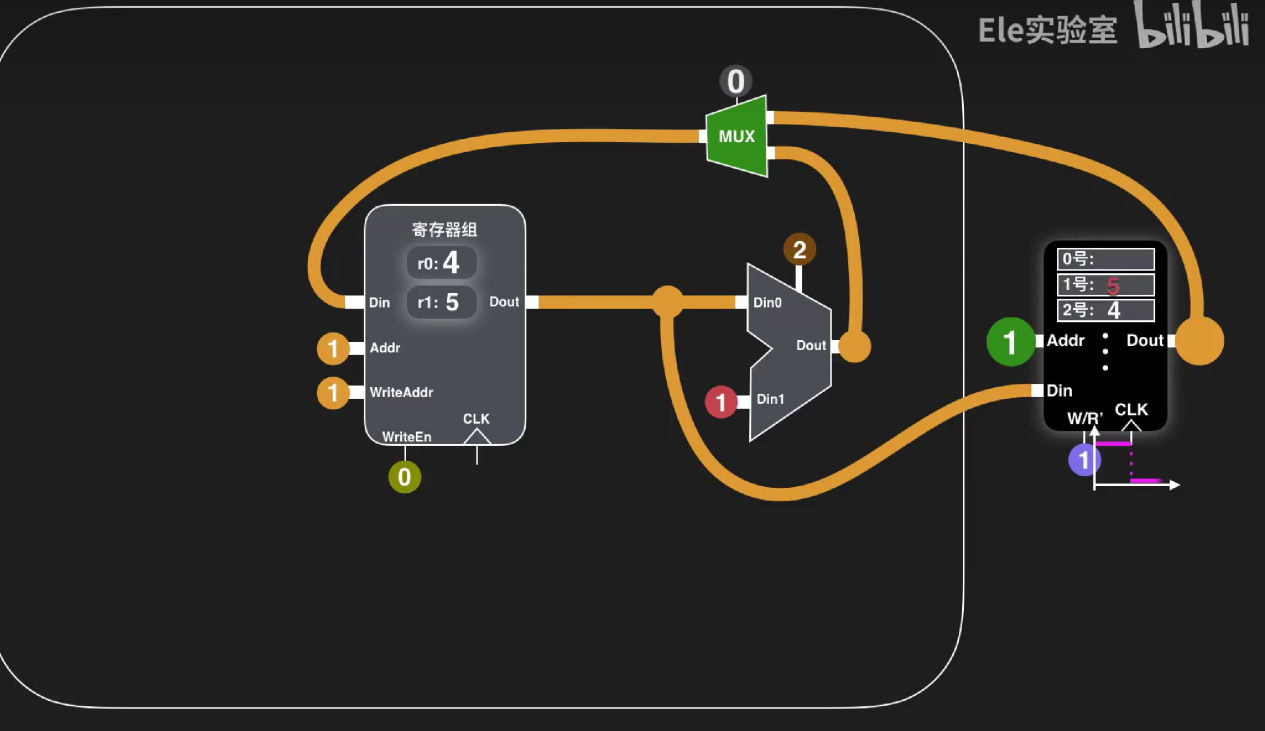

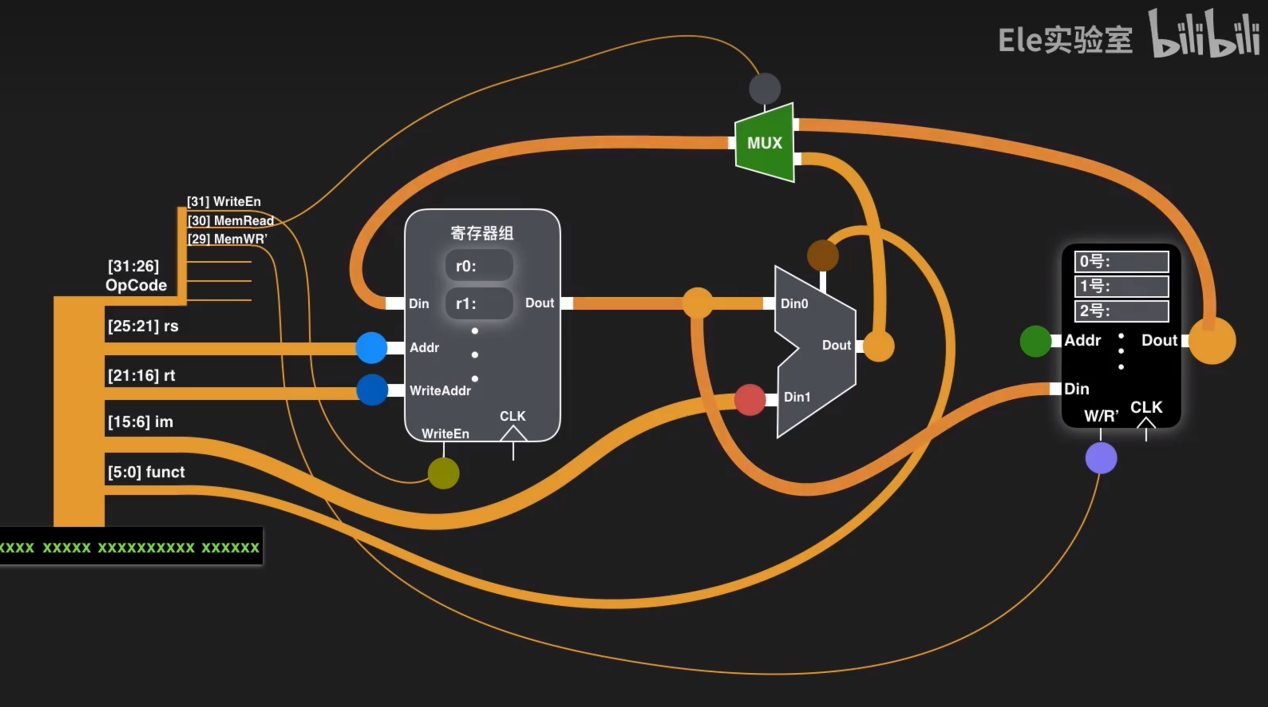

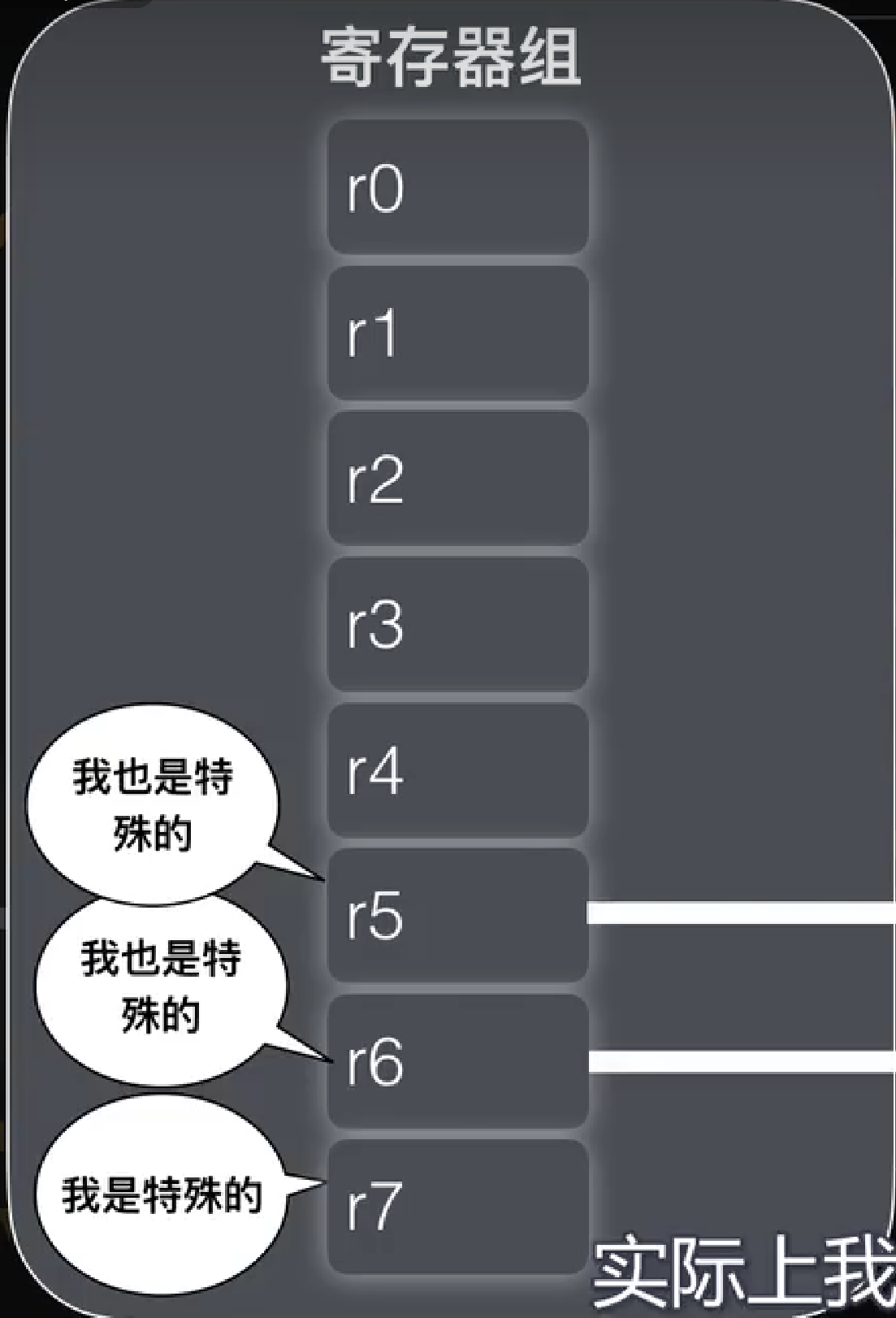

寄存器组(锁存器结构)与RAM大致相似

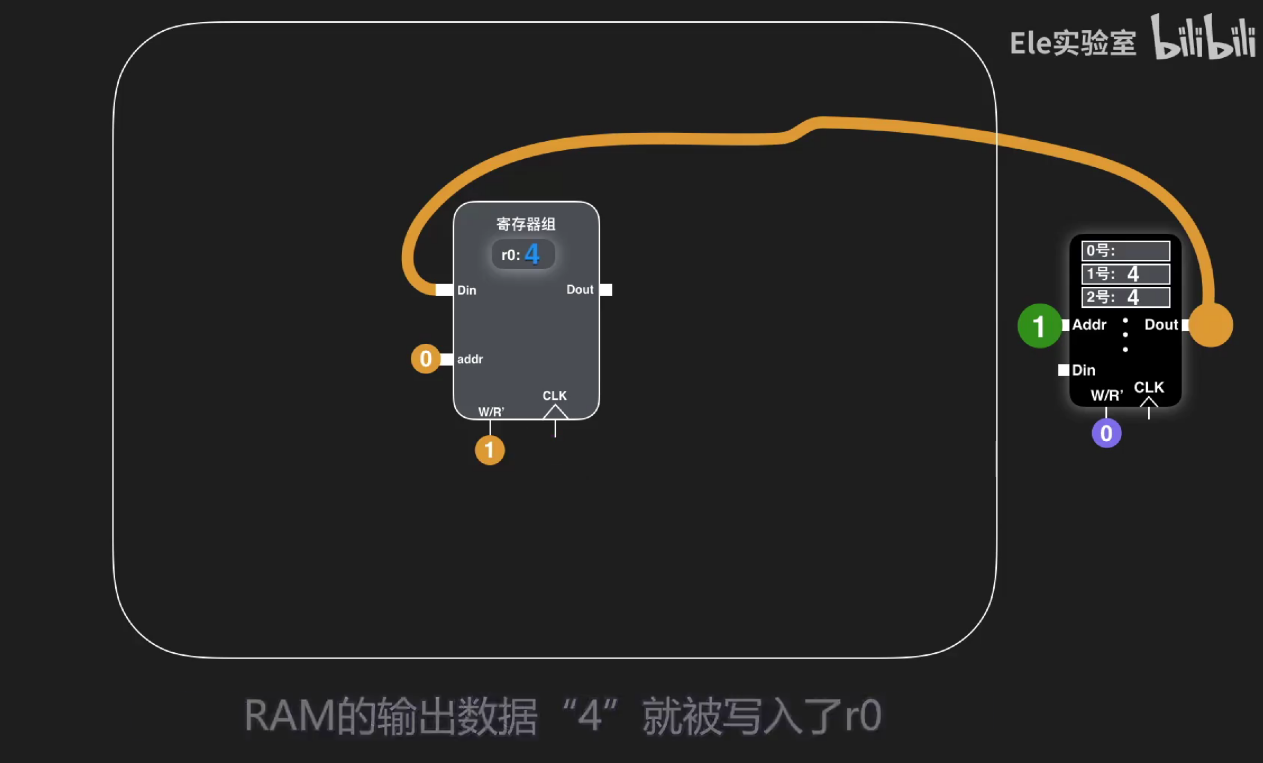

数据读写都必须经过寄存器组;在RAM中写了两个2个数据相当于(int x = 4;

int y = 4;)

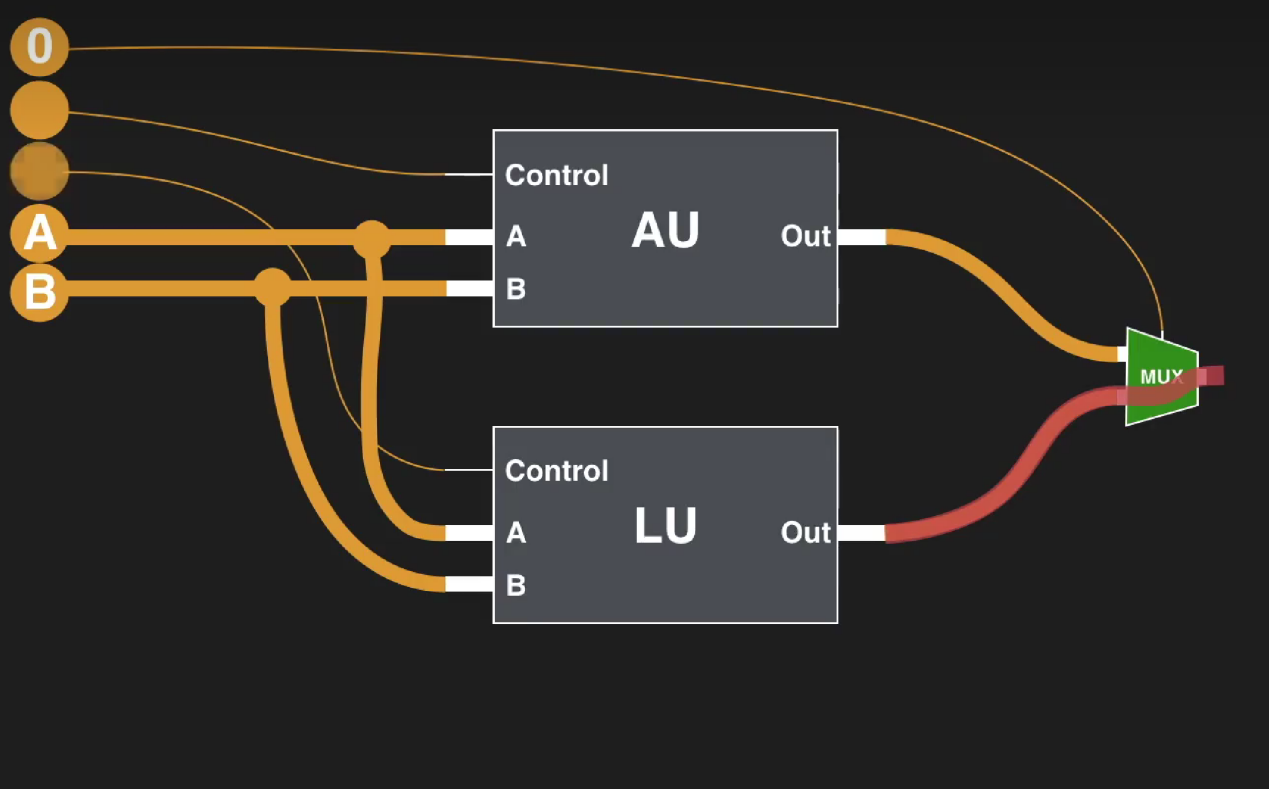

运算器:

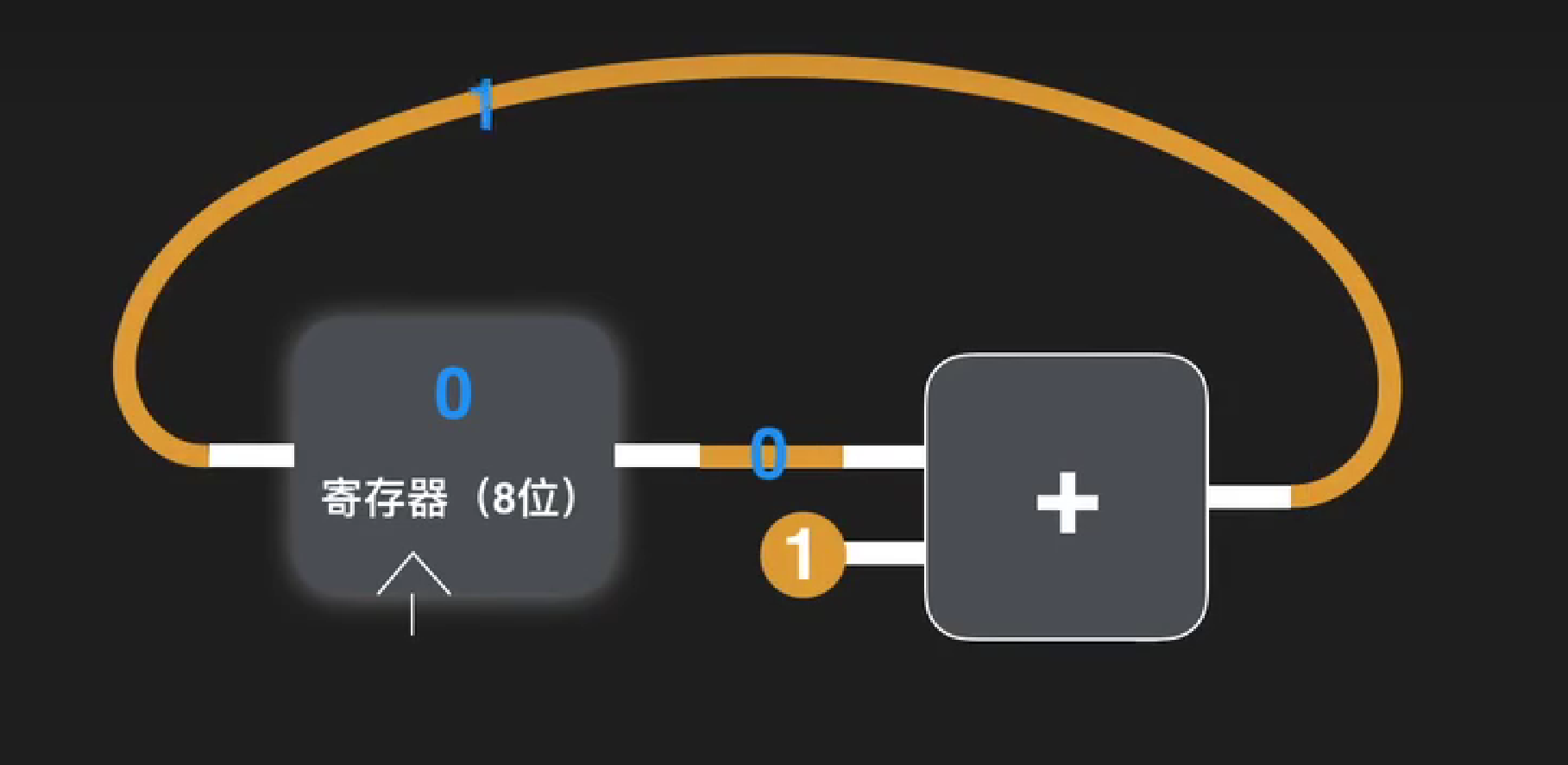

进行加1运算

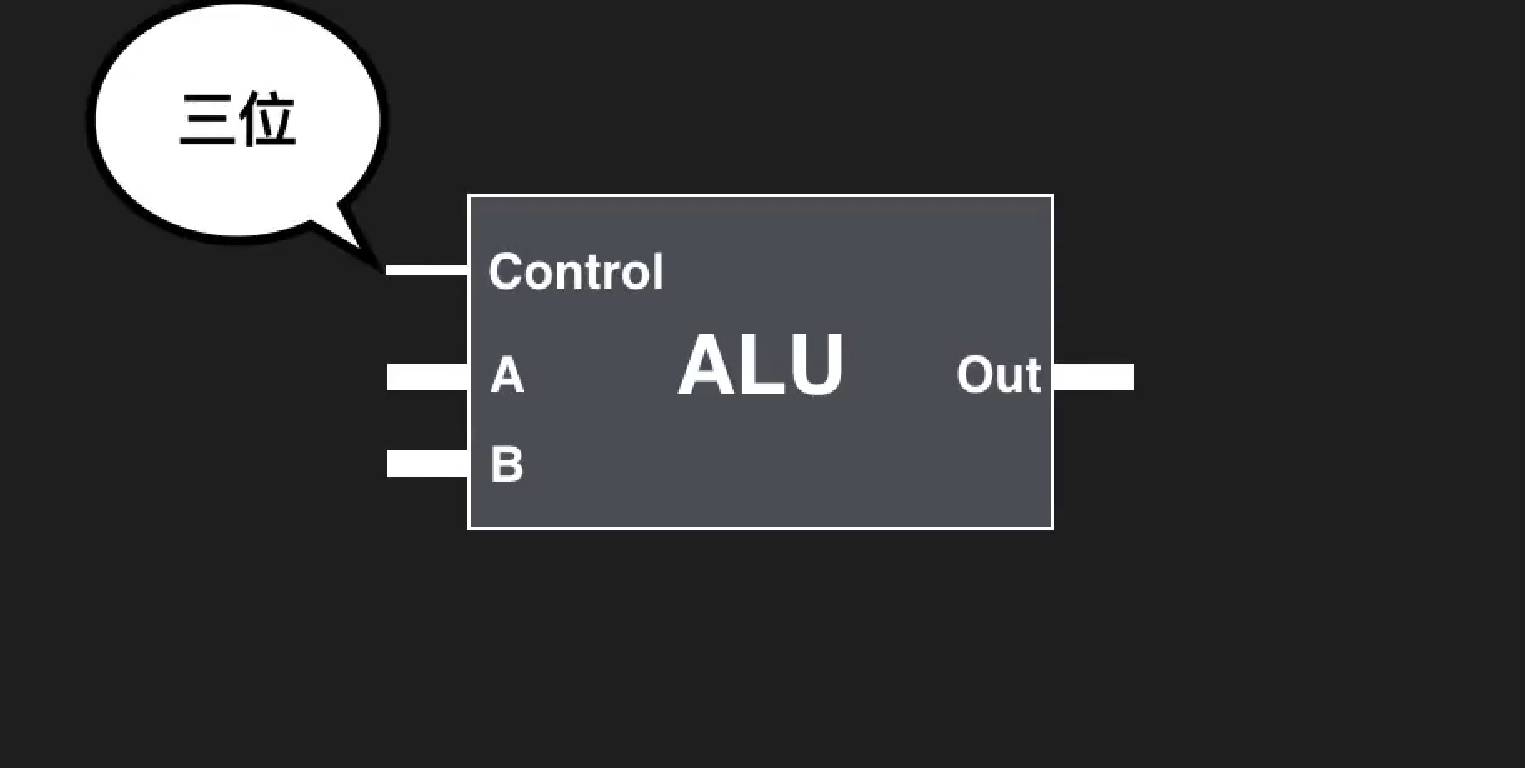

运算器可以进行多种运算,一位的控制信号显然不够,所以控制信号有4位

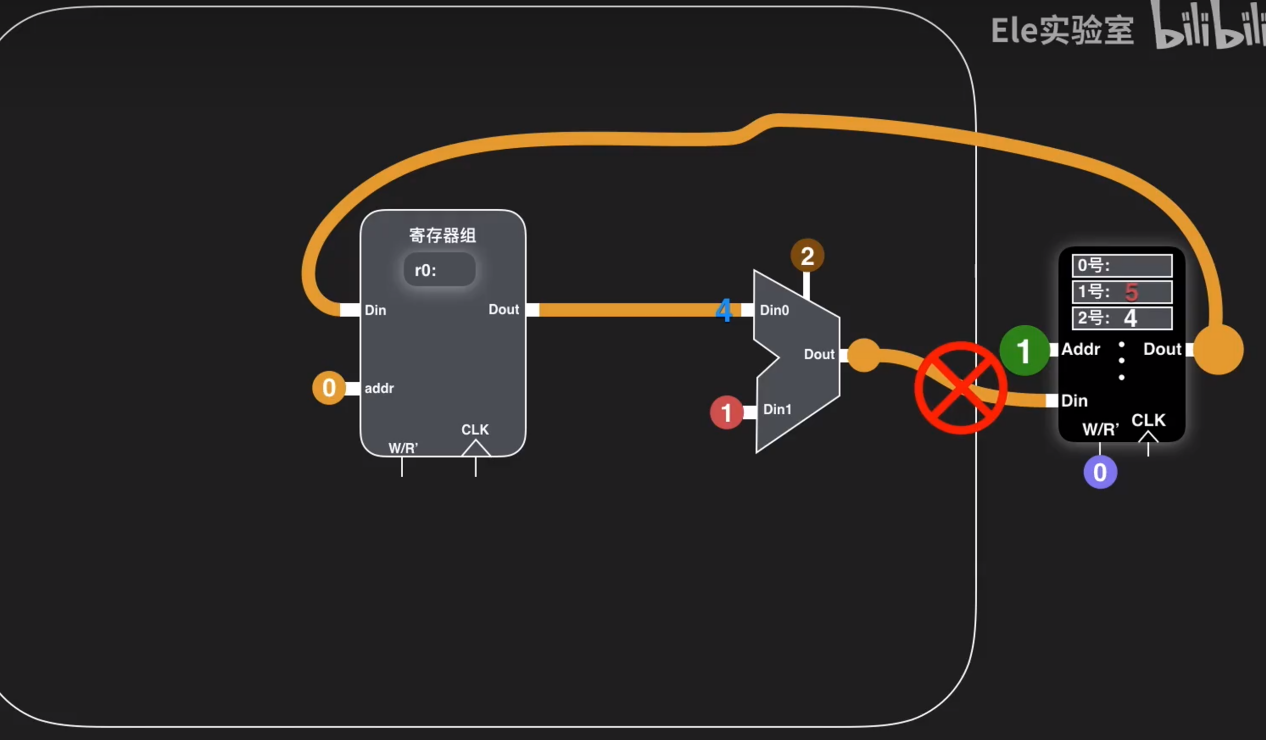

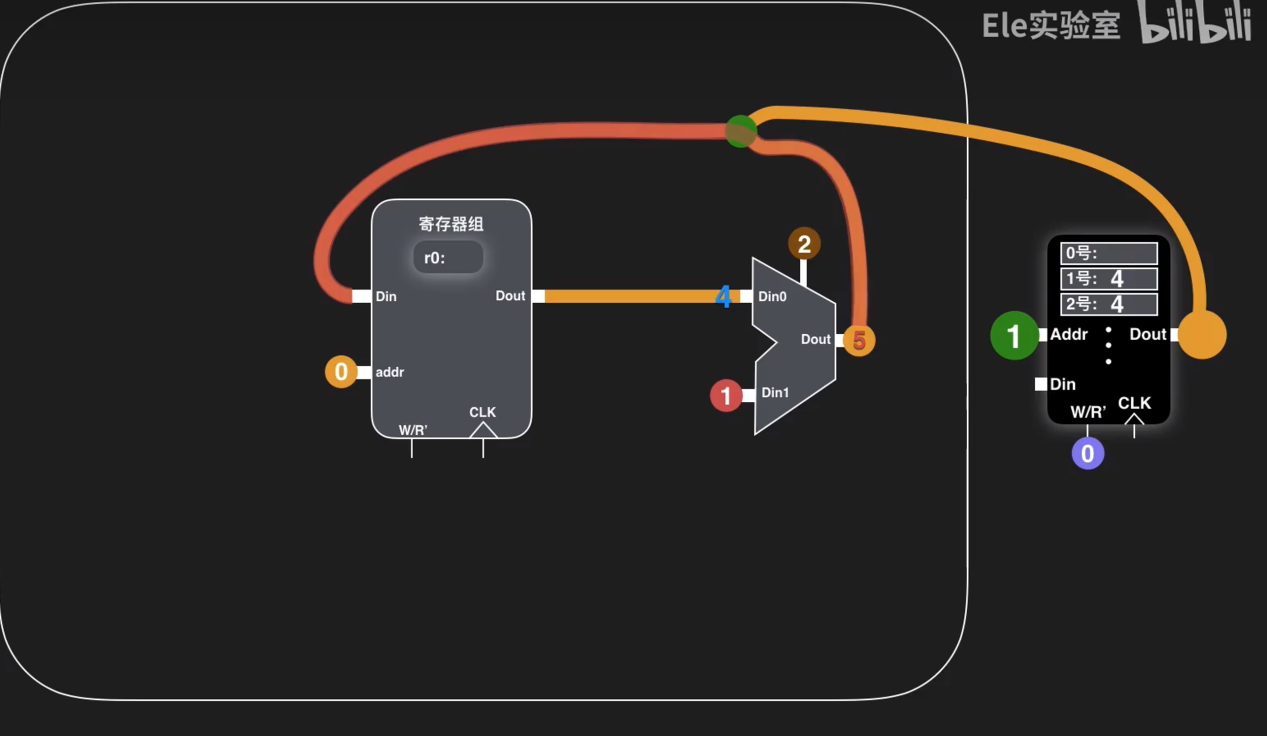

运算结果不能直接送回RAM,CPU与RAM的交互必须经过寄存器组(MIPS架构的要求)

这才是符合MIPS架构的输出方式(but RAM的输出与加法器的输出冲突了)

记得数电中有一个叫数选的东西;

读取RAM时选择信号为1

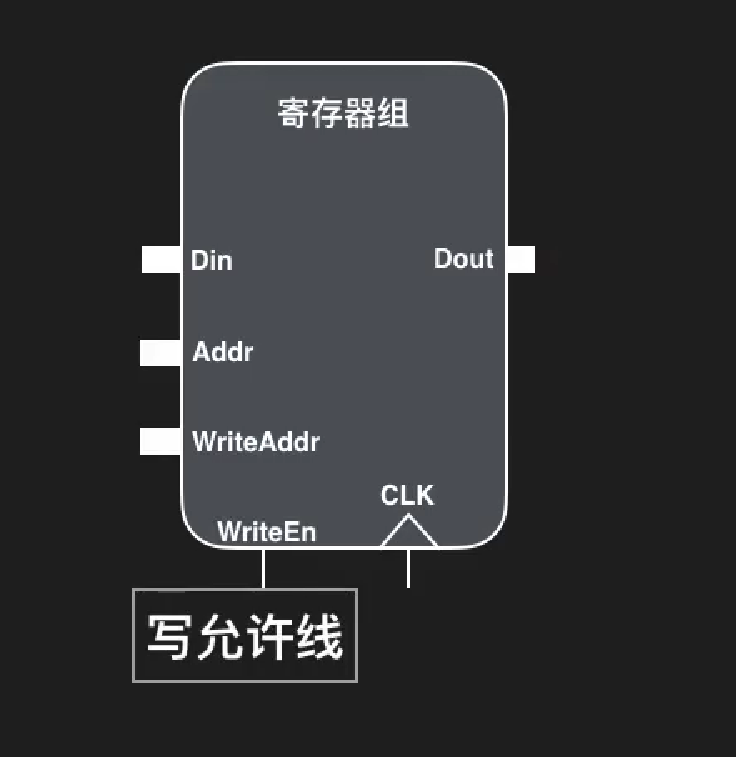

运算器把运算结果传递到寄存器中时 发现地址线在读取RAM时已经被占用 所以读写地址线分开;

所以读写控制线就不需要了改为写允许控制线;

为1时允许写,为0时不允许写(相当于int x=x+1;)

寄存器输出的结果输出到RAM的1号中,但寄存器的读写控制线为0防止其他数据写入寄存器

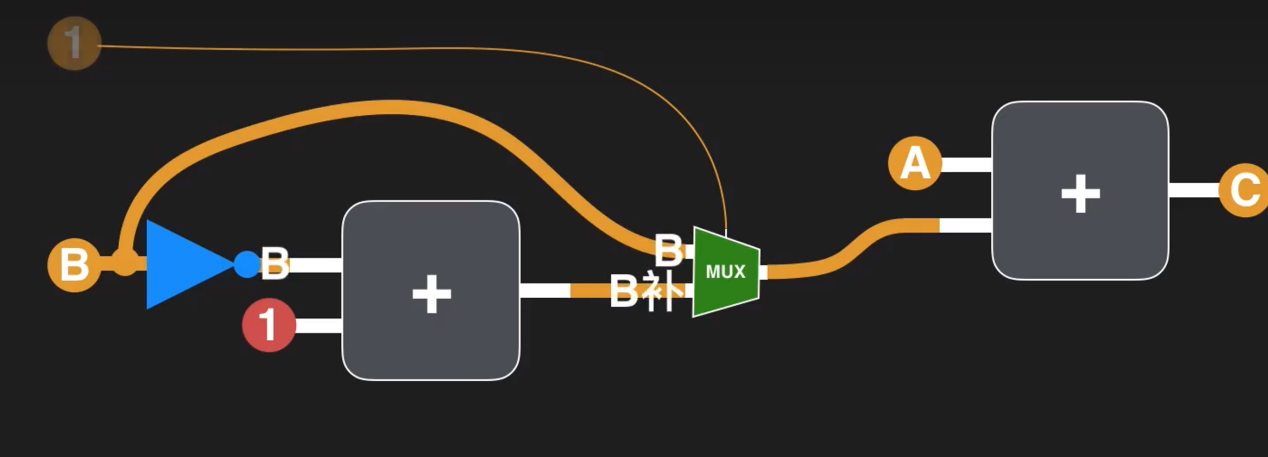

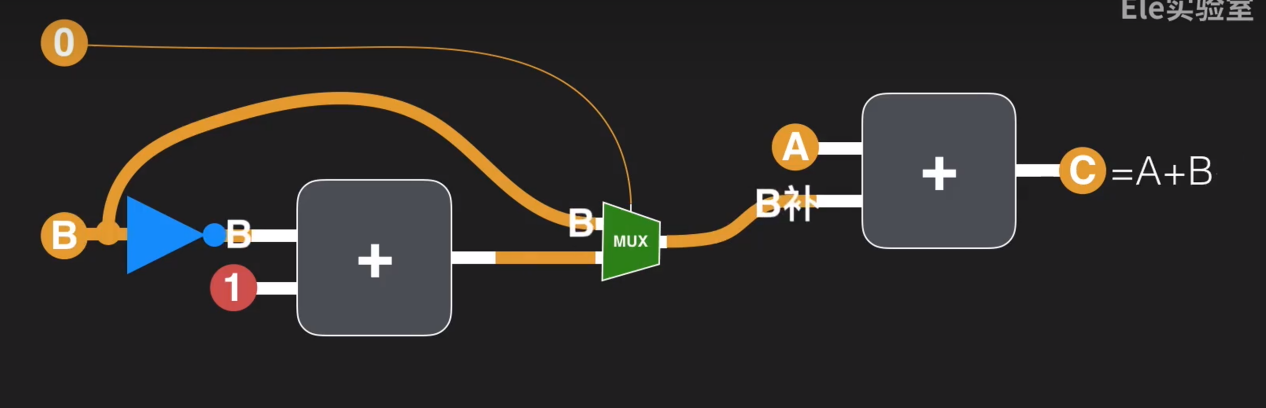

运算器和加法器的电气原理:

多路选择器为1时,输出B的原码值

A+B的运算

=0时,输出 B取反的值与1在全加器下运算结果

A-B的运算(A+B补)

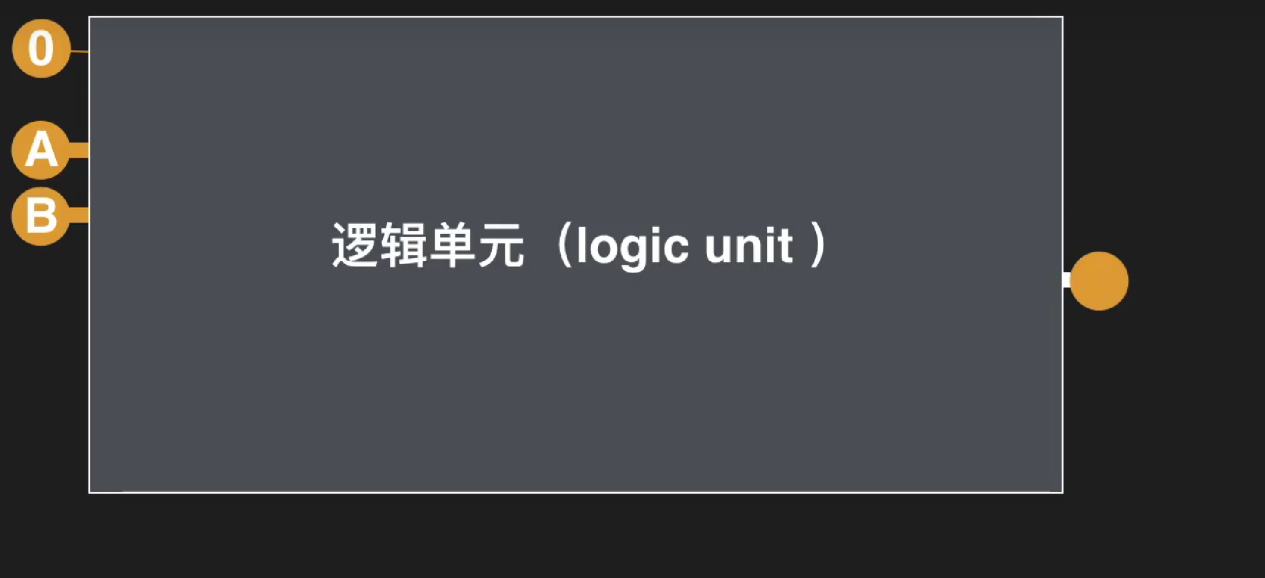

把这个模块封装起来

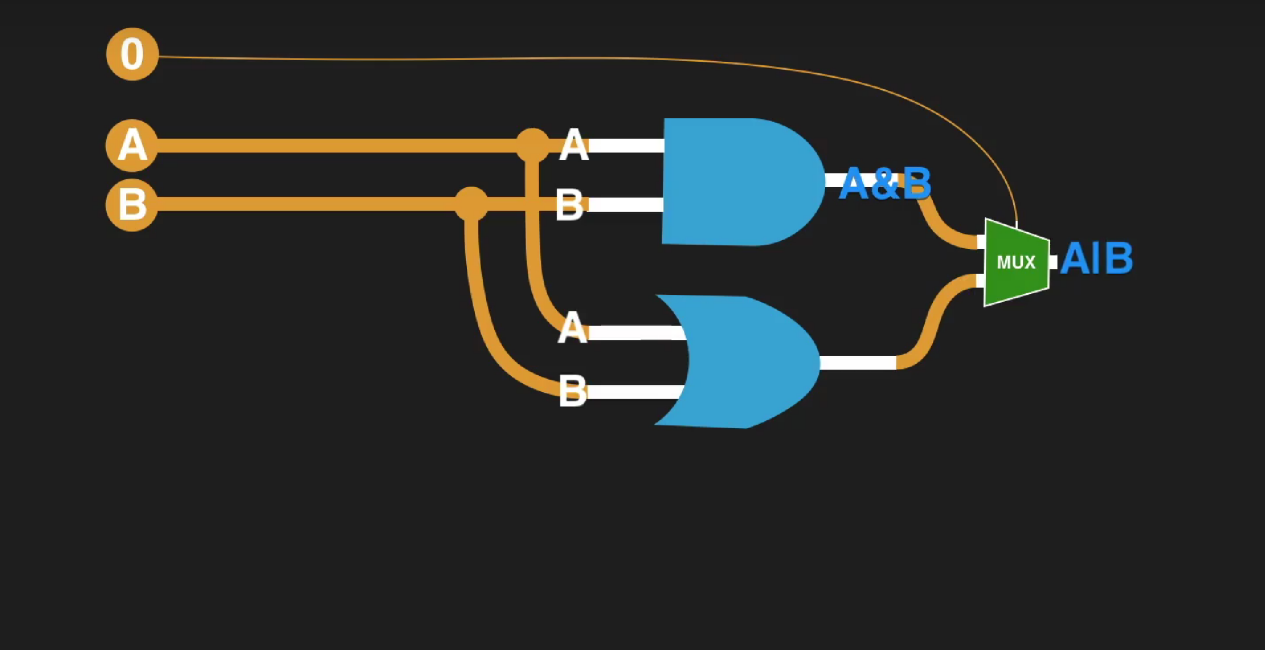

逻辑运算时相似

ALU

寄存器组的电气原理

MUX选择 输出哪个寄存器的值 在这里遵循MIPS架构32位的原则为5位

同样的写入数据通过3-8译码器就可以选择需要输入的寄存器,3-8译码器与一个与门相连接,这样就可以实现写允许控制线

指令集:

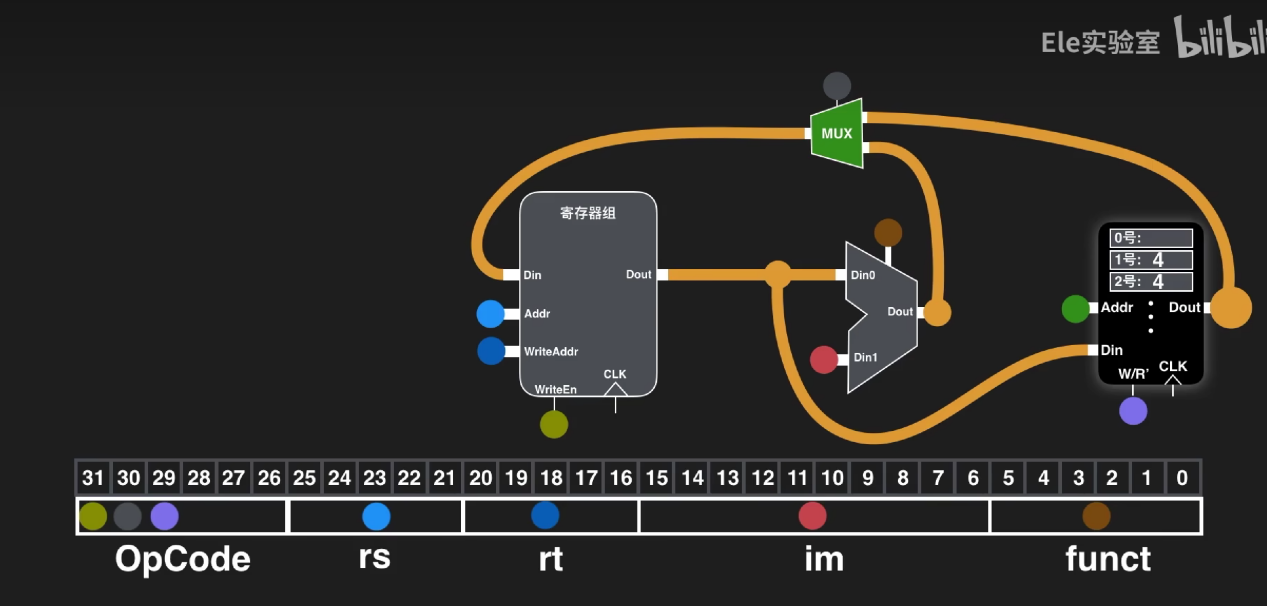

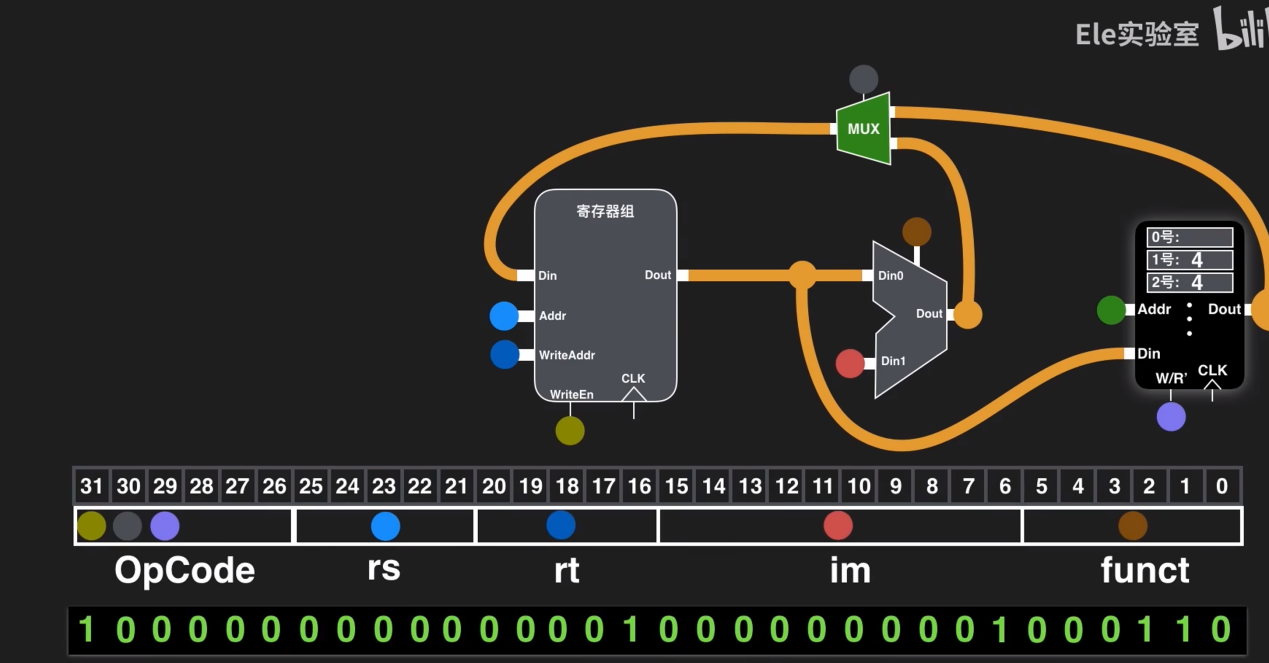

在我们在CPU进行某一运算时,CPU的每一个控制线就会有相应的值,把这些值按一定格式记录下来就形成了指令集(如图展示的是MIPS指令集)

以下内容来自AI

MIPS(Microprocessor without Interlocked Pipelined Stages)指令集是一种采用精简指令集计算(RISC)架构的处理器指令集。MIPS架构最初由斯坦福大学的研究项目发展而来,并于1984年由MIPS计算机公司商业化。MIPS架构以其简单性和规律性而著称,这使得它在计算机架构课程中广受欢迎,因为它在ISA(指令集架构)和实现方面都比较容易理解。

MIPS架构属于RISC(Reduced Instruction Set Computer)架构,与CISC(Complex Instruction Set Computer)架构相比,MIPS架构的指令集更小,指令更简单,这使得它的执行效率更高。MIPS架构的特点是固定长度的32位编码格式,这意味着每条指令都是32位长,这简化了指令的获取和解码过程。

MIPS处理器通常包含以下组件:

-

程序计数器(PC):存储下一条要获取的指令的地址。

-

指令寄存器(IR):保存当前正在解码的指令。

-

寄存器堆:包含32个通用寄存器,用于存储数据和地址。

-

算术逻辑单元(ALU):执行算术和逻辑运算。

-

内存:用于存储程序和数据。

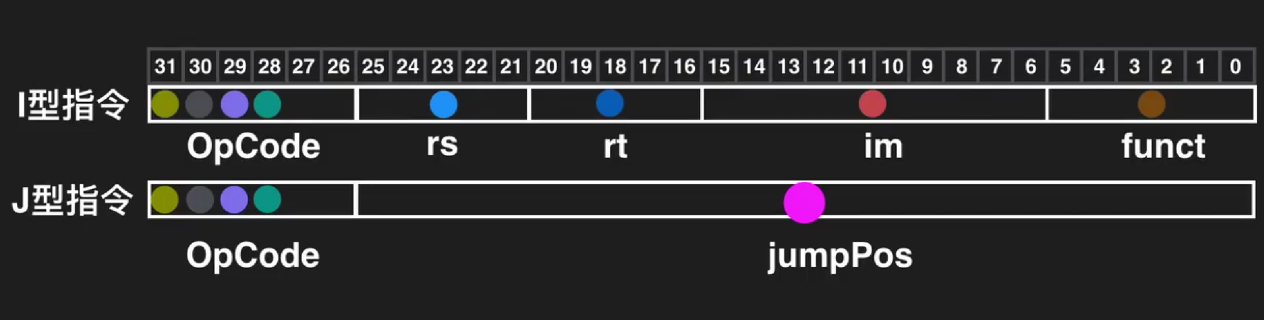

MIPS指令集包括三种基本类型的指令:

-

R类型(寄存器类型):这类指令主要用于寄存器之间的操作,如加减乘除和逻辑运算。

-

I类型(立即数类型):这类指令通常用于涉及立即数的操作,如加载和存储。

-

J类型(跳转类型):这类指令用于实现程序的跳转操作。

MIPS架构的一个关键特点是其加载/存储架构,这意味着除了加载和存储指令外,所有指令都需要寄存器或常量(立即数)操作数。要操作内存中的数据,MIPS程序必须先将内存值加载到寄存器中,然后使用寄存器操作指令处理这些值,最后将这些值存储回内存。

MIPS处理器的执行过程遵循典型的取指-解码-执行周期(FDX)。在这个周期中,处理器从内存中获取指令,解码指令,然后执行指令。解码过程确定了要执行的操作、使用哪些参数以及结果将存储在哪里。执行过程执行操作并确定获取下一条指令的位置。

MIPS架构的实现通常涉及流水线技术,这使得指令的获取、解码、执行、内存访问和写回可以并行进行,从而提高了处理器的性能。流水线技术允许多个指令同时在不同的阶段被处理,从而提高了指令的吞吐量。

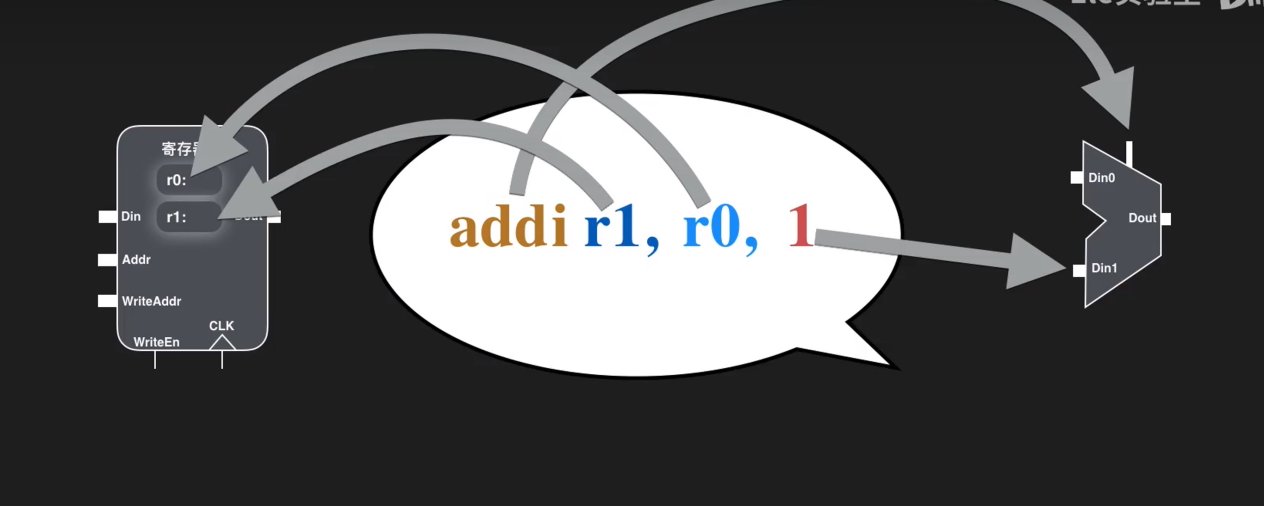

汇编

将人类语言转化为机器语言就是汇编器

在程序运行之初,寄存器在等待RAM的输入,RAM也在等待寄存器的输入,这时需要Din1直接输入一个立即数

这里本质上就是寄存器赋值,r7寄存器的值一直存0;

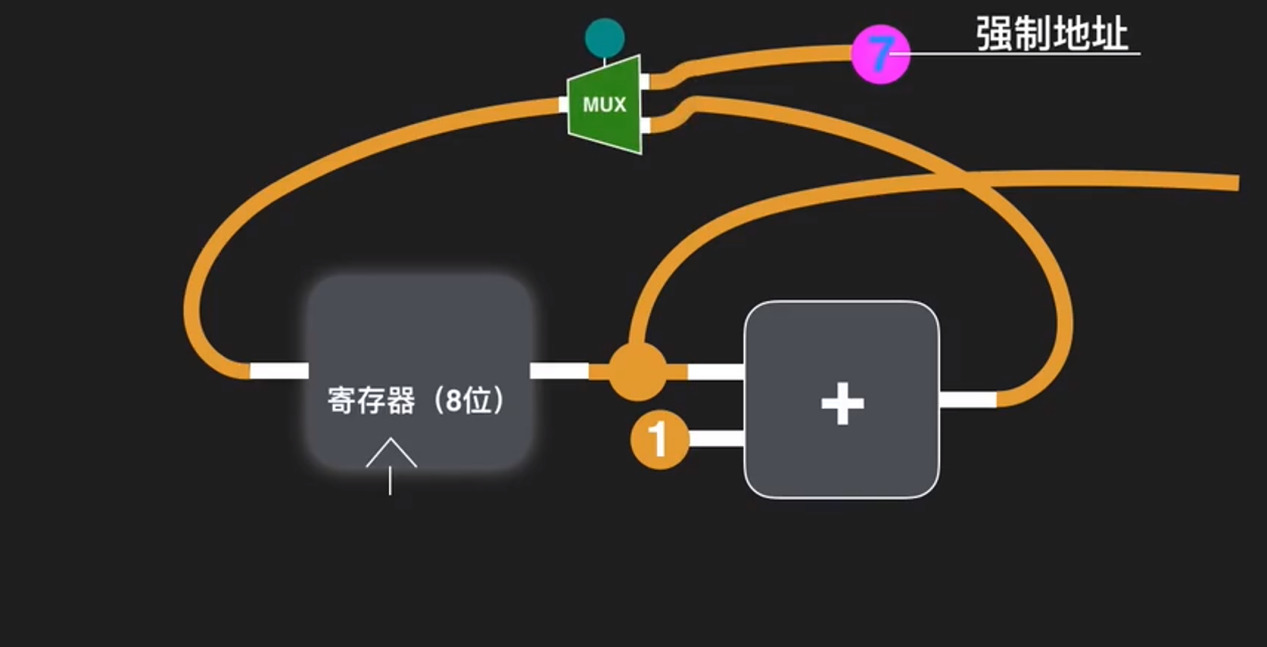

PC计数器:

电气原理:

我们知道指令存在ROM中,目前为止我们需要执行的每台指令需要我们手动输入,这与计算机自动机要求不符合,我们在ROM的地址线中加入一个PC计算器,在每一个时钟信号的边沿,PC实现加1,则自动执行下一条指令 当然这一部分也在CPU中;

目前为止我们的计算机可以自动运行了;

图形化:

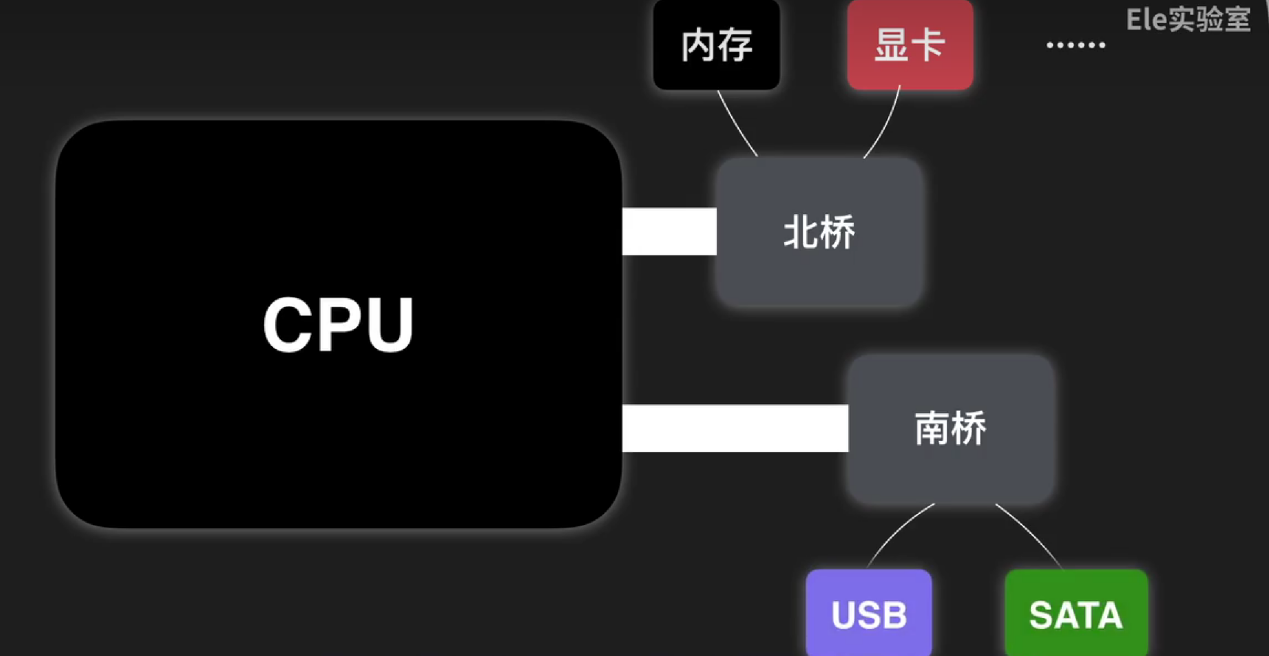

IO线路:

目前北桥一般被集成到CPU中了

例如我们可以把需要输出的数据储存到几个寄存器中,在把它输出到CPU外部上

把指令烧录到ROM中就可以实现输出到显示器

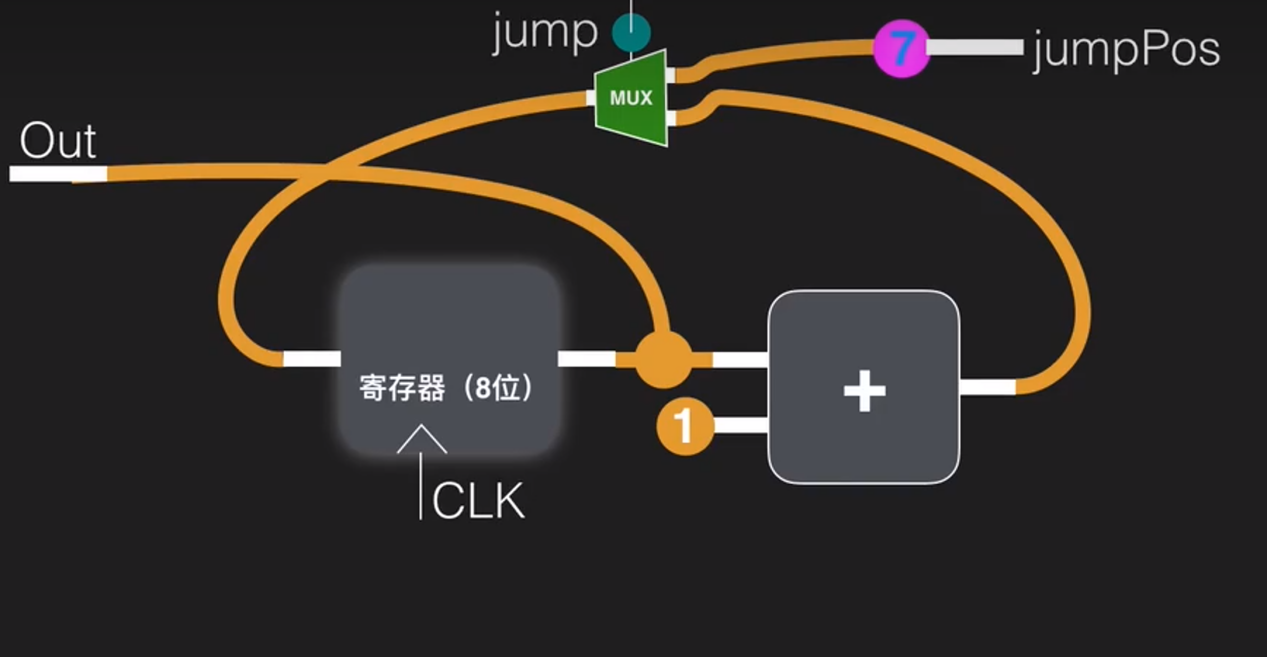

跳转:

比如Jump 7 (不论当前在哪条指令强行到某条指令即PC强行赋值)那么现在来改造PC计数器:

我们的老朋友多路选择器

这里这个的jump指令与RAM,寄存器组无关 MIPS的高6位为操作码,除此之外26位都可以作为地址码;

844

844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?