SD NAND引脚上拉电阻的必要性

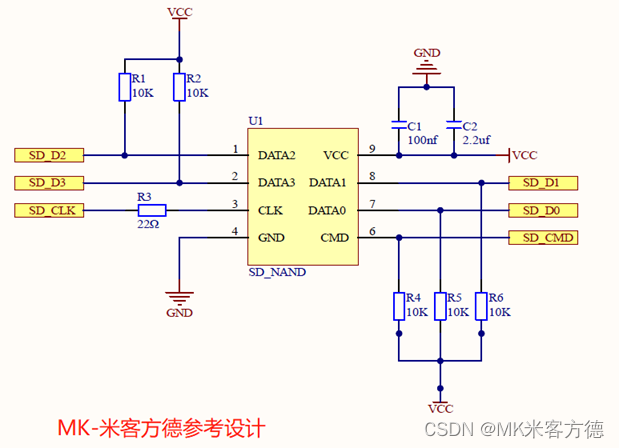

SD NAND参考设计电路

上面的电路设计是"MK-米客方德"的SD NAND芯片的标准参考电路,

电路中上拉电阻是为了保持信号的稳定性,让引脚不至于处在浮空状态而导致电压异常,从而让数据传输出现错误。

经典案例

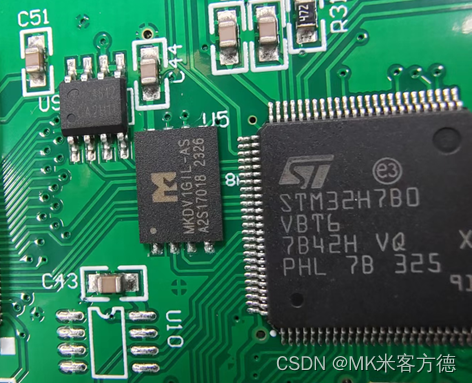

下图是一个主控STM32,应用于运动控制系统的工控机

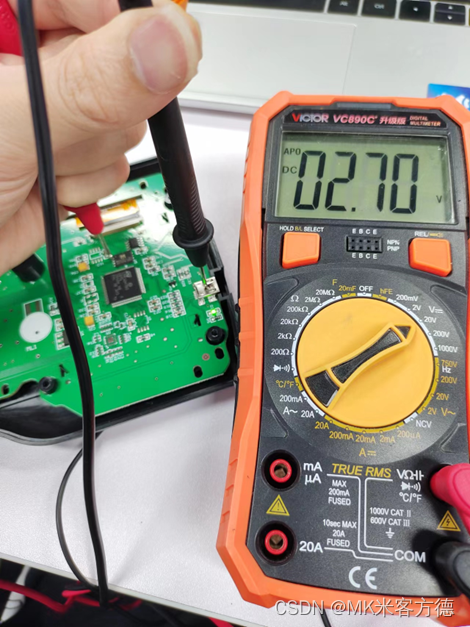

当读取写入的速度比较快时,产品系统会出现卡顿甚至卡死、芯片读取不了等情况;测得IO引脚电压异常。

芯片是3.3V电压的,引脚电压正常应该是3.3V,这个异常电压是引脚没有接上拉电阻导致的。

当产品接上上拉电阻后,产品就已经恢复正常。

注意事项

除了上拉电阻,参考电路的CLK引脚的电阻和VCC引脚的电容2.2uf也是不可缺少;电源和GND之间的电容是为了上电和断电时,芯片能正常工作,电容过大或者过小都会影响芯片的功能。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?