文章目录

9.1 8237A 的组成与工作原理

9.1.1 DMA传送

用 DMA 方式传送数据时,传送过程完全由 DMA 控制器(DMAC)控制。其基本功能:

DMAC能向CPU的HOLD脚发出DMA请求信号。- CPU响应

DMA请求后,DMAC获得总线控制权,由它控制数据的传送,CPU则暂停工作。 - 能提供读/写存储器或I/O设备的各种控制命令。

- 确定数据传输的始址和数据长度(CPU配置的),每传送1个数据便自动修改地址(

+1或-1),数据长度-1。 - 传送完毕,能发出结束

DMA传送的信号。 - CPU在每个非锁定时钟周期结束后,都会检测

HOLD脚上有无DMA请求?若有,便转入DMA传送周期。

8237A 是高性能可编程 DMA 控制器,主要特点:

- 含

4个通道,每通道有64K地址(16位)和字节计数能力(16位)。 - 有

4种传送方式:单字节传送、数据块传送、请求传送、级联传送。 - 每个通道的

DMA请求可被允许或禁止。4个通道的DMA请求有不同优先级,优先级可以是固定的,也可以是循环的。 - 任一通道完成数据传送后,会自动产生过程结束信号

EOP(End of Process,不常用),结束DMA传送;还可从外界输入EOP信号,中止正执行的DMA传送。

8237A 的两种工作状态

1)从态方式

开始 DMA 传送前,8237A 是系统总线的从属设备,由CPU对它进行编程,如指定通道、传送方式和类型、内存单元起始地址、地址是递增还是递减以及要传送的总字节数等等;CPU也可读取 DMAC 的状态。

2)主态方式

当 8237A 取得总线控制权后,它就完全控制了系统,使I/O设备和存储器之间或者存储器与存储器之间进行直接的数据传送。

8237A 芯片的内部结构和外部连接与这两种工作状态密切相关。

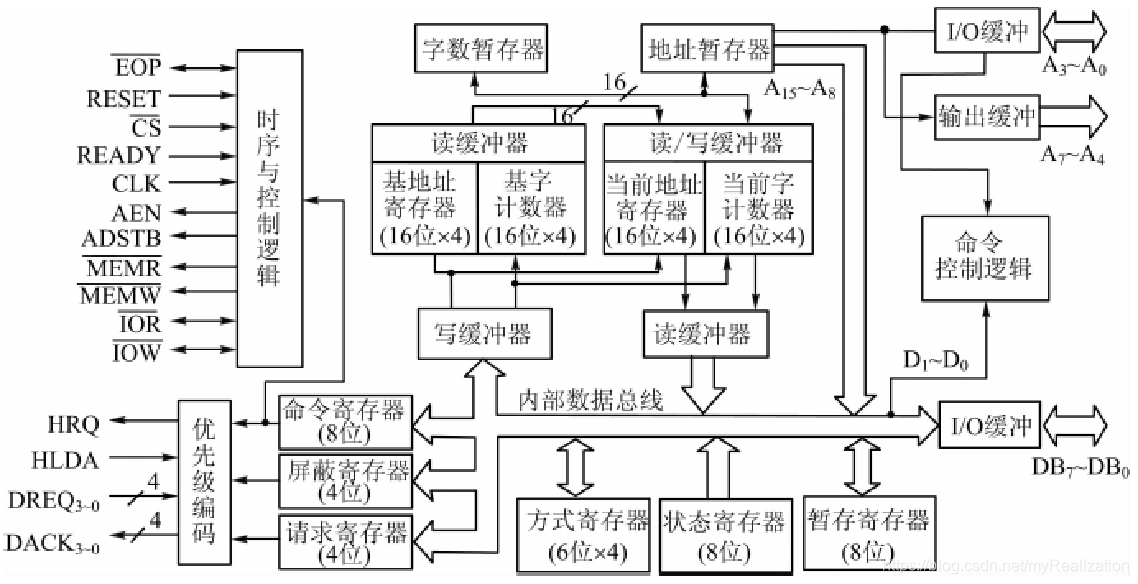

9.1.2 8237A的内部结构

-

时序与控制逻辑

从态时,接收系统时钟、复位、片选和读/写等信号,完成相应控制操作;主态时, 向系统发控制信号。

其中与设备相连的是 IOR ‾ , IOW ‾ \overline {\text{IOR}},\overline {\text{IOW}} IOR,IOW ,其他的要么和CPU相连,要么和系统总线相连。

MEMR ‾ , MEMW ‾ \overline {\text {MEMR}},\overline {\text{MEMW}} MEMR,MEMW 是主态时进行内存读写的命令。 -

优先级编码电路

对同时提出DMA请求HRQ(Hold Request)的多个通道进行排队判优,决定哪个通道优先级最高,然后进行响应HLDA(Hold Acknowledge)。

可选固定或循环优先级。某个优先级高的设备服务时,禁止其它通道请求。 -

数据和地址缓冲器组

8237A的A7~A4(单向输出)、A3~A0(双向:从态时A3-A0输入有4根线,说明占了16个端口地址;主态时:A3-A0、A7-A4、DB7-DB0共16根地址线往内存输出,读或写数据) 为地址线;

DB7~DB0在从态时传输(CPU配置或读取DMA的)数据,主态时传送地址。它们都与三态缓冲器相连,便于接管或释放。 -

命令控制逻辑

从态时接收CPU送来的寄存器选择信号(A3~A0),选择寄存器;主态时译码方式字的D1D0,以确定操作类型。A3~A0与 IOR \text{IOR} IOR 、 IOW \text{IOW} IOW 配合组成各种操作命令。 -

内部寄存器组

每通道有16位基址寄存器、基字计数器、当前地址寄存器、当前字计数器以及6位工作方式寄存器。

片内还有命令寄存器、屏蔽寄存器、请求寄存器、状态寄存器和暂存寄存器。

不可编程的字数暂存器和地址暂存器。

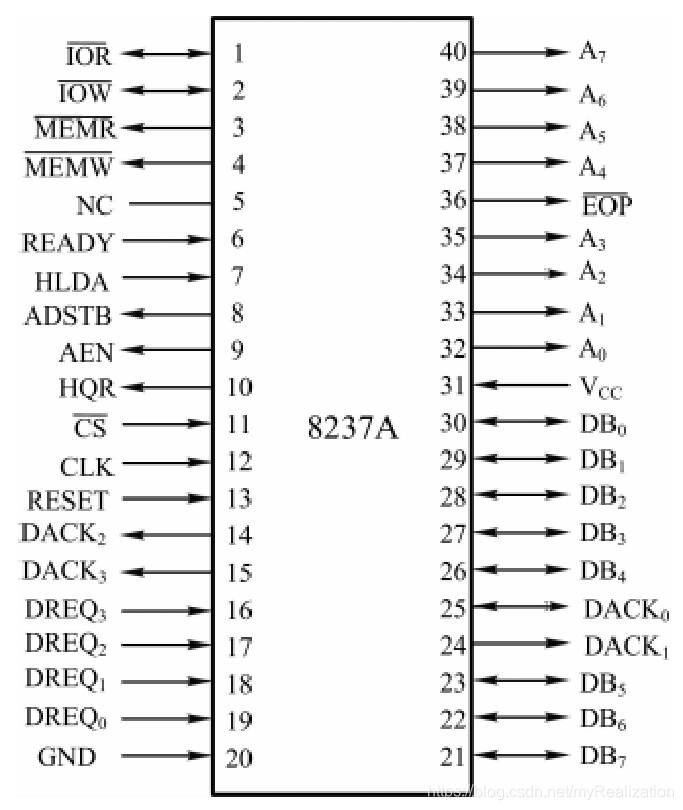

9.1.3 8237A的引脚功能

8237A 为 40 引脚 DIP 封装, 引脚排列:

CLK时钟信号,输入

8237A时钟频率3MHz,8237A-5为5MHz。- CS ‾ \overline \text{CS} CS 片选信号,输入,低电平有效。

从态方式下选中8237A,接受CPU对它的编程等。 READY准备好,输入,高电平有效

慢速I/O设备或存储器参与DMA传送时,可使READY变低,让8237A在DMA周期中插入等待周期TW;当它们准备就绪时READY变高。A3~A0低4位地址线

从态为输入,寻址8237A内部寄存器,实现编程;主态时输出要访问内存的低4位地址。A7-A4高4位地址线

始终是输出或浮空,主态时输出4位地址信息A7-A4。DB7-DB08位数据线,与系统数据总线相连。- 从态时,CPU经过数据线读取各有关寄存器内容,并对各寄存器编程。

- 主态时,由它们输出高

8位地址A15-A8,并由ADSTB信号将它们锁存到外部的高8位地址寄存器中,与A7-A0输出的低8位地址构成16位地址。 - 存储器-存储器传送方式下,源存储器读出的数据,经它们送暂存寄存器,暂存器中数据再经它们写到目的存储单元中。

AEN地址允许信号,输出,高电平有效

送出锁存的高8位地址,与芯片输出的低8位地址一起构成16位内存偏址。同时使连到CPU的地址锁存器无效,保证地址线上的信号来自DMAC。ADSTB地址选通信号,输出,高电平有效

选通外部地址锁存器,将DB7~DB0上的高8位地址送到外部的地址锁存器。- IOR ‾ \overline {\text{IOR}} IOR

I/O读信号,双向。

从态时,控制CPU读取8237A内部寄存器。

主态时,与 MEMW

本文深入探讨了8237A DMA控制器的组成、工作原理、内部结构及引脚功能,详细讲解了其时序、编程方法与应用实例,特别关注于IBM-PC微机中的DMA系统配置与初始化。

本文深入探讨了8237A DMA控制器的组成、工作原理、内部结构及引脚功能,详细讲解了其时序、编程方法与应用实例,特别关注于IBM-PC微机中的DMA系统配置与初始化。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

647

647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?